基于55 nm CMOS 工艺的可变增益放大器

2020-06-30安文星佟玲刘亚轩张娜

安文星,佟玲,刘亚轩,张娜

(1.天津大学 微电子学院,天津 300072;2.中国海洋大学 信息科学与工程学院,山东 青岛 266100)

近年来,5G 通信对数据传输速率的高要求,使得无线通信系统的信道带宽成为研究的重要指标,而可变增益放大器(Variable Gain Amplifier,VGA)作为影响收发机芯片信道带宽的重要模块,其带宽特性直接影响数据传输的快慢.在接收机中,VGA 能对不同幅度的输入信号产生不同的增益,从而增大接收机的动态范围[1-2],为了满足5G 通信的数据吞吐量,应用于5G 中VGA 的3-dB 带宽必须在吉赫兹以上[3].为了保证通信系统拥有稳定的建立时间,VGA 必须具有增益线性变化特性.因此,具有增益线性变化特性的宽带VGA 得到了广泛研究.

VGA 主要分为开环与闭环两种,由于难以实现高增益、宽带宽的运算放大器,闭环VGA 的带宽往往受到极大限制,仅为几十兆赫兹[4].现有的基于锗硅双极型互补金属氧化物半导体(SiGe Bipolar Complementary Metal Oxide Semiconductor,SiGe BiCMOS)工艺和互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺的宽带中频或基带VGA 多为开环结构[5-10],按控制方式又可分为数字控制与模拟控制两种.在具有精确增益线性特性的宽带VGA 中,数字控制的VGA 占主导地位[11-12],但其增益变化为离散型,严重限制了其应用领域;模拟控制的VGA 增益虽然能够连续变化,但需要几级低增益、宽带宽的可变增益单元级联,这就会带来功耗、成本增加、整体VGA 线性度下降等问题.例如文献[7]中提出的采用65 nm CMOS 工艺实现的一种模拟电流控制的VGA,带宽达到4 GHz,但其功耗超过25 mW,功耗过高,不利于系统集成,在应用上具有一定局限性.在利于系统集成的CMOS工艺中,实现增益线性变化具有挑战性,文献[9]虽然在低功耗下实现了宽带特性,但增益变化为非线性,不适用于需要稳定建立时间的系统中.

本文采用55 nm CMOS 工艺实现了一种模拟电压控制,增益具有线性的宽带可变增益放大器.在不显著增加功耗的基础上,实现了对数增益随控制电压连续、线性、大范围的变化,且3-dB 带宽对应的频率达到1.89 GHz.

1 电路设计

1.1 可变增益单元的设计

考虑到接收机一定的动态范围和带宽需求,本设计采用一种改进型的Cherry-Hooper 放大器,这种带有反馈结构的电路可以通过将输出极点移向更高的频率来扩大增益带宽,并且不会使增益显著降低.

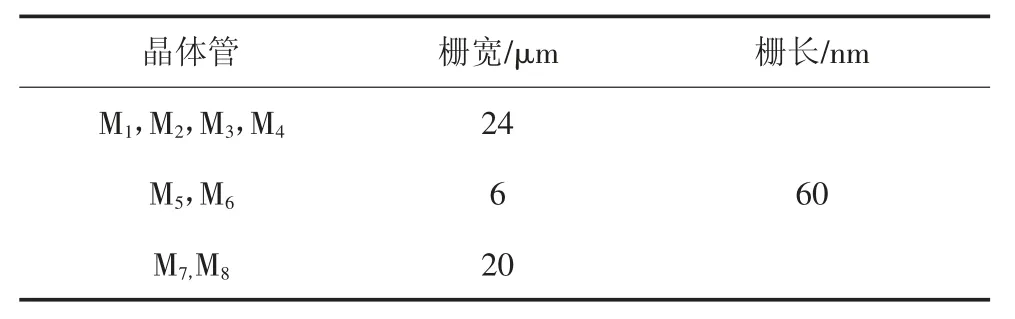

传统的Cherry-Hooper 型放大器如图1(a)所示,这种结构有两点不足之处:首先,为使所有晶体管在饱和区域工作,大偏置电压会造成高功耗;其次,RD限制了放大器的最小增益,也就限制了放大器的可调谐范围.因此,本文对传统的Cherry-Hooper放大器进行了改进,使其在不增加功耗的情况下,具有更宽的增益调谐范围,如图1(b)所示.其中可用工作在三极管区的PMOS 管M5、M6来代替反馈电阻Rf,Cf为M5、M6的等效寄生电容.利用施加在M5、M6栅极上电压VC的变化来实现可调电阻的功能[13].所有CMOS 晶体管都采用低阈值电压模型来缓解功耗问题.外接控制电压的PMOS 晶体管M7、M8分别与R3、R4并联,以降低最小增益,从而增加整体增益调谐范围.此外,NMOS 管M1、M2分别由偏置电阻R1、R2提供直流电流.最终优化得到的各晶体管的参数如表1 所示.

图1 可变增益单元的设计Fig.1 Design of variable gain cell

1.1.1 宽带的实现

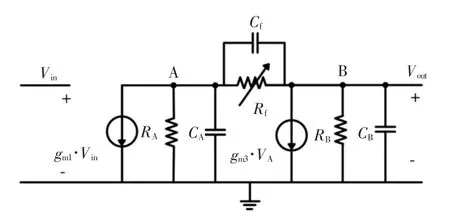

为减小分析复杂度,图2 给出了可变增益放大器半边小信号模型.其中Gm 级和TI 级的直流增益可分别由公式(1)和(2)进行定义.

表1 可变增益放大单元中晶体管的栅宽和栅长值Tab.1 Gate width and gate length values of transistors in the variable gain amplifier cell

图2 可变增益单元半边小信号模型Fig.2 Half small-signal model of variable gain cell

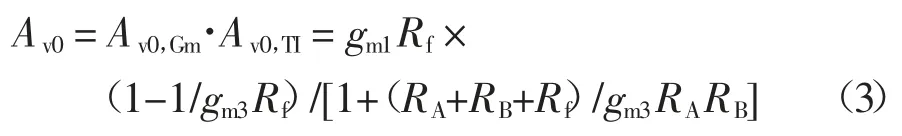

改进的Cherry-Hooper 放大器增益单元可视为跨导Gm 级和跨阻抗TI 级的级联,则增益单元的直流增益Av0为:

式中:gm1和gm3分别为M1和M3的跨导;RA和RB为主节点A 和B 处的输出电阻;反馈电阻Rf为M5、M6的等效电阻.该增益单元的传输函数Av(s)为:

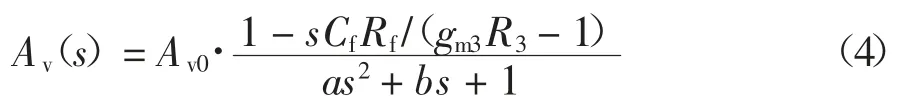

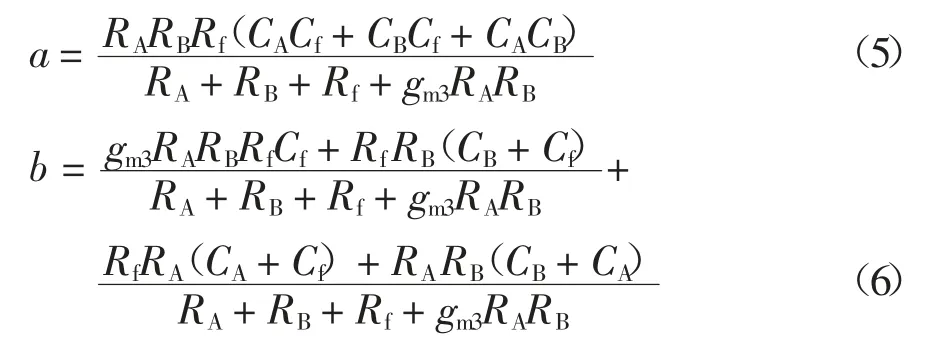

式中:Cf为M5、M6的等效寄生电容.a 和b 的表达式分别为:

式中:CA为节点A 处的总寄生电容;CB为输出节点B 处的总负载电容.通常忽略Cf的值,电路中晶体管M7可增大RA和RB的值,使RA>>Rf和RB>>Rf,则节点A 和节点B 处的极点为gm3/(CA+gm3RfCf)和gm3/(CB+gm3RfCf),进一步化简得gm3/CA和gm3/CB.

可以发现除了寄生电容CA、CB,该可变增益单元的带宽只由gm3决定,与gm1无关,这种设计的优点在于某个增益水平下,可以通过调节gm3来扩展带宽.由于差分电路的对称性,另一半电路中节点C 和D同理可得与上述节点A 和B 相同的结论,即可通过调节与gm3相对应的gm4来扩展带宽.

在直流偏置一定的条件下,改变晶体管M3、M4的栅宽和栅长可以改变其跨导值.图3 给出不同栅宽M3、M4的可变增益放大器频率特性.可以看出栅宽过大时寄生电容也不断增大,跨导gm不再起主要作用,可变增益单元通带内增益出现纹波.因此根据实际需求选择M3和M4的栅宽为24 μm.从整体来看,基于这种方式改进的Cherry-Hooper 型放大器能够实现更宽的带宽.

图3 不同栅宽M3、M4 的可变增益放大器频率特性Fig.3 Frequency responses of the variable gain amplifier with different gate widths of M3,M4

1.1.2 增益线性的实现

为了实现恒定的环路稳定时间和宽范围增益调节,VGA 要求具有指数增益特性,从而可实现增益线性变化.使用具有本征指数特性的双极型晶体管(Bipolar Junction Transistor,BJT)器件或异质结双极型晶体管(Heterojunction Bipolar Transistor,HBT)可较为轻松地实现可变增益放大器的指数增益特性.而在MOS 管中,由于漏源电流与栅源电压的平方律关系,难以实现指数增益特性.考虑到功耗问题,本文利用可调谐MOS 管工作在线性区的特点实现增益线性变化.

Cherry-Hooper 型放大器单元的直流增益Av0可简化为Av0≈gm1Rf.因此,Rf与Av0具有线性关系,即可变电阻Rf具有指数特性时,便可实现增益线性变化.

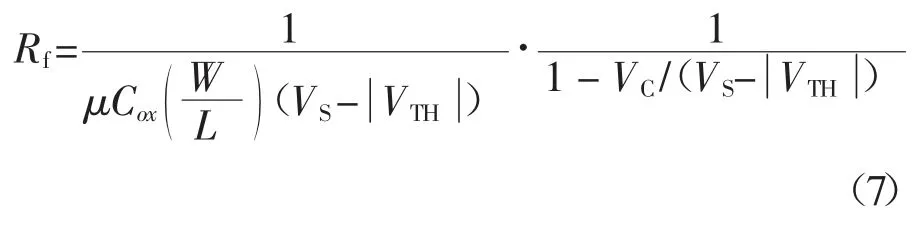

如图1(b)所示,在改进型Cherry-Hooper 放大器电路中,Rf是由可调谐PMOS 管M5、M6实现的,当PMOS 管工作在线性区时,可以得到表达式(7),其中VC和VS分别为栅极电压和源极电压.

根据泰勒展开公式,当允许一定误差存在时,ex≈1/(1-x),,通常在设计中VC的取值为0~电源电压,VS在本设计中为1.1 V,为满足条件1,VC取值要小于0.691 V,此时式(7)可写成:

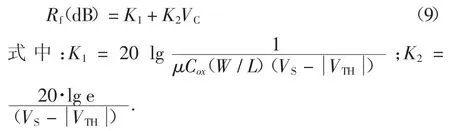

将式(8)换算成对数形式可得:

显然,K1和K2是常数,Rf相对于栅极电压VC成增益线性的关系,即增益Av0与栅极电压VC成增益线性关系.

通过以上推导可以得出,只要调节作为可调电阻Rf的可调谐PMOS 管的参数和工作区,就能使电路的对数增益随着控制电压VC呈线性变化.

1.2 整体VGA 系统与其他关键模块的设计

1.2.1 整体VGA 架构

图4 为本文提出的VGA 系统框图.本文采用的VGA 系统为级联结构,能提供足够的增益来放大接收到的较弱信号.设每个可变增益单元的3-dB 带宽为BC,增益为AC,级联系统的3-dB 带宽为Btot,增益为Atot,则有关系式(10)和(11),其中n 代表级联的个数.为达到高速通信的目的,整体VGA 需满足带宽大于1 GHz 的设计目标,因此在权衡n 与总噪声系数之间的矛盾之后,选择n=3.

图4 所提出的VGA 系统框图Fig.4 Overall block diagram of proposed VGA

整个VGA 的增益变化由控制电压VC决定,三级VGA 单元由相同的改进型Cherry-Hooper 放大器组成;由具有较低截止频率的高通滤波器构成的前馈电路有效消除了直流偏移.为了在实际环境中匹配50 Ω 的阻抗,在电路输入和输出端添加了缓冲器,能够有效地进行隔离并起到阻抗匹配的作用.

1.2.2 直流偏移消除电路

直流失调是设计高增益放大器时必须考虑的问题,即使一个很小的输入直流失调电压,经过多级放大后可能使输出饱和,导致VGA 输出为恒定电平.实际中,一般采取电容耦合或直流失调消除电路来降低直流失调电压.其中电容耦合是在前馈路径中每级放大器之间使用大尺寸的电容和电阻,来避免损失信号通路中的低频分量,这种方式往往见于低频应用.典型的直流失调消除电路是通过带有RC低通滤波器的单个反馈放大器提取输出直流失调电压,将其部分反馈到输入端,逐步在输入端校正直流失调电压[4,8-10],加入反馈放大器后往往会引入额外功耗,不利于整体设计.

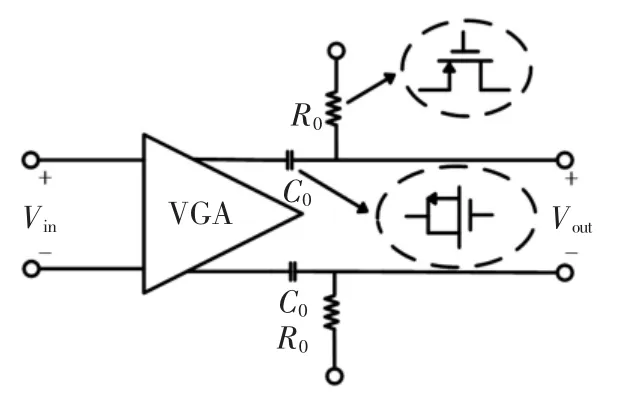

图5 为前馈直流失调消除电路,利用晶体管代替高通滤波器中的大电阻R0和大电容C0,在降低电路复杂度的同时减小了芯片面积,并使得该高通滤波器的截止频率大大降低,从而降低了该可变增益放大器的下截止频率,可以有效提升数据传输速率,降低误码率.

图5 前馈直流失调消除电路Fig.5 Feed-forward DC offset cancellation circuit

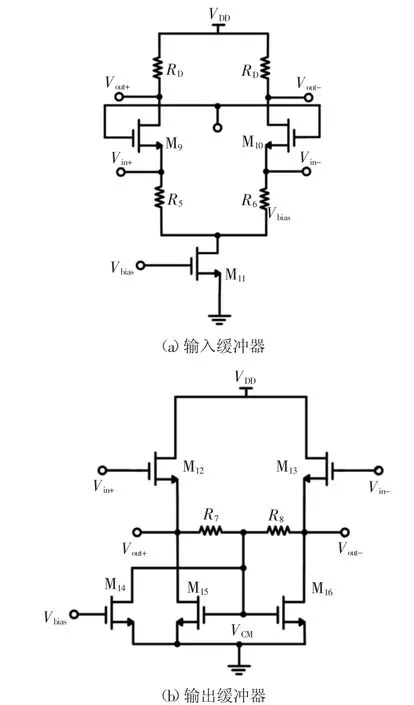

1.2.3 输入缓冲器与输出缓冲器

为方便在实际环境中进行测试,VGA 系统在输入输出端分别使用缓冲器来获得良好的匹配,便于驱动低阻抗负载.输入与输出缓冲器的原理图如图6 所示.输入缓冲器采用基本的共栅极放大结构[9],其输入阻抗为R5/(1+gm9R5),gm9R5的值很小,可忽略不计;输出缓冲器采用具有共模反馈电路的射极跟随器的结构[14],其输出阻抗为Zout=(1/gm15)‖(1/gm16);M15、M16影响着VGA 的输出匹配.缓冲器电路中关键器件的参数见表2.

图6 缓冲器电路图Fig.6 Buffer circuit

表2 缓冲器电路中晶体管的栅宽和栅长值Tab.2 Gate width and gate length values of transistors in the buffer circuit

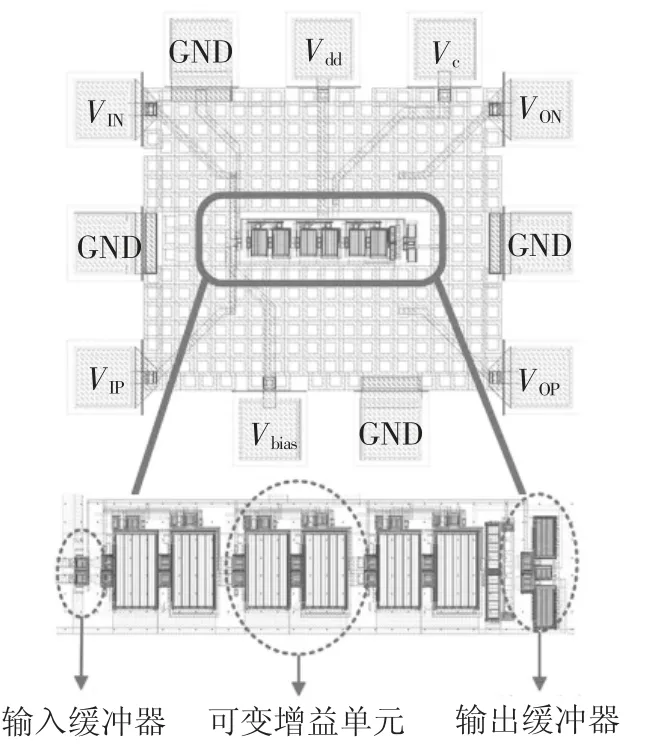

2 结果与分析

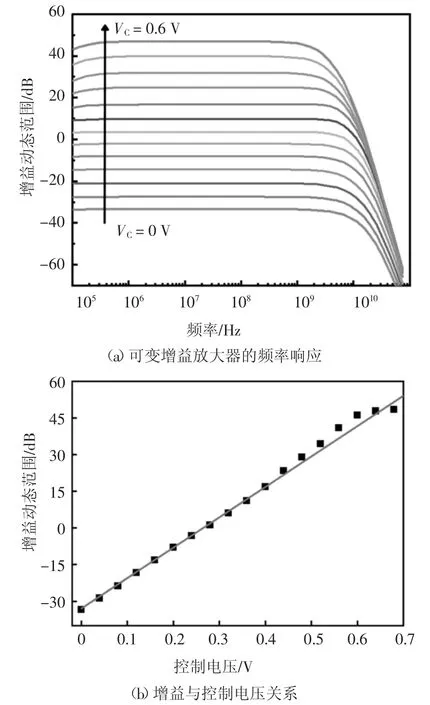

本文设计的VGA 版图如图7 所示,由于芯片设计时未使用任何电感,故芯片面积小,制作成本低.芯片面积为0.006 mm2(芯片核心区域尺寸,不包括焊盘),直流功耗为19.68 mW.使用仿真软件基于Global Foundries 55 nm CMOS 工艺模型对该宽带VGA 进行版图后仿真.图8(a)给出了该VGA 的对数增益在不同频率上的响应结果.该放大器3-dB 带宽为1.89 GHz(0.000 12~1.9 GHz),带内平坦度极佳.

图7 可变增益放大器的版图Fig.7 Layout of the variable gain amplifier

该VGA 的对数增益随控制电压变化结果如图8(b)所示,当控制电压VC为0~0.6 V 时,电路的对数增益与控制电压VC呈现相当好的线性关系,拟合度较高,增益线性变化的动态范围为-33.4~46.9 dB,增益实现了最大范围的线性变化.

图8 可变增益放大器的性能Fig.8 Performance of the variable gain amplifier

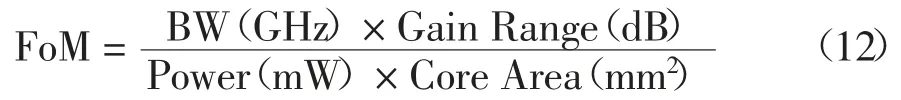

表3 为本文中VGA 的指标与已发表的同类采用CMOS 工艺的可变增益放大器的性能比较.本文所提出的结构实现1.89 GHz(0.000 12~1.9 GHz)的3-dB 带宽,并具有高达80.3 dB(-33.4~46.9 dB)的增益线性变化的增益.通常广泛使用的综合评价VGA性能的FoM 公式如(12)所示,可突出设计在带宽BW、动态范围Gain Range、功耗Power、面积Core Area 等方面的优越性.文献[9]的FoM 虽高于本文中的VGA,其增益却不具备dB 线性的特征,相较而言本设计可直接应用于自动增益控制系统中,在实际应用中更具有优势.

表3 可变增益放大器性能总结与对比Tab.3 Summary and comparison of the variable gain amplifier performance

3 结论

本文设计了一种CMOS 宽带可变增益放大器,该放大器采用三级级联结构,增益单元基于改进的Cherry-Hooper 放大器,可增大带宽,通过在放大管输出的漏极添加可调谐的PMOS 晶体管代替反馈电阻,同时保证了更大的增益调谐范围.此外,利用该可调谐晶体管工作在亚阈值区的特征,在整个动态变化范围内实现出色的dB 线性.最后,利用直流失调消除技术优化了电路性能.VGA 的增益范围为-33.4~46.9 dB,具有精确的dB 线性特性,3-dB 带宽为1.89 GHz(0.000 12~1.9 GHz),满足了5G 通信系统的要求,同时VGA 电路仅占用0.006 mm2面积,1.2 V 电源仅消耗16.4 mA 电流,在VGA 广泛适用的FoM 值为1 292,高于目前同类设计,实现了芯片小尺寸和低功耗,适用于5G 宽带通信系统中.