基于90 nm SOI CMOS 工艺的24 GHz 信号发生器

2020-06-30夏庆贞李东泽常虎东孙兵刘洪刚

夏庆贞,李东泽,常虎东,孙兵,刘洪刚†

(1.中国科学院微电子研究所 高频高压器件与电路研发中心,北京 100029;2.中国科学院大学,北京 100029)

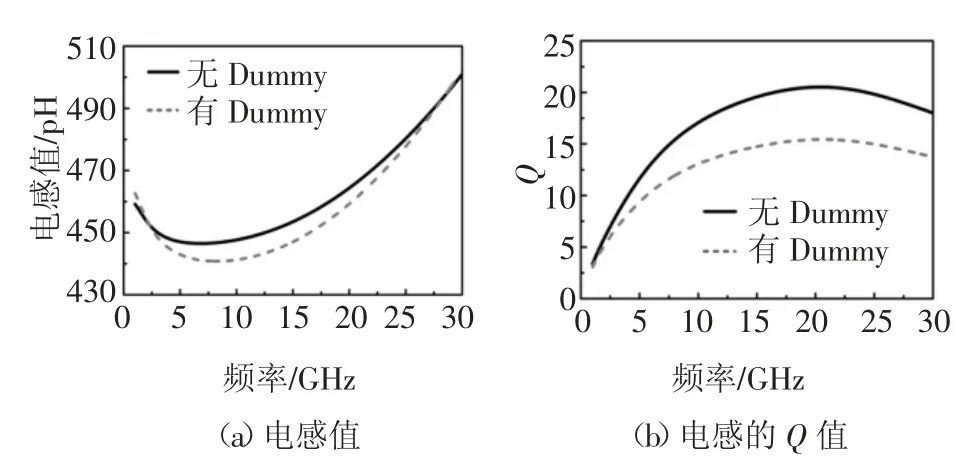

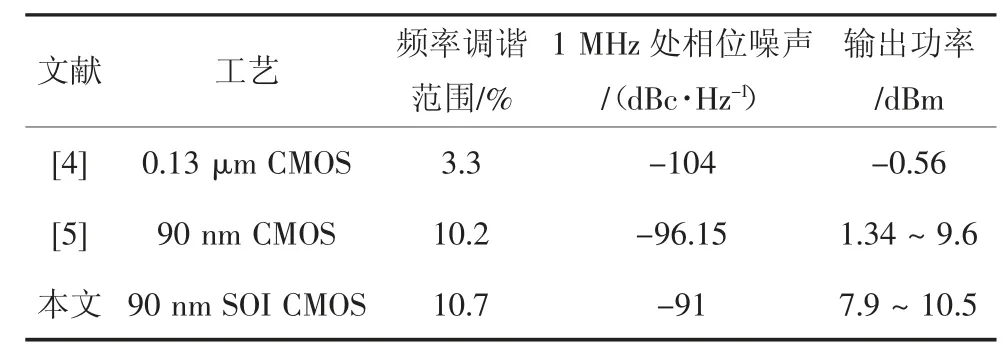

信号发生器是微波与毫米波雷达系统中的重要部件[1].近几年,随着微波毫米波雷达传感器应用需求的增长,低成本与高性能雷达收发芯片的设计与实现逐渐成为研究热点.随着半导体工艺技术的发展,场效应晶体管的特征尺寸不断缩小,器件的截止频率不断提高,基于CMOS 工艺的单片微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)为高集成度射频芯片的实现提拱了解决方案[2-3].Gitae等人[4]采用0.13 μm CMOS 工艺设计了一款24 GHz发射芯片,输出功率为-0.56 dBm.Tan 等人[5]采用90 nm CMOS 工艺设计24 GHz 发射芯片时,在螺旋电感的底部加入接地屏蔽层来抑制衬底串扰,电感的品质因子(Quality Factor,Q)为14.2,输出功率为1.34~9.6 dBm.传统Bulk Si CMOS 工艺衬底的电阻率较低(大概10 Ω·cm),衬底损耗比较严重,难以设计出高Q 的无源器件.与相同技术节点的Bulk Si CMOS 工艺相比,SOI CMOS 工艺具有更高的截止频率、更低的衬底损耗和衬底串扰、良好的温度稳定性.因此,SOI CMOS 工艺非常适合应用于雷达收发芯片领域.2017年,Shopov 等人[6]采用45 nm SOI CMOS 工艺实现了一款60 GHz 低功耗雷达收发芯片,输出功率为-7 dBm,可用于高精度距离探测和速度探测.

本文基于90 nm SOI CMOS 工艺,通过设计一种无输出阻抗匹配网络Stacked-FET 功率放大器(Power Amplifier,PA),提高输出功率.通过底层空置Dummy 金属的方法改善阻抗匹配网络和谐振网络中螺旋电感的Q 值,减小无源器件的损耗,实现一款具有高输出功率的24 GHz 信号发生器电路.

1 电路分析与设计

1.1 24 GHz 信号发生器的电路结构

在24 GHz 信号发射系统中,通常由一个压控振荡器(Voltage Controlled Oscillator,VCO)产生基频振荡信号,并通过PA 将信号放大到需要的功率水平.

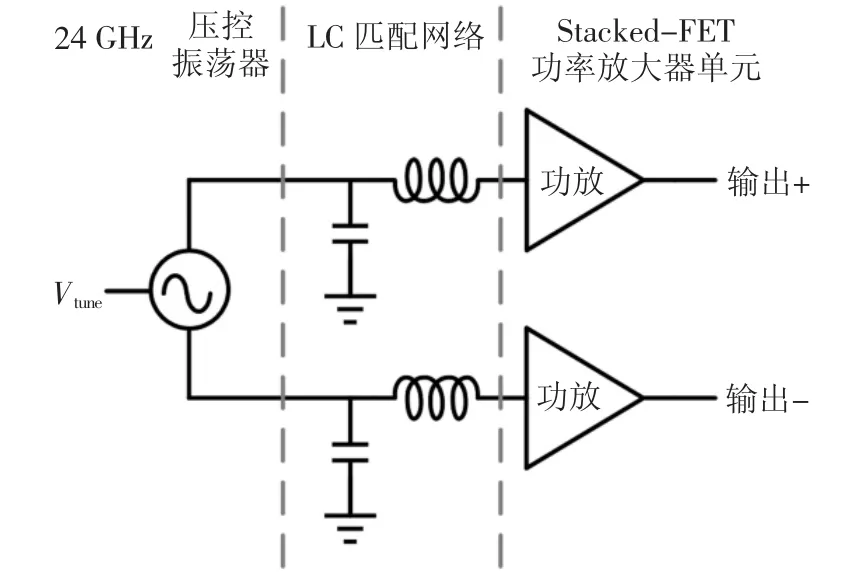

如图1 所示,所设计的信号发生器包括一个24 GHz VCO 和两个24 GHz 频段的PA 单元,PA 中的匹配网络采用共面波导(Coplanar Wave Guide,CPW)传输线进行设计.在VCO 与PA 之间插入LC 匹配网络以改善模块电路之间的功率传输效率.基于低损耗高频印刷电路板(Printed Circuit Board,PCB)的微带环形混合网络已广泛用于微波系统中差分信号的合成,因此,在本设计中,不再设计额外的片上巴伦器件,以实现更小的芯片面积.

图1 信号发生器电路的结构Fig.1 Architecture of signal generator

1.2 模块电路的设计

1.2.1 Stacked-FET PA 分析与设计

CMOS 工艺中的MOSFET 器件具有较小的击穿电压,较大的膝点电压(Vknee)以及较小的电流密度,这些特点限制了CMOS PA 的饱和输出功率(Psat).功率合成技术与Stacked-FET 技术是目前两种常用的提高Psat的方法.与功率合成技术相比,基于Stacked-FET 技术的PA 所需芯片面积较小,并且易于实现宽带阻抗匹配,进行宽带PA 设计.

共源共栅结构的PA 具有较高增益,然而共源共栅PA 的共栅管与共源管的漏源电压摆幅分配不均衡,特别是在放大器的输出功率接近或达到饱和时,共栅管的漏源电压摆幅大于共源管的漏源电压摆幅,极易使共栅管击穿,从而降低电路的可靠性[7].

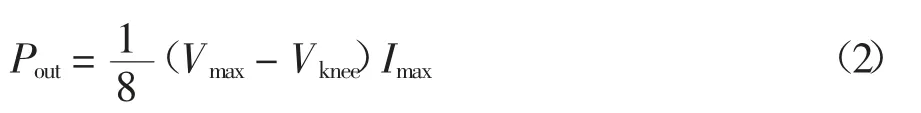

图2 为Dabag 等人[8]提出的一种Stacked-FET PA 的设计方法,首先计算单个晶体管的最佳负载阻抗(Ropt),通过调整Stacked 晶体管栅极所接电容,将晶体管漏极的负载阻抗调整为Ropt的倍数,使每个晶体管具有相同的漏源电压摆幅,提高PA 的Psat以及在高功率工作状态下的可靠性.

偏置在A 类工作模式的PA,具有较高的线性度和Psat.对于偏置在A 类的晶体管,可以基于负载线的方法计算其最佳负载阻抗,表达式如下:

式中:Vmax为最大漏源电压摆幅;Imax为最大漏极电流.基于Load-line 的方法计算出来的最佳负载阻抗只有实部,没有虚部.单个晶体管的最大输出功率的计算表达式如下:

短距离民用微波与毫米波雷达传感器对输出功率的要求通常在10 dBm 左右,基于Stacked-FET 结构的PA 可以达到这一功率要求.

图2 Stacked-FET 结构Fig.2 Stacked-FET architecture

基于上述理论分析,在满足输出功率需求的前提下,通过优化晶体管的尺寸调整功率输出级单个晶体管的Ropt,使n-Stacked-FET 结构的漏端负载阻抗nRopt接近标准50 Ω 负载阻抗,进而省略输出阻抗匹配网络,进行无输出阻抗匹配网络PA 的设计,该设计方法有利于实现较小的芯片面积.

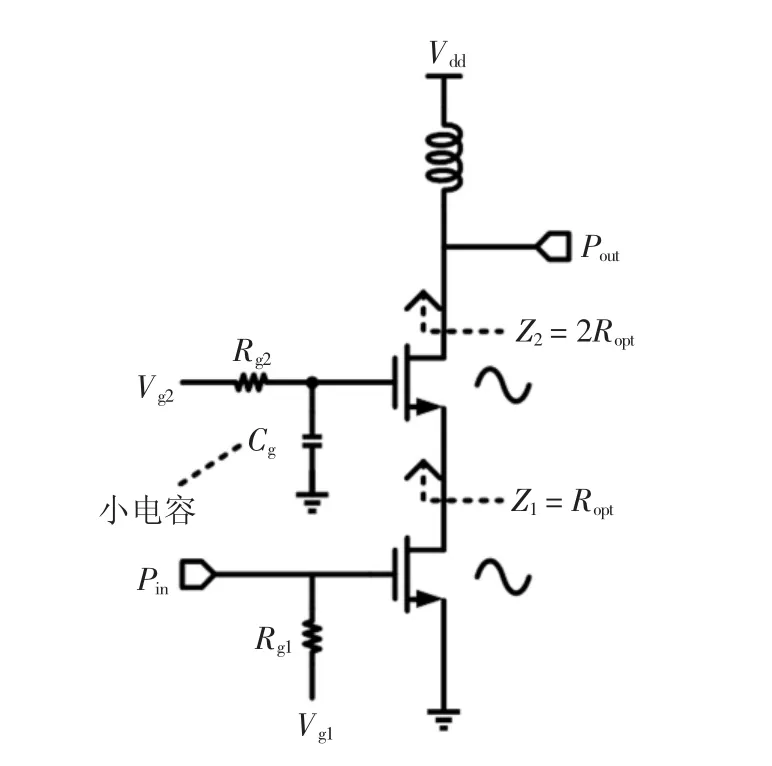

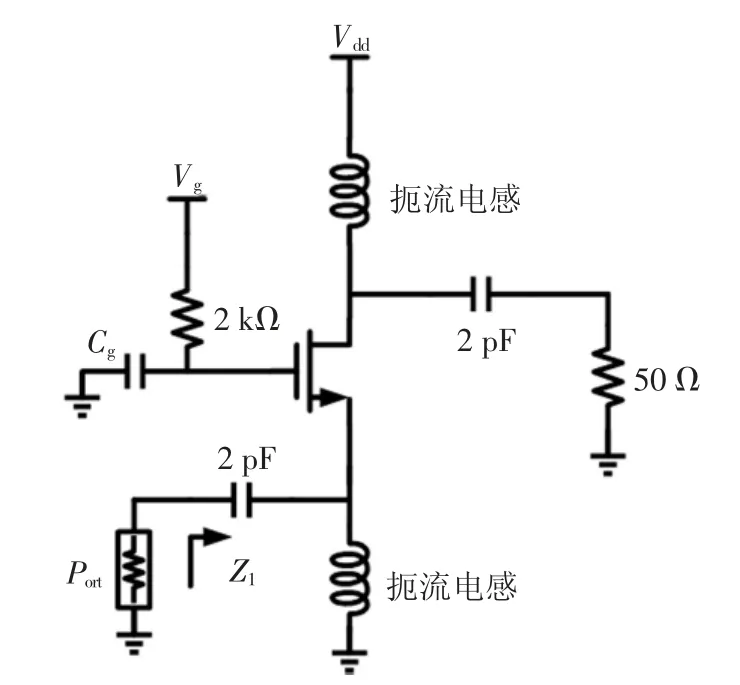

基于上述原理,设计单端两级2-Stacked-FET PA,图3 为2-Stacked-FET PA 的原理图,其中输出级采用2-Stacked-FET 结构,由两个晶体管堆叠而成;驱动级采用单个晶体管的共源结构.

图3 2-Stacked-FET PA 的原理图Fig.3 Schematic of 2-Stacked-FET PA

通过仿真可知,当功率输出级单个晶体管的栅宽为100 μm 时,用公式(1)计算出来的最佳负载阻抗为26.25 Ω,晶体管M3 的漏极所需负载阻抗为52.5 Ω,该阻抗值非常接近标准的50 Ω 负载阻抗,故无需设计输出阻抗匹配网络.

将晶体管M3 的漏极负载阻抗设置为50 Ω,通过调节Stacked 晶体管M3 的栅极所接电容,使功率输出级中从Stacked 晶体管的源极看上去的阻抗为单个晶体管的最佳负载阻抗26.25 Ω,进而使功率输出级的漏源摆幅电压均衡分配在共源管与Stacked晶体管上.通过调节Stacked 管的栅极所接电容来调节共源晶体管负载阻抗Z1的原理图如图4 所示.

图4 用于调节共源晶体管负载阻抗的原理图Fig.4 Schematic for tuning the load impedance of common-source MOSFET

采用CPW 传输线设计输入阻抗匹配网络和级间阻抗匹配网络,保证驱动级的输出1 dB 压缩点比功率级的输入1 dB 压缩点大3 dB,防止PA 提前进入压缩状态;通过减小各级输入晶体管栅极所接偏置电阻来提高PA 的稳定性.

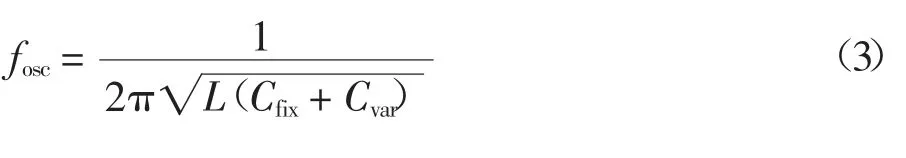

1.2.2 24 GHz class-A 交叉耦合压控振荡器

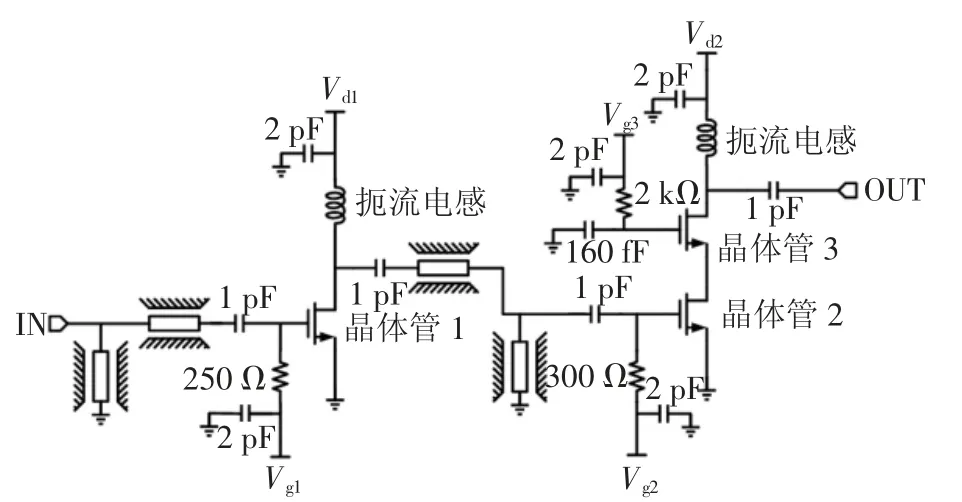

LC 交叉耦合结构的VCO 易于起振,广泛应用于微波与毫米波频率源的设计[9].通常,class-C 结构的VCO 可以实现较低的相位噪声,但是需要在一个核心振荡管的栅极与另一个核心振荡管的漏极之间引入隔直电容,以给核心振荡管的栅极提供额外的偏置电压.隔直电容加在反馈环路上,使VCO 加电后达到稳定振荡状态的时间变长,不利于低功耗短脉冲多普勒雷达的实现[10].class-A 结构的VCO,其核心振荡管的栅极与漏极通过交叉耦合结构直接相连,可以实现较短的起振时间.如图5 所示,本设计中的24 GHz 基频振荡VCO 采用class-A 结构.

VCO 包含一对交叉耦合的核心振荡晶体管(NC-MOS,PC-MOS),一个LC 谐振网络,由共源连接的M1 和M2 构成的用于隔离负载牵引效应的缓冲放大器,以及调节晶体管偏置状态的可变电流源I.振荡频率计算公式为:式中:L 为谐振网络中的电感;Cfix为包括各种寄生电容在内的固定电容值;Cvar为变容管的容值.由公式(3)可知,核心振荡晶体管尺寸确定并兼顾谐振网络Q 值的情况下,所用电感的感值越小,可采用的变容管越大,则调谐范围越宽.因此,在本设计中,采用直径为90 μm 的单圈对称式螺旋电感来获得较大的调谐范围.

图5 24 GHz VCO 的原理图Fig.5 Schematic of 24 GHz VCO

根据交叉耦合VCO 的理论,大的晶体管可以提供更大的跨导,使VCO 更容易起振.但是,由于大的晶体管会引入更大的Cfix,压缩可用调谐范围.因此,在确定核心振荡晶体管的尺寸时,需要对上述指标折衷考虑.优化后核心振荡晶体管的栅宽为50 μm.

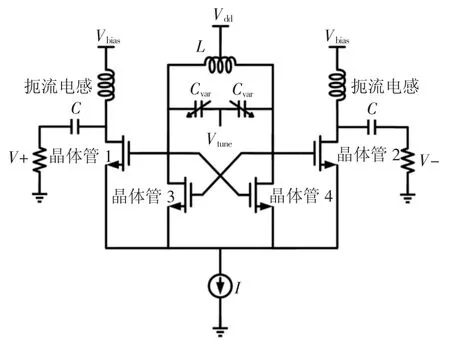

1.3 Dummy 金属对螺旋电感的影响

在CMOS 工艺加工过程中,通常需要在芯片版图上放置一些与电路无关的器件或金属单元,以减小加工过程中的工艺偏差,称为Dummy.其中,放置金属单元的目的是增大芯片上走线比较稀疏的区域的金属密度以达到一定的要求,防止后续加工过程中出现刻蚀不足或刻蚀过度的情况.在MMIC 中,Dummy 金属对微波电路元器件影响较大,如增大寄生电容、引入额外的损耗、降低电感的品质因子等[11].螺旋电感是LC 匹配网络与LC 谐振网络中用到的关键元件,其Q 值对MMIC 的性能有重要影响.

图6 为底层不带Dummy 的螺旋电感和底层带Dummy 的螺旋电感.图7 为对上述螺旋电感进行仿真得到的电感值和Q 值.在高频频段,底层带Dummy 的螺旋电感比底层不带Dummy 的螺旋电感的电感值更小,Q 值更低.在24 GHz 处,电感值减小了3 pH,Q 值减小了4.92.螺旋电感Q 值变差,在VCO 设计中会降低LC 谐振网络的Q 值,进而恶化相位噪声.在LC 匹配网络设计中则会引入较大的插入损耗.

图6 无Dummy 的电感和有Dummy 的电感Fig.6 Inductor without dummy fills and inductor with dummy fills

图7 电感的仿真结果Fig.7 Simulated results of the inductors

在本文设计中,为了获得尽可能准确的仿真模型和尽可能高的电路性能,LC 匹配网络与LC 谐振网络中螺旋电感的正下方区域不填充Dummy.手动绘制自定义的电感单元,并通过电磁场仿真确定电感的感值.

2 模块电路的仿真

对于微波与毫米波频段的集成电路,仅仅通过后仿提参无法得到准确的寄生参数及各种耦合效应.本文在仿真过程中,无源元件(电感、电容、传输线),采用Momentum 软件进行电磁场仿真,得到多端口S参数文件,与晶体管、电阻等其他元件的Spice 模型进行联合仿真.

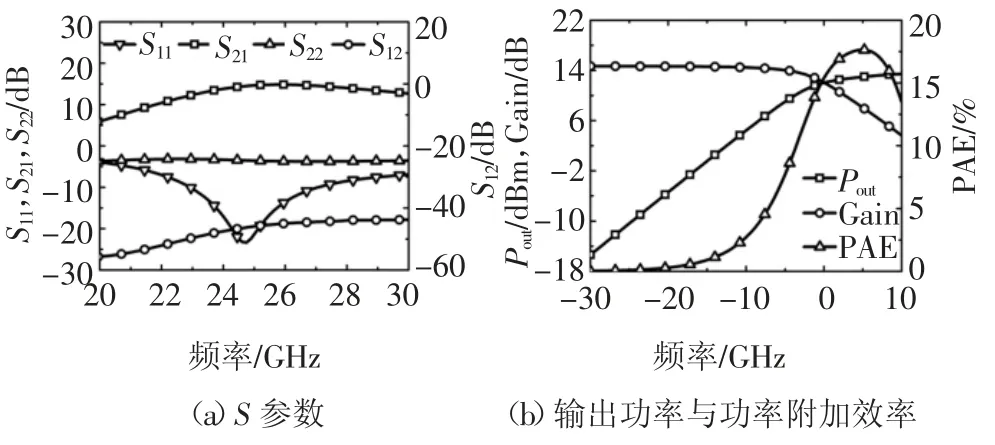

图8 为PA 的小信号S 参数(S11,S22,S12,S21),输出功率(Pout)以及功率附加效率(Power Added Efficiency,PAE)的仿真结果.S11在23~27 GHz 范围内小于-10 dB,表明输入端口实现了良好的阻抗匹配,输出端口未加阻抗匹配网络;S22在20~30 GHz 频段上大概为-4 dB.该PA 可以提供14.6 dB 的小信号增益(Gain),Pout达到13.4 dBm,PAE 的峰值为17.6%.

图8 PA 的仿真结果Fig.8 Simulated results of the PA

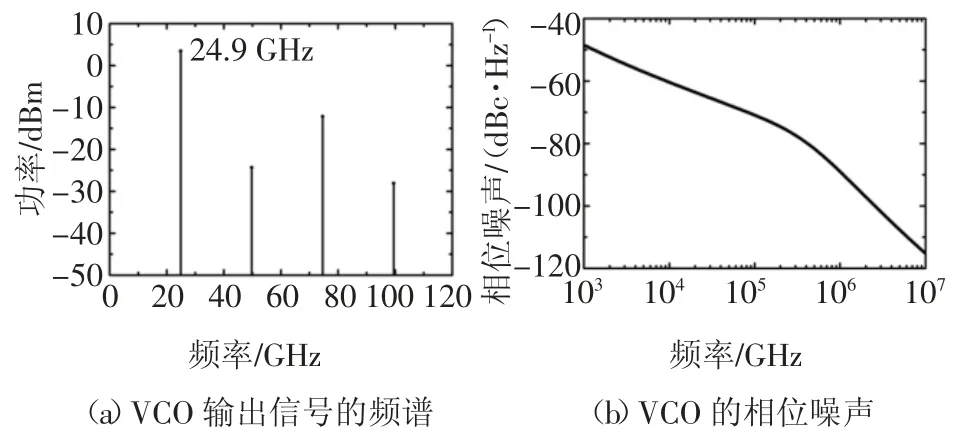

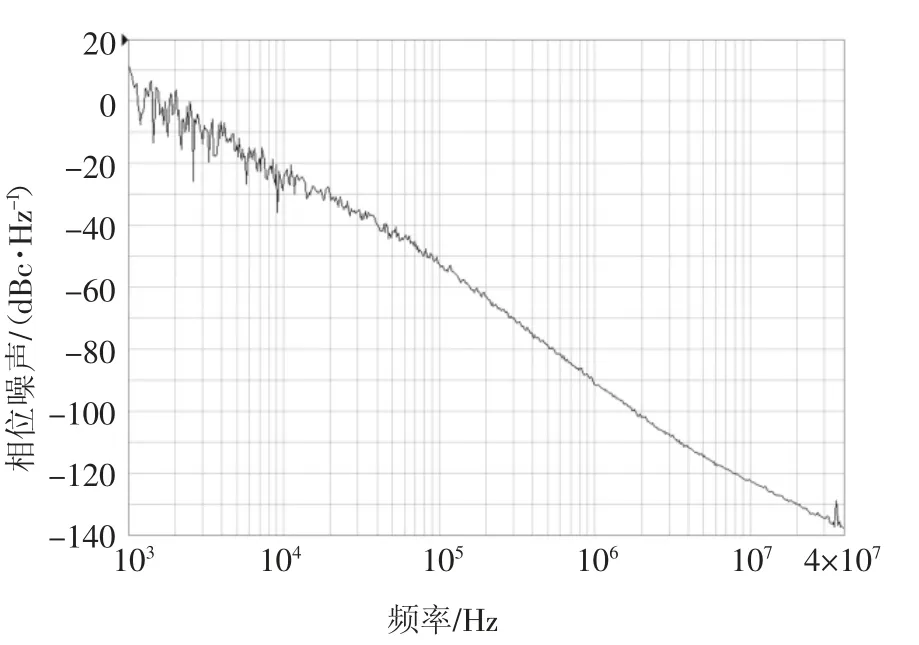

图9 为仿真得到的VCO 输出信号的频谱和相位噪声.由图9 可知,VCO 能够稳定振荡在24 GHz频段,在偏1 MHz 处的相位噪声为-89 dBc/Hz,在偏10 MHz 处的相位噪声为-115 dBc/Hz.VCO 相位噪声在偏100 kHz 与1 MHz 之间存在一个拐点,在拐点之前,相位噪声下降较为平缓,分析可能是由SOI CMOS 工艺中Floating body 类型MOSFET 器件所特有的浮体效应引起的低频Lorentzian 噪声导致的[12].

图9 VCO 仿真结果Fig.9 Simulated results of the VCO

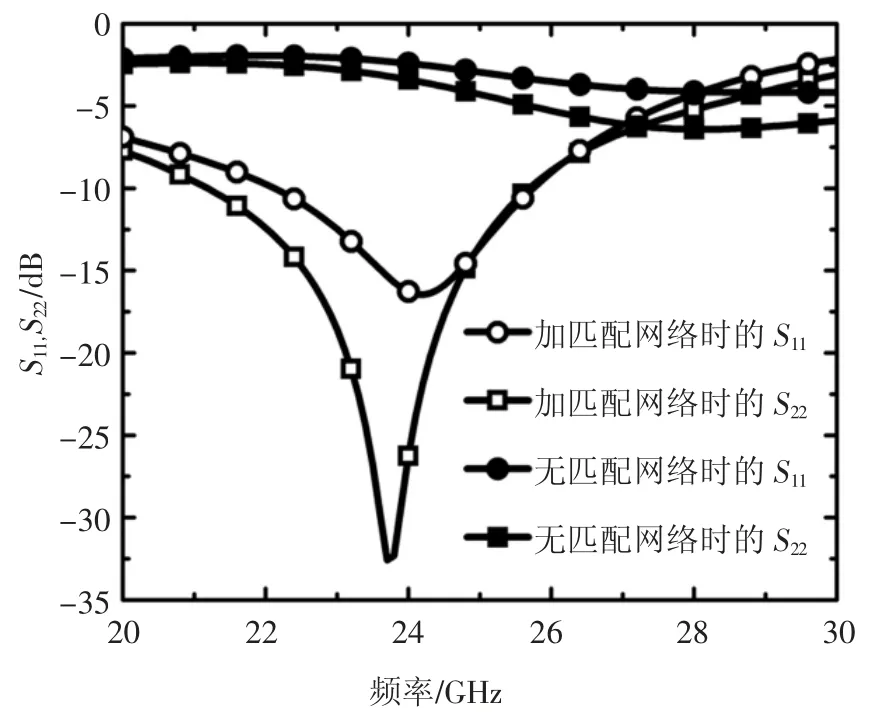

PA 的输入端口匹配到50 Ω 的源阻抗,因此,在进行信号发生器芯片设计时,需要在VCO 与PA 之间插入阻抗匹配网络,提高功率传输效率.

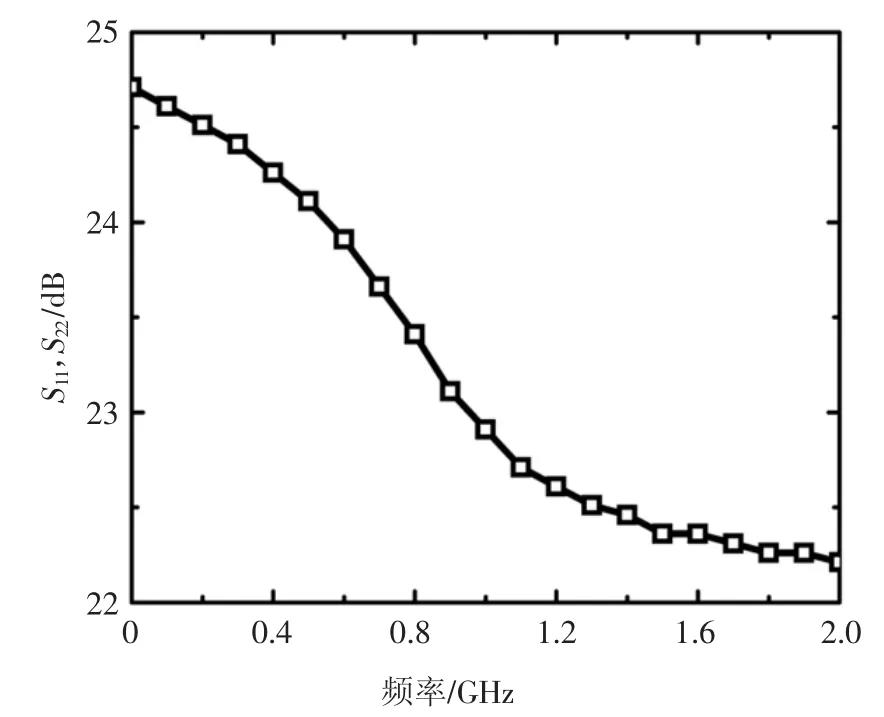

本文采用L 形LC 结构的阻抗匹配网络,图10为在VCO 的输出端口加LC 匹配网络和不加LC 匹配网络S11和S22参数的仿真结果.可知,在VCO 的输出端口添加匹配网络之后,S11参数在21.2~25.6 GHz 范围内低于-10 dB,S22参数在22.2~25.7 GHz 范围内低于-10 dB.与未加匹配网络相比,VCO 在24 GHz 频点附近的反射系数得到了很好的改善.

图10 VCO S11 和S22 参数仿真结果Fig.10 Simulated S11 and S22 of VCO

3 测试结果与分析

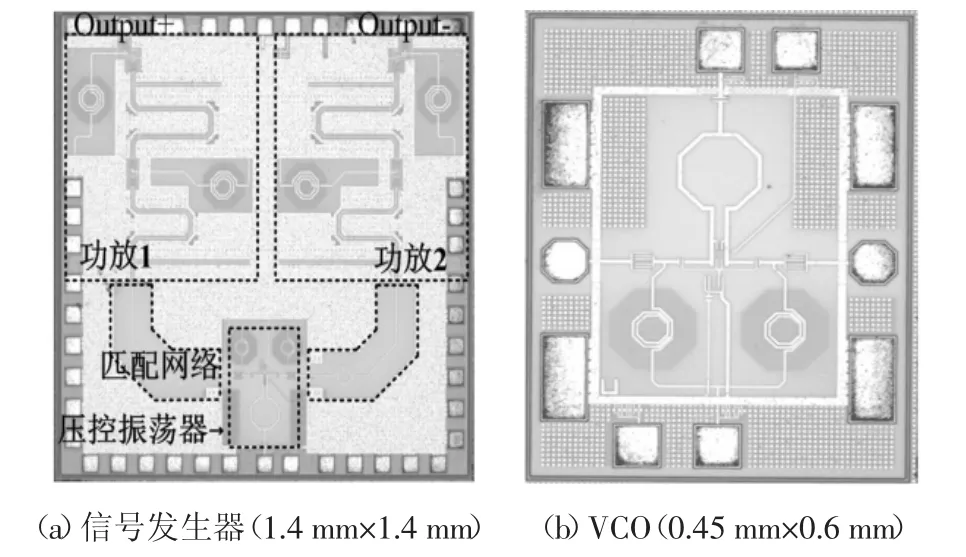

本文所设计的24 GHz 信号发生器采用90 nm SOI CMOS 工艺流片加工,芯片面积为1.4 mm×1.4 mm.该芯片包含一个24 GHz class-A 结构的VCO,两个差分放置的Stacked-FET PA 单元,以及模块电路间的LC 匹配网络.为了评估模块电路之间匹配网络的性能,对VCO 也进行了加工和测试.

图11(a)为24 GHz 信号发生器芯片的显微照片,图11(b)为24 GHz VCO 的显微照片.测试时,将芯片固定在测试用PCB 板上,并通过健合金线为芯片提供偏置电压和调谐电压.在各管脚处放置必要的滤波电容,防止PA 加电后出现低频振荡.射频信号的两个差分输出端口(输出+,输出-),其中一端通过键合线连接至测试板上,负载为50 Ω;另一端通过GSG 探针和同轴线缆连接至频谱分析仪.

图11 芯片的显微照片Fig.11 Micrograph of chips

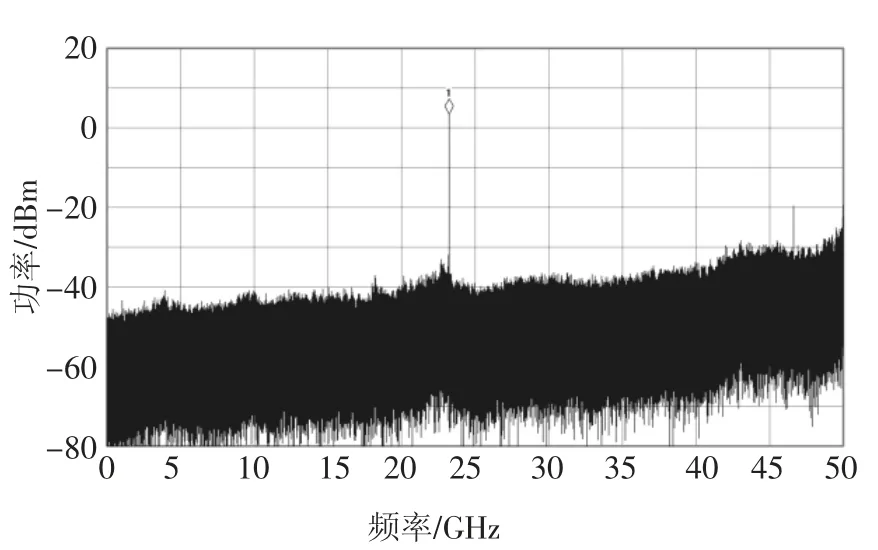

加电后,VCO 能够稳定起振,PA 能够稳定工作.图12 为测试得到的信号发生器输出信号的频谱.

图12 信号发生器输出信号的测试频谱Fig.12 Measured spectrum of the output signal of the signal generator

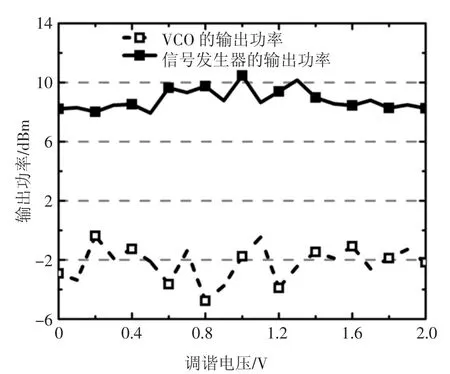

本文所采用的工艺提供了2.5 V 的变容管器件,因此调谐电压的范围可以设置得宽一些.图13 为输出信号的频率随调谐电压的变化关系.该信号发生器芯片能够稳定输出22.2~24.7 GHz 频段的信号,中心频率为23.45 GHz,与24 GHz 相比有所偏移,可能是由工艺偏差导致的,但该信号发生器的输出频率依然覆盖了国内和国际上通用的24 GHz ISM 雷达传感器的工作频段,即24~24.25 GHz.

图13 信号发生器测得的频率调谐范围Fig.13 Measured frequency tuning range of the signal generator

采用E5052B 信号分析仪和E5053A 变频器对VCO 的相位噪声进行测试,图14 为在VCO 振荡频率为22.24 GHz 时测得的相位噪声.在偏1 MHz 和10 MHz 处,VCO 的相位噪声分别为-91 dBc/Hz 和-123 dBc/Hz.

在测试输出功率时,同轴线缆引入的损耗以3 dB 的经验值进行估算.考虑到差分输出,总输出功率在单端测试结果上加3 dB.图15 为VCO 在相同偏置电压下,信号发生器与VCO 输出功率随调谐电压的变化关系.信号发生器的平均输出功率为8.83 dBm,峰值输出功率为10.5 dBm.表明插入VCO 与PA 之间的LC 匹配网络,在螺旋电感底层不添加Dummy 金属的情况下,实现了良好的匹配性能.在测试过程中,通过对多个样品进行测试,均未发现因局部不填充Dummy 金属而导致的可靠性问题,表明本文设计方法具有一定的可行性.

图14 测得的VCO 的相位噪声Fig.14 Measured phase noise of the VCO

图15 信号发生器与VCO 的输出功率Fig.15 Output power of signal generator and VCO

表1 给出了本文设计的测试结果与其他文献中结果的对比.从表1 中可以看出,本文基于SOI CMOS 工艺,通过采用Stacked-FET 结构的功率放大器和高Q 螺旋电感,实现了较高的输出功率和较宽的频率调谐范围.

表1 本文与其他文献性能的对比Tab.1 Comparison of performance in this paper with other literatures

4 结论

本文基于90 nm SOI CMOS 工艺设计了一款24 GHz 信号发生器电路.通过优化晶体管的尺寸,设计出无输出阻抗匹配网络的Stacked-FET PA,提高了Psat和MOS 器件大功率工作时的可靠性.通过电磁场仿真分析了Dummy 金属对螺旋电感性能的影响,在设计用于LC 谐振网络和LC 阻抗匹配网络的电感时,去除底层的Dummy 金属,可提高螺旋电感的Q 值.测试结果表明,该信号发生器实现了10.5 dBm的峰值输出功率,可用于24 GHz 雷达收发芯片,同时验证了设计方法的可行性.