CMOS 工艺节点进展中器件技术的革新

2020-03-02裴志军

裴志军

(天津职业技术师范大学电子工程学院,天津 300222)

电真空管的发明开启了电子技术时代,更低功耗、更小尺寸晶体管的出现使电子技术进入新时代,而第1 块集成电路的发明开启了微电子时代[1]。早期的集成电路采用基于双极结型晶体管(bipolar junction transistor,BJT)的双极技术,但BJT 的静态功耗限制了单个芯片中可以集成的最大晶体管数量。1963 年,仙童公司发布了第1 块CMOS(complementary metal oxide semiconductor)逻辑门电路,具有几乎零静态功耗。但与CMOS 技术相比,NMOS(negative channel metal oxide semiconductor)技术的工艺更简单,成本更低,单个芯片中可以集成更多晶体管。因此,早期MOS(metal oxide semiconductor)集成电路采用了NMOS 技术,然而与CMOS 技术相比消耗更多静态功耗。在20世纪80 年代,当单个芯片中集成数千个晶体管时,功耗成为一个严峻的问题。由于CMOS 技术具有低功耗、高速、可靠性能等优点,最终在数字技术领域得到应用并逐步替代NMOS 技术和双极技术[2]。随后CMOS技术持续改进,工艺特征尺寸不断缩小。近些年来,电池供电的便携式产品应用需求日益增加,但电池技术的发展很难适应便携式设备能耗的增加,而随着CMOS 技术工艺微缩,晶体管尺寸更小,芯片上集成的晶体管数量增加,同时较小电容使得延迟减小及动态功耗降低。因此,随着CMOS 技术的不断进步,集成电路的成本、性能以及功耗得到有效改善。CMOS 工艺技术的微缩遵循摩尔定律,历经了微米、亚微米、深亚微米、超深亚微米等工艺节点。然而CMOS 工艺节点从22 nm 到14 nm,以及从10 nm 进入到当前的7 nm 或5 nm,甚至随后的3 nm 及以下,芯片中晶体管的结构尺寸逐渐接近材料中的原子大小,CMOS 技术演进面临着愈来愈严峻的挑战,摩尔定律的推进已经明显放缓[3]。在CMOS 工艺节点进展中,为了减小各种短沟道效应的影响,新技术、新材料、新器件结构得到了广泛应用,器件技术从传统平面晶体管转向SOI 场效应晶体管(silicon-on-insulator field effect transistor,SOIFET)以及新三维器件结构如鳍式场效应晶体管(fin field effect transistor,FinFET)、环绕栅极(gate-all -around,GAA)结构等[4-5]。为此,本文对CMOS 工艺节点进展中的挑战与器件技术的革新进行分析探讨。

1 MOSFET 器件的短沟道效应

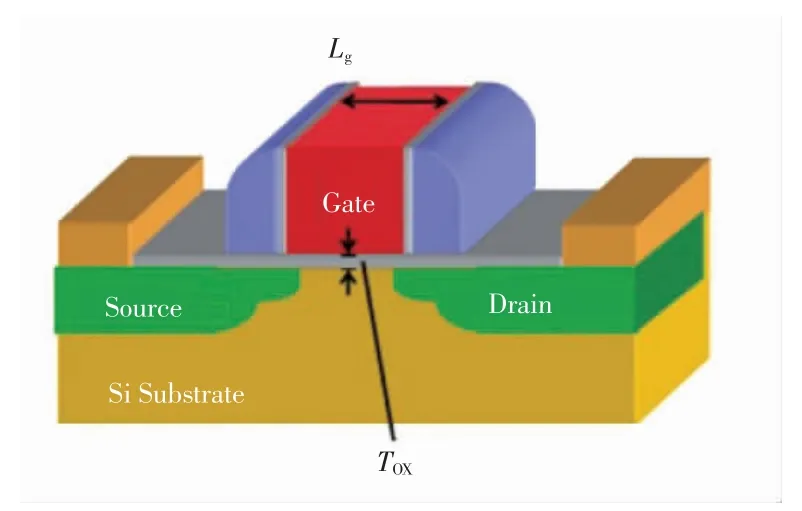

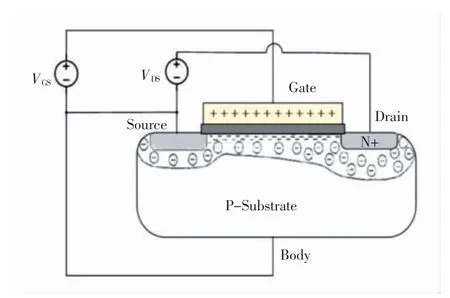

CMOS MOSFET 器件采用金属(metal)作为栅极、氧化物(oxide)作为绝缘层、半导体(semiconductor)作为衬底,即MOS 结构,具有源极(source)、漏极(drain)、栅极(gate)和衬底(substrate)共4 端子,MOSFET 器件结构如图1 所示。MOS 结构中,在源区和漏区之间的区域称为沟道(channel),基于导电沟道的类型,可分为互补的NMOS 和PMOS 两类。对于NMOS 晶体管,当栅极正偏压VGS足够大时,沟道区的空穴被电场排斥,形成耗尽区。如果栅偏压进一步增加,大于阈值电压VTH时,大量电子被吸引到沟道表面,出现反型,形成N 型导电沟道,NMOS 晶体管沟道反型如图2 所示。当漏极与源极间施加正偏压VDS时,电子将从源极经导电沟道到漏极运动,形成导通电流。可见,器件的导通或截止由栅极偏压产生的沟道垂直电场所控制,所以称为场效应晶体管FET。

图1 MOSFET 器件结构

图2 NMOS 晶体管沟道反型

早期的MOS 晶体管的栅极材料通常采用金属铝(Al)而不是多晶硅(Poly-Si),制造工艺从源区和漏区开始,随后形成金属铝栅极,如果栅极掩模没能对准,将导致寄生的重叠输入电容Cgd 和Cgs,从而降低晶体管的开关速度。若采用自对准工艺,从栅极开始,随后形成漏区和源区,可使得栅极相对于源区和漏区自动对准,从而减小了相应的寄生电容。漏区和源区掺杂工艺要求高于800 ℃的高温退火,而栅极材料铝的熔点约为660 ℃,在此高温下将熔化,而采用多晶硅作为栅极材料,则不会熔化。因此,自对准工艺采用多晶硅作为栅极。另外,与金属栅相比较,多晶硅栅还能够获得较低阈值电压,从而与CMOS 工艺节点进展中器件工作电压的降低相适应。

随着CMOS 技术的进步,MOS 晶体管尺寸不断缩小,当沟道长度不满足远大于源、漏耗尽区宽度之和时,则称为短沟道器件。短沟道器件中,漏区和源区更靠近,需要考虑沟道中二维电场分布和高电场所产生的各种效应[6-7]。

(1)载流子速度饱和迁移率下降

NMOS 晶体管中,沟道中电子的漂移速度在高电场时趋向于饱和,即载流子速度饱和。短沟道器件中,随沟道纵向电场增加,高电场下发生载流子速度饱和,使饱和电流下降,影响器件特性。此外,随纵向电场增加,沟道中的载流子也将受到氧化层界面散射的影响,导致载流子迁移率降低,使得导通电流下降。

(2)漏致势垒降低和穿通

短沟道器件中,随漏极偏压的增加,漏极端的耗尽区增大延伸,导致沟道势垒降低,使得阈值电压减小,这种效应即漏致势垒降低(drain induced barrier lowering,DIBL)。DIBL 将导致出现亚阈值电流,并使导通时电流随漏极偏压增加而增大。另外,随着漏极偏压增加,漏极端的耗尽区向源极端的耗尽区延伸,当2个耗尽区融合时,发生沟道穿通,如图3 所示。此时,栅极偏压将失去对沟道电流的控制,器件将无法关断而失效。

图3 沟道穿通

(3)热载流子效应

短沟道器件中,随着电场增加,特别是在漏极端,载流子将获得大量能量,称为热载流子。热载流子在漏极端附近碰撞电离,产生新的电子-空穴对,从而导致生漏极与衬底间的漏电增加。另外,少量热电子还可以穿过栅氧化层而被栅极收集,一些热载流子甚至有可能损伤栅氧化层导致器件失效。

2 应变硅技术、高K 电介质及金属栅

随着CMOS 工艺节点进展,当MOSFET 器件尺寸微缩到纳米尺度时,沟道中纵向高电场引起载流子迁移率下降。通过应变硅技术在沟道中引入应力,可以增加载流子迁移率。如对于PMOS 晶体管,当沟道中存在压缩应力时,可增加空穴迁移率。为了能够在硅沟道中产生压缩应变,在源极端、漏极端的区域通过外延生长硅-锗(Si-Ge)薄膜,由于锗原子大于硅原子所产生的应力挤压沟道并增大空穴的迁移率,从而改善晶体管的驱动电流和速度性能。应变硅技术最早应用于90 nm 工艺节点,PMOS 晶体管中具有硅-锗薄膜的源、漏结构在沟道中引起压缩应变,而NMOS 晶体管中由高应力氮化硅(Si3N4)帽层来引入沟道应变,从而有效提高MOS 晶体管的性能[8]。

另外,在MOS 晶体管中,栅极对沟道的控制与栅氧化层电容COX密切相关。减小栅氧化层厚度可增大栅氧化层电容,减小了耗尽区宽度,从而改善短沟道效应。因此,为了抑制短沟道效应,CMOS 工艺节点进展中,栅氧化层SiO2电介质的厚度也随着沟道长度近似按比例缩小,在65 nm 工艺节点,栅氧化层厚度约为1.6 nm。如果栅氧化层厚度进一步减小,则载流子直接隧穿现象占据主导,将导致栅极漏电。因此,栅极与沟道间的隧穿泄漏所限定的栅氧化层厚度约为1.6 nm。为了增加栅氧化层电容,还可以采用高介电常数K 的电介质材料,这意味着允许采用更厚的电介质层来改善载流子隧穿漏电。此外,随着MOSFET 器件尺寸不断缩小,多晶硅栅与氧化层界面的多晶硅耗尽增加,这将导致等效的氧化层厚度增加,影响栅氧化层电容,使器件性能下降,因此栅极多晶硅耗尽层厚度也需要改善;多晶硅栅与高K 电介质的兼容也存在问题,若采用金属栅代替多晶硅栅,不仅可以消除多晶硅耗尽效应,还能够与高K 电介质兼容。英特尔公司在45 nm 工艺节点,引入了基于铪(HfO2)的高K 电介质栅氧化层和金属栅,NMOS 晶体管和PMOS 晶体管中栅极采用了不同的金属[9]。通常,有效氧化层厚度(effective oxide thickness,EOT)与介电常数K 和氧化层厚度Tox 的关系可表示为:EOT=3.9Tox/K。SiO2的介电常数为3.9,而铪材料的介电常数约为25,可见6 nm 厚的铪材料相当于大约1 nm 厚的有效氧化层厚度。

3 MOSFET 器件结构革新

传统MOSFET 器件结构中,为了抑制短沟道效应,通过增加沟道掺杂浓度可以使耗尽区宽度减小。虽然沟道掺杂可减少短沟道效应的影响,但是由于离子注入或热扩散掺杂工艺的随机性,使沟道内掺杂杂质的分布也具有随机性。这种沟道杂质的随机掺杂将引起器件阈值电压的波动,即随机掺杂涨落效应(random dopants fluctuation,RDF)。一方面,随着CMOS工艺节点进展,器件尺寸微缩,沟道内掺杂杂质的总数减少,随机掺杂的相对涨落更加显著,尤其在亚50 nm 工艺节点,沟道随机掺杂将引起阈值电压的激烈波动,严重影响器件性能[10]。另一方面,随着MOSFET 尺寸微缩,漏源距离越近,栅氧化层愈薄,漏电越严重。此外,随着栅极与沟道间的接触面积减小,栅极对沟道的控制也将受到严重影响。因而,传统的MOSFET 器件结构的沟道长度随CMOS 工艺节点进步而持续缩小,栅极将很难完全控制沟道,导致亚阈值漏电增加,功耗也相应增加[11]。MOSFET 器件的亚阈值漏电性能可以采用亚阈值摆幅S 来衡量,表示器件在亚阈值工作情况下漏源电流变化10 倍所需要的栅电压变化量,单位为mV/dec。在MOSFET 器件的实际应用中,期望S 值越小越好,300 K 时S 的极限值为60 mV/dec。器件的S 值越低意味着在同样的亚阈值栅压下漏极电流越小,开关速度越快。MOSFET 器件的开关性能与沟道控制及沟道输运有关,可以通过各种革新的MOS 器件结构来改善,如SOIFET、FinFET 和GAAFET 等,以便增大栅氧化层电容,减小寄生电容,同时也改善了RDF 效应的影响[12-13]。

3.1 SOIFET

SOIFET 器件结构与传统MOSFET 结构的主要区别在于采用隐埋氧化层(buried oxide,BOX)与衬底隔离,SOIFET 结构如图4 所示。

图4 SOIFET 结构

SOIFET 的制造工艺与传统MOSFET 工艺相似,但基于SOI 晶圆,SOI 晶圆包括形成晶体管的薄硅体层、绝缘隐埋层和硅晶圆衬底3 层。SOIFET 器件可分为部分耗尽PD-SOI(partially depleted-SOI)和全耗尽FD-SOI(fully depleted-SOI)2种结构。PD-SOI 结构的硅体层为50~90 nm,而FD-SOI 结构的硅体层仅为5~20nm,器件工作时完全耗尽[14]。FD-SOIFET 的非常薄的硅体层自然限定了源、漏结深和耗尽区,从而减小了DIBL 等短沟道效应,可改善器件的亚阈值特性,降低电路的静态功耗。由于隐埋氧化层BOX 的存在,减小了漏极端和源极端的寄生电容,也使漏极与衬底间漏电路径不再存在。可见,与传统MOSFET 结构相比较,FD-SOIFET 器件的亚阈值特性更好,延迟和动态功耗更低,更适合低功耗应用;FD-SOIFET 不需要沟道掺杂,可以避免随机掺杂涨落RDF 效应,从而使阈值电压保持稳定,同时还可以避免因沟道掺杂引起的载流子迁移率退化;SOIFET 器件也没有传统CMOS电路可能存在的闩锁问题。虽然与传统MOSFET 工艺类似,但SOI 晶圆的成本较高,SOIFET 器件也存在自加热问题,隐埋氧化层绝热性好,不利于功耗的散发。

3.2 FinFET

鳍式场效应晶体管FinFET 的概念最初源于双栅MOS 晶体管的构想,通过增加栅极与沟道的接触面积来增强对导电沟道的控制[15]。当前FinFET 器件通常是三栅MOS 晶体管的三维立体结构,可以在体硅或SOI晶圆上实现,FinFET 结构如图5 所示。FinFET 器件结构中,衬底上的垂直体硅薄翅片类似于鱼鳍(Fin),栅极从三面围绕沟道,从而能够有效进行控制。不同于传统平面MOSFET 结构中的水平沟道,FinFET 器件结构中导电沟道是垂直的,FinFET 的沟道控制如图6 所示。图中,沟道宽度W 与Fin 的高度HFin和宽度WFin有关,但主要由Fin 的高度决定。增加Fin 的高度可增大FinFET 器件的驱动电流,还可以采用多个Fin 并联方式来增加器件的驱动电流。因此,对于FinFET 器件来说,有效的沟道宽度往往是Fin 高度的倍数。与传统MOSFET 结构相比较,FinFET 器件结构中,栅极围绕在沟道周围并且体硅Fin 非常薄,有效改善了短沟道效应,可免除沟道掺杂,从而消除沟道随机掺杂涨落RDF 效应的影响,同时也使得沟道载流子具有更高的迁移率。相对与于传统MOSFET 结构来说,FinFET 器件在给定面积条件下具有更高的驱动电流,可获得更高的速度,同时也具有更低的漏电,从而可获得更低的功耗[16]。FinFET 器件技术最早由英特尔在22 nm 工艺节点中采用,随后在16 nm、14 nm、10 nm、7 nm 等工艺节中广泛应用。实际上,现代CMOS 工艺节点中往往是应变硅技术、金属栅、高K 电介质,以及FinFET等各种新技术的融合[17]。

图5 FinFET 结构

图6 FinFET 的沟道控制

FinFET 器件技术不仅极大降低了漏电,也有效增加了栅氧化层电容,提高了晶体管的开关性能。与SOIFET 相比较,FinFET 具有更高的驱动电流,但FinFET 制造工艺更复杂。FinFET 结构中热量也易于积聚在翅片上,影响散热效率。

3.3 GAAFET

尽管SOIFET 和FinFET 结构中,栅极对沟道都具有较好的控制性能,但在10 nm 以下工艺节点,漏电再次成为挑战性问题[18]。特别是随着CMOS 工艺微缩到5 nm 及以下工艺节点,亚阈值漏电、漏致势垒降低DIBL 等效应的严峻挑战正推动着新的场效应晶体管结构的研究,如GAAFET 结构,作为这些先进CMOS工艺节点的潜在候选者[19]。在GAAFET 结构中,栅极环绕在沟道的所有边侧,GAAFET 示意图如图7 所示。纳米线场效应晶体管(nanowire FET,NWFET)与FinFET 相比较具有更好的沟道控制,显著减小了DIBL 效应的影响,可获得较低的亚阈值漏电,从而具有更好性能和低功耗,并且晶体管尺寸更小。

图7 GAAFET 示意图

虽然环绕栅极GAA 结构通常可以提供比FinFET更好的性能,但是也存在驱动电流、寄生电容等方面的问题。为了增大驱动电流,可将多个纳米线堆叠在一起以增加有效沟道宽度,水平式环绕栅堆叠纳米线结构如图8 所示[20]。水平纳米线FET 可以想象为将FinFET 的导电沟道切成碎片,每个碎片则变成水平纳米线,作为源极和漏极之间的导电沟道。与水平纳米线NWFET 类似的GAA 结构还包括纳米片(nanosheet)FET 或纳米板(nano-plate)FET,只是作为导电沟道的纳米线变成了更宽、更厚的纳米片或纳米板,以便能够进一步获得更大的驱动电流[21-22]。为了减小寄生电容,用作源、漏间导电沟道的这些纳米线、片或板的形状也可以根据需要而有所变化。另外,若将纳米片挤压到一起,构成纳米环,则能够有效降低寄生电容。

图8 水平式环绕栅堆叠纳米线结构

CMOS 工艺技术进步中,环绕栅极GAAFET 结构是当前FinFET 之后最具前途的候选者,然而从更长远来看,还存在其他选择,如III-V 族FinFET、互补式FET(complementary FET,CFET)、隧 道FET(tunnel FET,TFET)以及垂直纳米线FET 等[23-25]。

4 结语

随着CMOS 工艺技术的进步,MOS 晶体管尺寸不断缩小,各种短沟道相关效应,如载流子速度饱和迁移率降低、漏致势垒降低、热电子效应、沟道随机掺杂涨落等显著影响MOSFET 器件的亚阈值摆幅、功耗等性能。为了减小短沟道效应的影响,提出了应变硅技术、高K 电介质氧化层、金属栅、SOI 等新方法以改善器件性能。然而,在28 nm 以下工艺节点,平面MOSFET器件结构中,栅极对沟道的有效控制面临严峻挑战,而革新的三维立体器件结构,如FinFET 结构具有更有效的栅极控制,可获得更优异的器件性能。随着CMOS 工艺技术进一步微缩,在10 nm 以下工艺节点,器件亚阈值漏电再次成为挑战性问题。与FinFET 相比较,各种GAAFET 结构中栅极环绕沟道,具有更好的沟道控制性能,可作为5 nm 以下工艺节点最具前途的解决方案。随着器件特征尺寸逐渐达到硅材料中的原子大小,从而接近物理极限的限制,新材料、新工艺如碳化硅(SiC)、磷化铟(InP)、氮化镓(GaN)等化合物半导体材料的相关研究将受到越来越多的关注。