三值光学处理器三模冗余表决系统设计与实验

2019-10-31沈云付

彭 聪,沈云付

(上海大学计算机工程与科学学院,上海200444)

近年来,由于超级计算机功耗的急剧上升,关于新型高性能计算机的研究越来越多[1].三值光学计算机是一种新型的计算机,其处理器具备可重构以及三值计算的特性.长期以来,金翊等[2]提出了以无光态和偏振方向相互正交的2个偏振光态(垂直偏振光和水平偏振光)表示信息,以液晶和偏振片构造光学处理器的三值光学计算机概念和结构,基于降值设计理论实现了可重构的三值光学处理器(ternary optical processor,TOP)[3],并利用小规模现场可编程门阵列(field programmable gate array,FPGA)芯片验证了新设计的重构电路等[4].三值光学计算机中均方位移(mean square displacement,MSD)加法器理论与技术的提出推进了其实现大规模数值计算的进程,使得各数据位在MSD加法器中能够并行计算[5].

对于任何处理器的设计而言,其可靠性至关重要.目前,三值光学处理器在可靠性设计方面还不够完善.由于受现有技术的影响和限制,现在的三值光学处理器还是一种以电路控制、光路结构计算的系统,其中还存在很多不确定因素影响着三值光学处理器运行的可靠性.引发三值光学处理器运行失效的原因有:①处理器硬件系统随着工作时间的增加而可靠性降低;②不失一般性地,考虑三值光学处理器的重构存储单元(如FPGA)在遭到诸如电磁干扰等情况时,容易造成处理器系统的重构指令和运算数据错误.到目前为止,三值汉明码纠错与检错技术的提出在三值光学计算机数据通信的可靠性方面起到了一定的作用[6],但仍然没有一种容错方法能够直接保障处理器运算输出的正确性.

以三模冗余(triple module redundancy,TMR)的方式对系统逻辑单元的输出进行表决是提高系统部件可靠性的经典的容错技术,其原理是:3个模块同时执行相同的操作,采用3取2的原则令大部分相同的输出作为表决的正确值.在电子计算机中关于三模冗余表决的应用是非常普遍的,如当静态随机存取储器(static random-access memory,SRAM)单元在太空环境中出现单事件干扰(single event phenomena,SEU)的事故首次被发现时,Ruano等[7]为可靠性低于100%的存储芯片电路提出了一种轮替的TMR表决机制;考虑到电磁环境的特殊性和复杂性,Ruano等[8]还提出了一种可靠的TMR投票方案,其目的是为了确保电路严格正确地工作.此外,有很多关于改进仲裁器电路结构的工作,Kshirsagar等[9]设计了一种全新的容错架构的TMR表决器,并提出了相关的算法,这种TMR结构可以掩盖表决器自身所产生的错误.而Michele等[10]在评估TMR投票的可靠性时发现,由于互连扩展和增加电路中与选择器集成存在串扰问题,因此他们提出了在原来的TMR表决框架上进行再度表决方案.这些成功的三模冗余表决应用表明,基于TMR表决的容错方法在提高系统部件的可靠性中起着重要作用,本工作将对三值光学处理器展开三模冗余表决系统设计与实验.

1 三值光学处理器简介

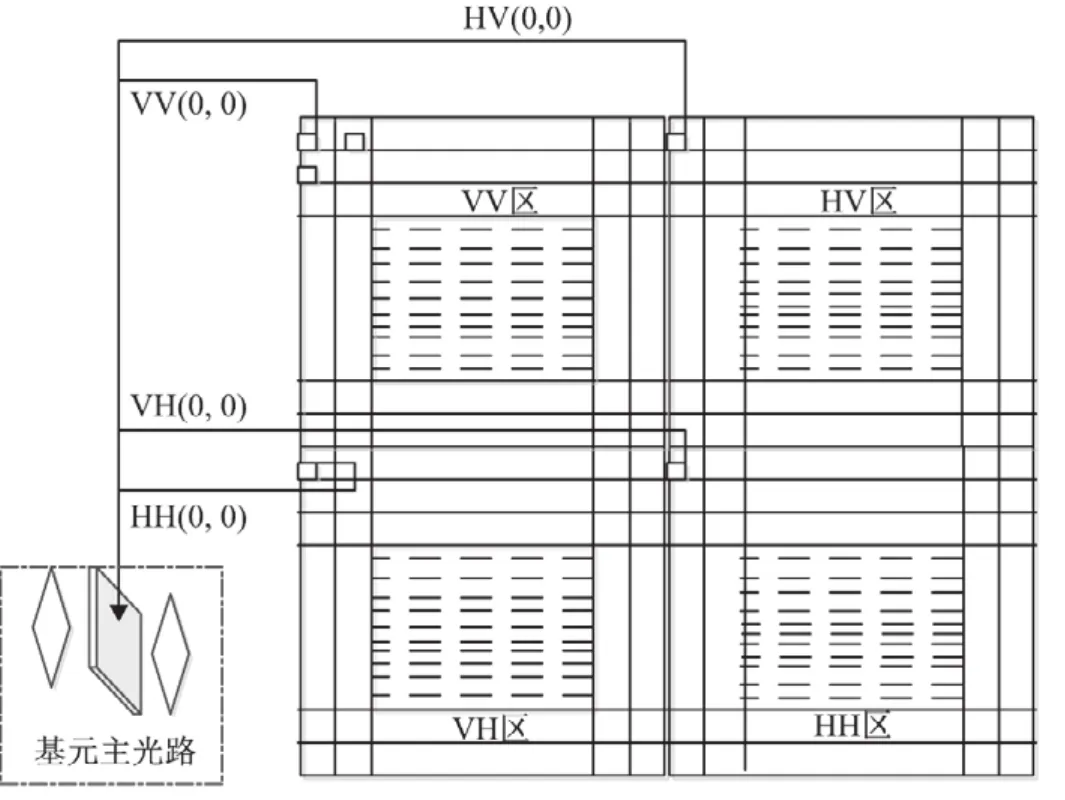

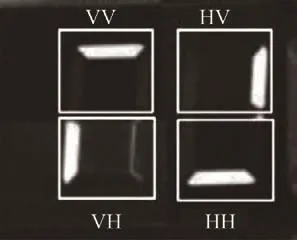

三值光学处理器的运算单元叫做基础运算单元(basic operation units,BOUs).降值设计理论表明,三值光学处理器可以由18种最基本的基元构成,而在三值光学处理器上任意重构的运算器将使用不超过6种基元[11].基元的运算采用光的2个相互垂直的偏振态(垂直偏振态和水平偏振态)以及无光态表达信息(见图1),在本工作中,这3种信息状态的数值符号分别记为-1,1和0.

1.1 基元

基元在空间上具有统一的结构,由主光路和控制光路组成.图1中,4个网格阵列区域表示液晶像素,在这4个液晶像素区的正面和背面贴有垂直偏振片或水平偏振片:在VV区像素的前面和后面都贴有垂直偏振片;VH区像素的前面贴垂直偏振片而背面贴水平偏振片;HH区像素的前面和后面都贴有水平偏振片;HV区像素的前面贴水平偏振片而后面贴垂直偏振片.因此4个液晶像素区都具有相同的“偏振片-液晶-偏振片”的三明治结构.将4个区域左上角的像素相应地标记为坐标(0,0),相同坐标的三明治结构的像素位VV(i,j),HV(i,j),VH(i,j)和HH(i,j)构成单个基元主光路的4条子光路,4条子光路拥有对应的控制光路,基元的外部特征如图2所示.对于200×100的液晶像素阵列,三值光学处理器可轻松构造出(200×100)/4=5 000个运算单元.

图1 三值光学处理器液晶像素阵列区:组成基元主光路Fig.1 Liquid crystal pixels of TOP:used to make up of the BOUs'main optical path

图2 基元的外部特征Fig.2 The external feature of single BOU

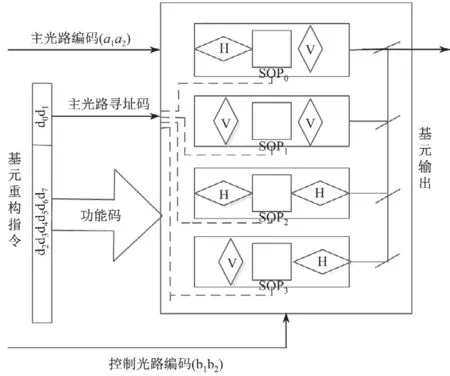

1.2 基元重构运算操作及输出

基元被用于重构组合成运算器,而对于每一位基元的重构操作,具有如图2所示的d0d1d2d3d4d5d6d7,a1a2,b1b23个输入数据部分,其中d0d1d2d3d4d5d6d7是8位的重构指令,各为2位的a1a2和b1b2分别是用于调制主光路和控制光路信号的编码数据.基元的重构运算操作如下:重构指令用于重构出特定的基元,2位的地址码d0d1会对主光路寻址并且选定子光路,而功能码位d2d3d4d5d6d7对选定的子光路所对应的控制光路进行作用,对投射在液晶上的光信号进行旋光和转换.与此同时,编码寄存器中的a1a2和b1b2分别对基元主光路和控制光路的光信号进行调制(垂直光、水平光或无光),被重构的基元随后进行相应的计算.

事实上,基元的每一次重构运算,其主光路只有一条子光路在工作,而其他3条子光路被关闭[3].主光路的4条子光路在被重构选择后,成为具备实际运算功能的子处理单元.为了方便说明,基元主光路中具备运算功能的HV,VV,HH和VH子光路模块分别记为SOP0,SOP1,SOP2和SOP3.

对于SOP0和SOP1来说,主光路中的信号最终透过的垂直偏振片能够吸收水平偏振光,其输出集为Ω1={0,-1}.相应地,SOP2和SOP3主光路上最终透过的水平偏振片能够吸收垂直偏振光,并输出信号集Ω2={0,1}.这2个输出集反映了基元重构运算输出的三值特点,也说明基元的三值输出空间可降解为二值输出空间.针对基元的SOP0,SOP1以及SOP2,SOP3子处理器模块的二值输出特征,可以分别对其统一设计表决器Voter1和表决器Voter2.

2 三值光学处理器三模冗余表决系统设计

2.1 表决器设计

三模冗余表决的布尔逻辑表达式为Cout=M1M2+M1M3+M2M3+M1M2M3,其中M1,M2和M3是3个相同单元的输出,一起作为表决器的输入.这个逻辑说明表决器可以通过光逻辑部件实现.

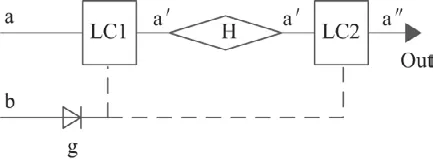

首先提出2个偏振光比较部件,用于判断2束光强是否同时具有相同的偏振类型,称为偏振光“与”门.为方便说明,将垂直偏振光和无光记为V型光集合,而水平偏振光和无光记为H型光集合.

判断2束光在同一时间为垂直偏振光的“与”门结构如图3所示,图中a和b的输入均为V型光集合中的光强,LC1和LC2是2个加电旋光液晶,中间夹着能够吸收垂直偏振光而透过水平光的水平偏振膜h,g为将光转换为电的感光管.其原理如下:当a和b的输入都是垂直偏振光时,b中的光强信号被感光管g转换为电流,用于控制LC1和LC2的旋光;光束a经LC1的旋光作用后被转换成水平偏振光a′,a′能穿过水平偏振膜到达LC2;受到LC2的旋转后,a′再次被转换为垂直偏振光a′′,得到信息值-1.对于a和b的输入不同时为垂直偏振光的其他情况,很容易验证垂直偏振光“与”门的输出为无光,且信息值为0.

图3 垂直偏振光“与”门Fig.3 AND gate for vertical polarized light

图4 水平偏振光“与”门Fig.4 AND gate for horizontal polarized light

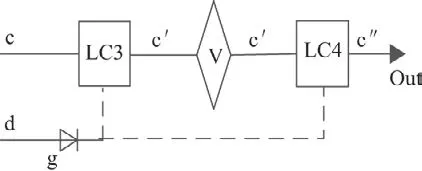

类似地,比较2束光强是否同时为水平偏振光的“与”门结构如图4所示.图中c和d的输入是H型光集合中的光强,液晶片LC3和LC4中间夹着垂直偏振片“v”(能够吸收水平光而透过垂直光).当c和d同时输入水平偏振光时,水平偏振光“与”门输出信息值为1的水平偏振光;在c和d不同时输入水平偏振光时,输出无光态的信息值0.以上2种“与”门运算简记为AND.

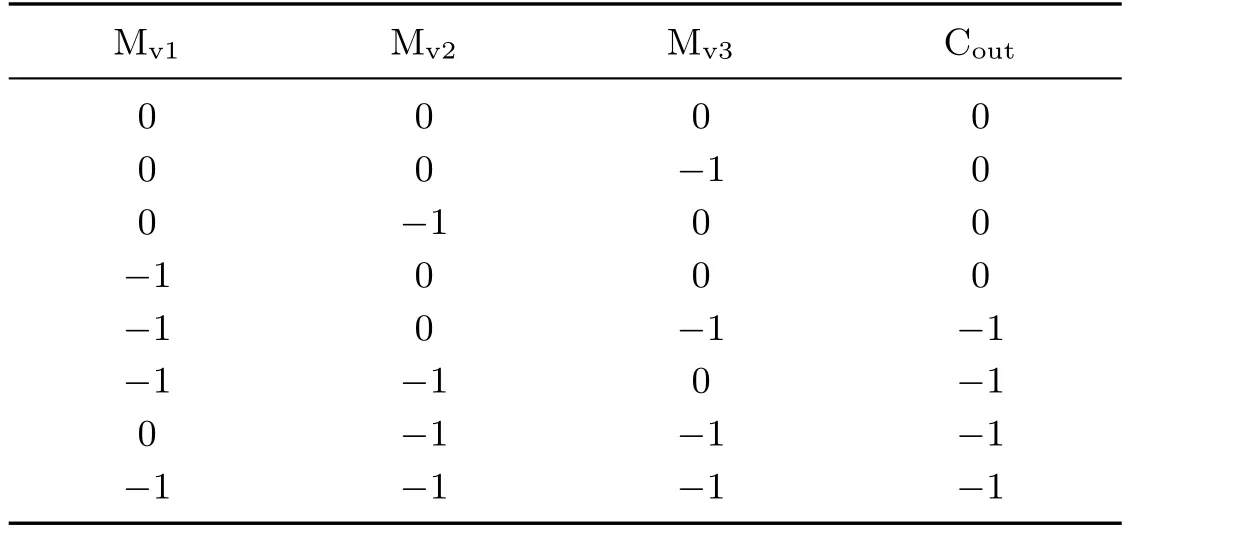

表1 基元SOP0和SOP1单元的表决真值Table 1 Voting truth table of SOP0and SOP1

表2 基元SOP2和SOP3单元的表决真值Table 2 Voting truth table of SOP2and SOP3

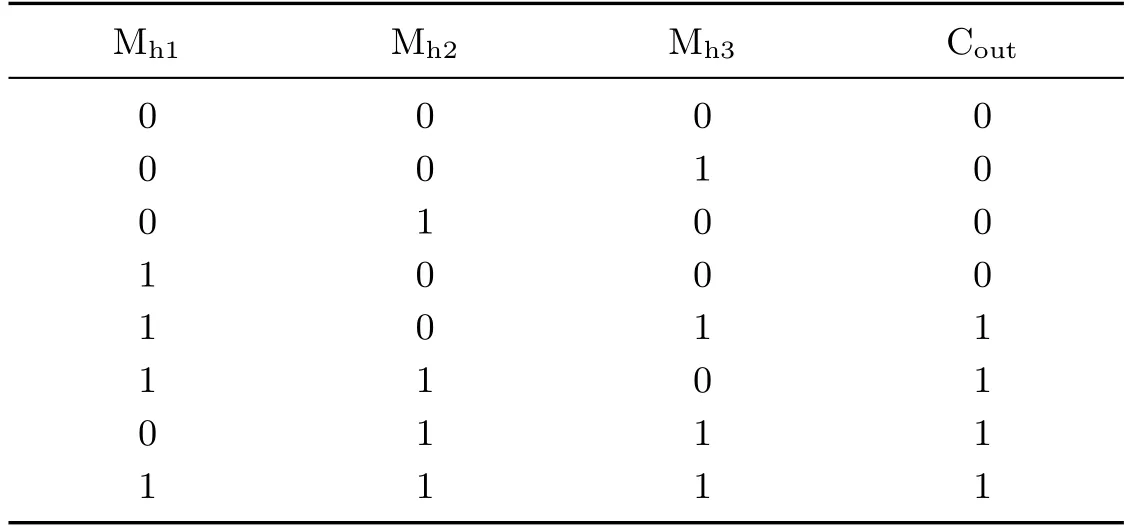

基元子处理单元SOP0和SOP1的TMR表决真值如表1所示,表中Mv1,Mv2和Mv3为SOP0或SOP1的3个相同模块的输出,具有相同的信息输出空间Ω1.对SOP0和SOP1单元设计的TMR光电表决器Voter1的结构如图5所示,图中左侧2条短粗斜线代表分光镜,用于将Mv1,Mv2,Mv3的光束分成3组进入3个垂直偏振光“与”门.右侧2条短粗的黑色斜线是半反半透镜,用于叠加来自3个“与”运算的输出信号,以产生表决结果Cout.其原理为用2个分光镜分别对Mv1和Mv3的光强输出进行分光,其中Mv1和Mv3各自一半的光强一起进入到垂直偏振光的“与”门形成AND1运算;同时,Mv1和Mv3各自剩余的一半光强分别与Mv2协作,通过2个垂直偏振光“与”门形成AND2和AND3运算;最后,将3个“与”门的光信号输出进行叠加,产生Voter1的表决结果.例如,当Mv1,Mv2和Mv3的输出分别为垂直偏振光、垂直偏振光以及无光时,Mv1,Mv2和Mv3的输出信号进入Voter1后,AND2运算输出垂直偏振光,而AND1和AND3都输出无光,经过对3个“与”门光信号叠加后,表决得到垂直偏振光(信息值为-1).

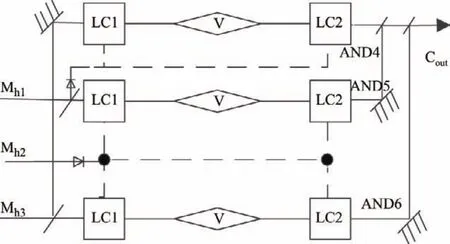

对SOP2或SOP3设计的表决器Voter2的光电结构如图6所示,表2是相应的表决真值.其中,Mh1,Mh2和Mh3是SOP2或SOP3的3个相同单元的输出,具备相同的信息输出空间Ω2.与Voter1类似,Voter2的表决原理是对Mh1,Mh2和Mh3的光强输出分光成3组,进入3个水平偏振光“与”门进行AND4,AND5和AND6运算,再将3个“与”门运算的光束输出进行叠加,以产生表决信号.

图5 表决器Voter1光电结构Fig.5 Photoelectric structure of Voter1

图6 表决器Voter2光电结构Fig.6 Photoelectric structure of Voter2

2.2 三值光学处理器三模冗余表决系统建构

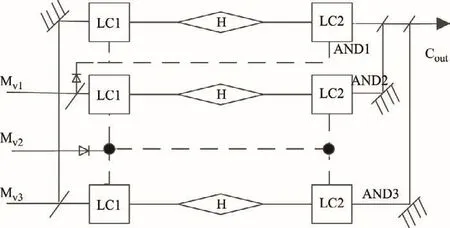

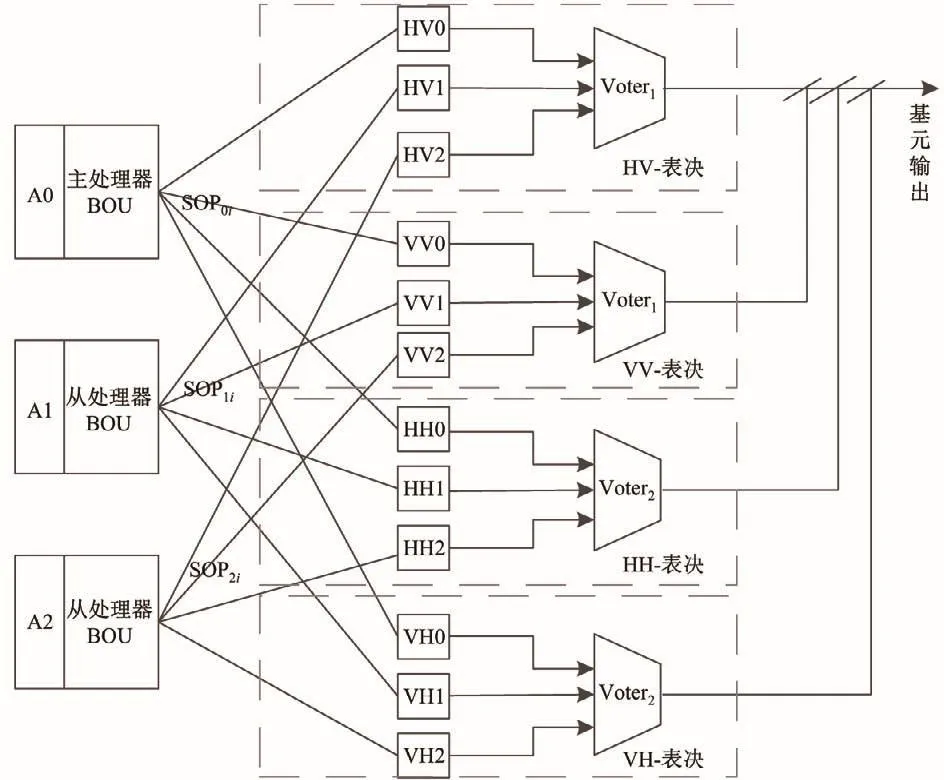

对三值光学处理器建构表决系统,将直接针对系统所有的基元结构的4个子处理单元部署表决器.三值光学处理器三模冗余表决系统框架如图7所示,构建步骤如下.

步骤1 设A0为主处理器,在原液晶板上扩建另外2个从处理器A1和A2,A1和A2具有和主处理器A0相同的构造.将3个处理器同一位置的3个等位基元分别标记为BOU0,BOU1和BOU2,这3个基元都有4个具有实际执行功能的子处理模块,记为SOP0i、SOP1i和SOP2i(i=0,1,2).对于当K=0,1,2时,SOPki在i=0,1,2,3情况下分别表示这3个处理器基元的主光路各自分别被重构为HV,VV,HH以及VH类型光路.

步骤2 在如图7所示的3个协同进行表决的基元中,SOP0i,SOP1i和SOP2i子处理单元的输出将构成4组表决,分别为HV型光路表决、VV型光路表决、HH型光路表决以及VH光路表决.HV光路的表决由SOP00,SOP10,和SOP20的输出组成;VV光路的表决由SOP01,SOP11和SOP21的输出组成;HV光路的表决由SOP02,SOP12和SOP22的输出组成;而HV光路的表决由SOP03,SOP13和SOP23的输出组成.这里,HV和VV的表决使用Voter1,而HH和VH的表决使用Voter2.

步骤3 3个基元从同一控制系统接收一条相同的重构指令,重构指令会按主光路寻址码确定主光路类型.此时,SOP0i,SOP1i和SOP2i各自的一个具体的子处理单元将执行运算.例如,一条正确的重构指令对3个处理器上等位的基元重构为HV型光路,这3个基元主光路中的HV光路同步、独立进行运算.

步骤4 4组表决中,HV型主光路表决的结果代表系统基元SOP0单元运算的最后结果,VV型光路的表决结果代表基元SOP1单元的运算值,HH型光路的表决结果代表基元SOP2单元的运算值,而VH型光路的表决结果代表基元SOP3单元的运算值.

此外,对用于存储基元运算所需数据(重构指令、主光路和控制光路编码)的部件进行三模冗余,即对任意基元的重构锁存器组以及主控光路上的2个输入寄存器组进行冗余.由于三值光学处理器运算单元之间的运算已实现了同步,因此可以保证下位机控制器对三模冗余基元的3个输入数据的同步,也就保证了三模冗余基元运算的同步.

对于三值光学处理器上的任意一个基元的4组TMR光路表决中,仅有一组会输出期望值.考虑一条8位的系统重构指令,将主副处理器中同一位置的3个基元重构选择为HV型主光路(SOP0),如果主处理器A0中的基元被重构错误或者在运行过程中出现异常,那么A0中该位基元的HV光路重构运算不正确(数据位运算失效).经过HV型光路区的表决,即使屏蔽了其发生的错误,最后也能得到系统期望的计算值.而对于表决系统表决出错误结果的数据位,应该对各分区中相应错误的数据位进行重复计算和表决.

图7 三值光学处理器三模冗余表决框架Fig.7 Framework of TMR-based voting system of TOP

3 一位处理器三模冗余表决实验

由于三值光学处理器的运算单元具有独立并行计算的特点,故本工作为一位的可重构处理器设计了硬件表决实验,以验证三模冗余表决在三值光学处理器上应用的有效性和可行性.在本实验中,每个处理器只有一个基元,并且设计了3个重构电路程序副本用于对3个基元重构控制,借助了3台Dice-SemⅡ数字仿真综合实验箱辅助完成.将QuartusⅡ软件设计的重构程序下载到3台实验箱上的ACEX1K PLD(可编程逻辑器件)后,连接好三模冗余整体电路系统,令3个实验箱共同接地,其中1个实验箱上的脉冲被用作三模冗余系统接连的同步时钟.通过拨动实验箱上的开关来实现三模冗余基元的重构操作,并借助电键开关手动注入基元的重构指令以及主控编码数据的错误,以便模拟系统故障错误.

3.1 一位处理器的三模冗余表决结构实现

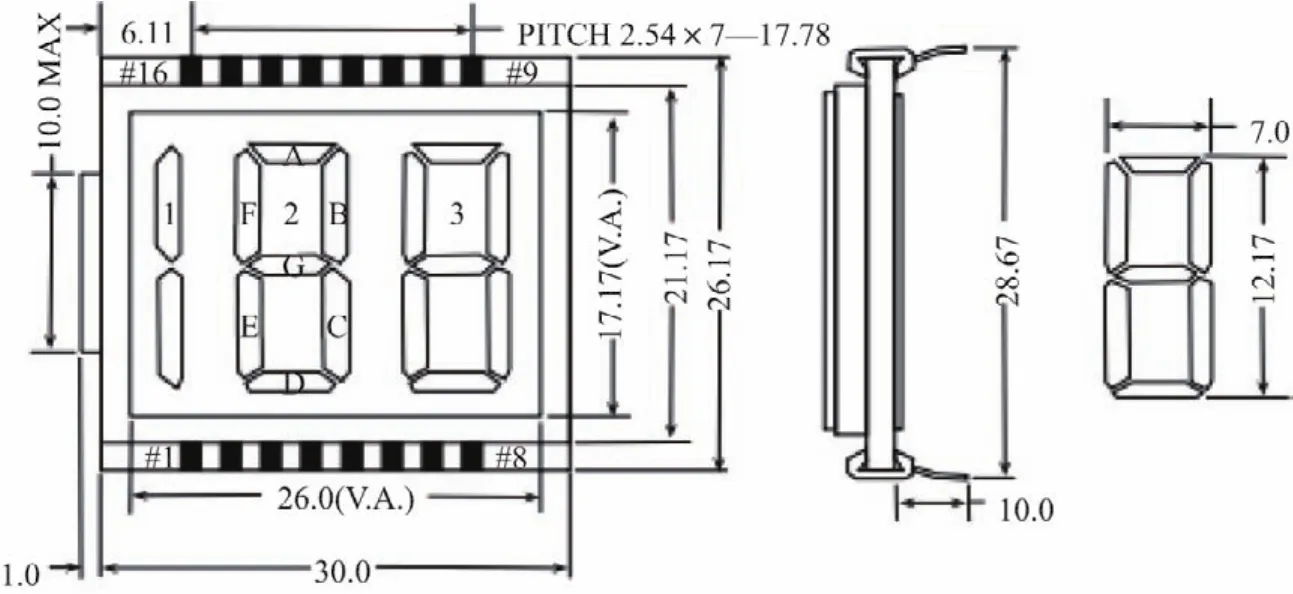

在本实验中,基元与表决器的制作利用了EDS819 TN静态笔段液晶LCD(见图8).EDS819 TN-LCD的光源分布均匀,且光强度高,有标记为1,2,3的3个部分,其中第2和第3部分分别有标记为A~G的7个笔段,并且2G,3G笔段以及第1部分将不被用到.

图8 EDS819 TN型笔段液晶LCD规格Fig.8 Specification for TN stroke segment LCD

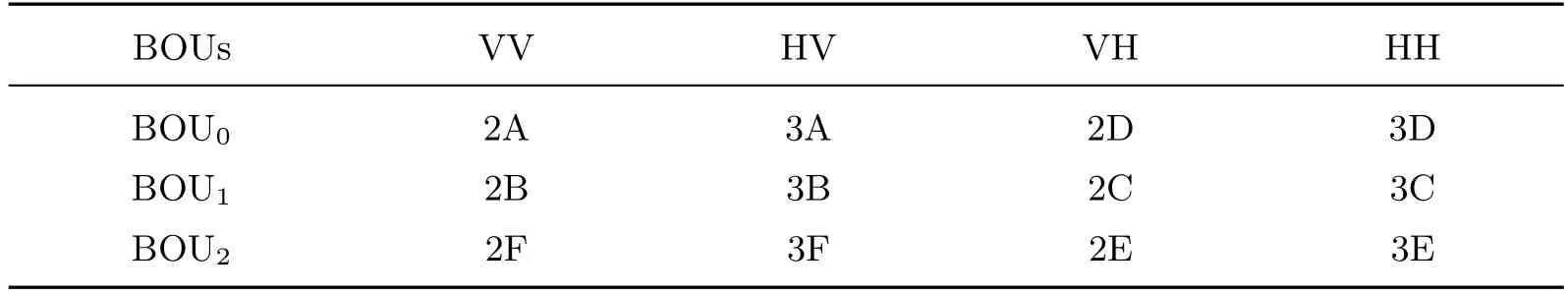

3个基元(BOU0,BOU1,BOU2)的主光路在EDS819 TN-LCD中的笔段分配如表3所示,(2A,3A,2D,3D)笔段用于构成BOU0的主光路像素,其中2A表示VV型光路,3A表示HV型光路,2D表示VH型光路,以及3D表示HH型光路.与此类似,(2B,3B,2C,3C)笔段用于构成和表示BOU1的主光路像素,而(2F,3F,2E,3E)笔段则用于表示BOU2的主光路像素.使用3片EDS819 TN-LCD,并在其对应的主光路笔段位之间放置相应的偏振片,贴紧与对齐后构建3个基元的物理结构(关于基元物理结构的更多细节,可以参考文献[4]).

图9为基元4个表决光路区,图中3层结构的(2A,2B,2F)笔段的输出构成了基元VV型主光路区中表决器的输入,(3A,3B,3F)笔段的输出作为HV型主光路区中表决器的输入,(2D,2C,2E)笔段的输出作为VH型主光路区中表决器的输入,而(3D,3C,3E)笔段的输出则作为HH型主光路区中表决器的输入.

表3 一位处理器三模冗余表决实验基元主光路笔段分配表Table 3 Stroke segments assignment for BOUs'main optical path

图9 基元4个表决光路区的说明Fig.9 Speci fi cation for the four voting regions

使用2片EDS819 TN-LCD及偏光片制作用于4个表决区的2种表决器,并将4个表决器与4个表决区域平行放置,2层液晶结构表决器的各笔段与3个基元的各笔段对齐,其间留有间隙以便放置感光管与透镜.为方便操作与观察,4个表决区的表决结构设计如下:对于VV型主光路表决区,将BOU1的2B笔段的光强输出转换为电流,直接控制该区表决器的2A和2F笔段,形成(2A,2B)和(2F,2B)“与”运算,运算后的光强由表决器的2A和2F笔段显示.用透镜对BOU1的2A笔段的光强输出分出一半,以控制该区表决器的2F笔段,进而形成(2A,2F)“与”运算,光强从表决器的2F笔段出来.VV区的表决结果最终由该区表决器的2A和2F笔段显示.与此类似,对于HV表决区,该区表决器的(3F,3A),(3F,3B)以及(3A,3B)笔段组分别形成“与”操作,表决结果由HV表决区中表决器的3A和3B笔段显示.在VH表决区中,表决器的笔段(2C,2D),(2C,2E)以及(2D,2E)形成“与”操作,结果由VH表决区中表决器的2D和2E笔段高亮显示.而在HH表决区内,笔段(3E,3C),(3E,3D)以及(3C,3D)构成3个“与”操作,并由HH表决区中表决器的3C和3D笔段显示表决结果.

3.2 实验用例设计与表决结果分析

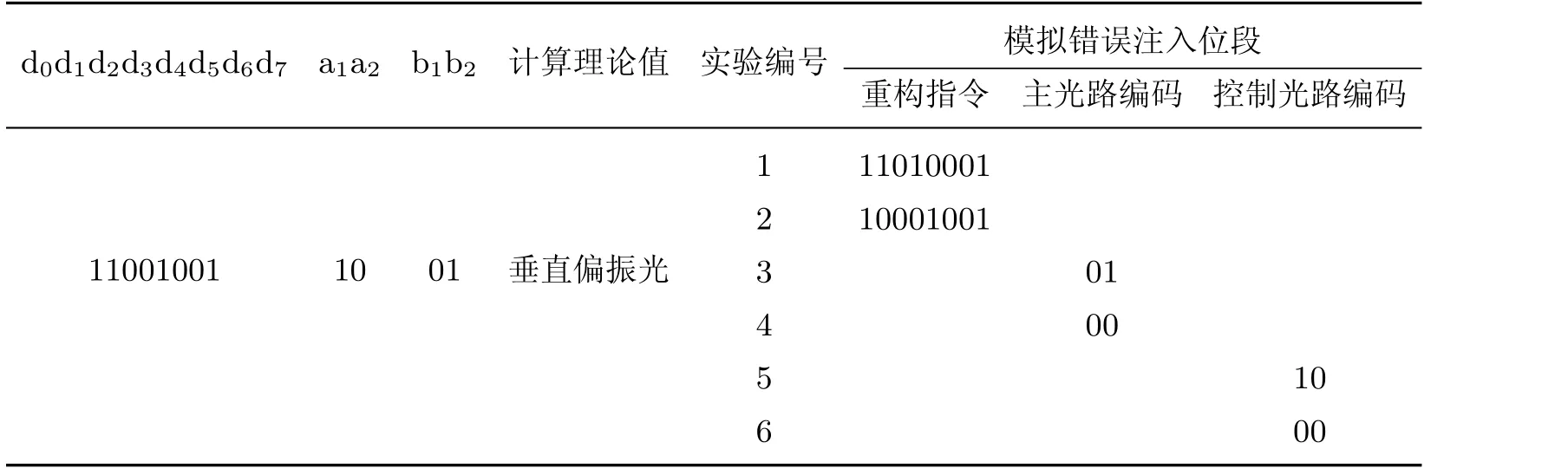

本实验以基元重构运算操作所需的重构指令(d0d1d2d3d4d5d6d7)、主光路编码(a1a2)、控制光路编码(b1b2)数据发生错误的情况来进行设计.由于这3个数据中的每个出错的数据都可能导致基元计算错误,因此实验中针对每个类型的基元,对其重构运算操作的3个数据分别设计了2个用例,这样18种基元共设计了108个表决用例.

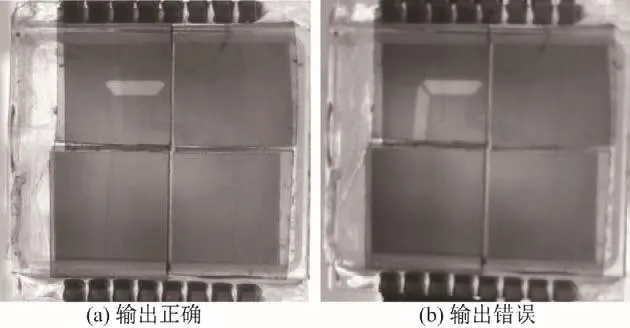

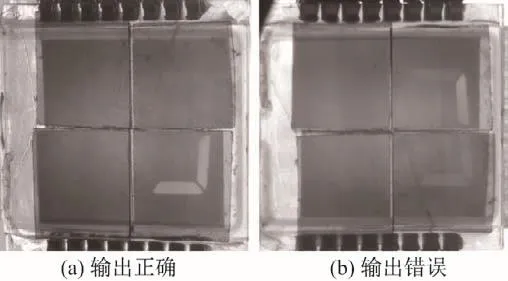

重构指令标识了唯一特定的基元[4].对于重构指令为11001001的基元,其主光路被重构选择为VV类型,对其设计的6个实验用例如表4所示.在这6个测试用例中,每个错误数据位段注入到一个基元(BOU0,BOU1或BOU2)中.以表4中的用例1为例,对BOU1注入错误的重构指令11010001,且保持其主控光路编码数据均为正确的10和01,与此同时BOU0和BOU2的重构指令以及主控编码数据值都注入正确.在这种情况下,BOU0和BOU2的VV主光路都输出垂直偏振光,而BOU1的VV主光路输出无光.经过VV区的表决,表决器的2A笔段高亮显示(如图10(a)所示).而在BOU0,BOU1和BOU2重构运算的3个数据都正确注入的情况下,VV区主光路数据的TMR表决效果如图10(b)所示,其中表决器的2A和2F笔段高亮显示.

在所有18个基元的表决用例测试中,基元的主光路均被重构为VV,HV,VH或HH 4种类型中的一种.为了更一般地讨论实验效果,在以下实验结果分析中,还以注入重构指令位段为例,介绍了HV,VH和HH 3个表决区在重构指令正确与失效情况下的表决效果.

重构指令为01001100的系统基元重构选择HV型主光路.当3个基元的重构指令都输入正确,并且对3个基元的主控光路编码分别赋10和01值时,主光路将输出垂直偏振光,TMR表决效果如图11(a)所示(HV表决区中表决器的3A和3B笔段高亮显示).当对BOU1注入错误的重构指令01000100时,BOU1的主光路输出无光,此时HV表决区中表决器的3A笔段高亮显示,表决效果如图11(b)所示.

表4 重构指令为11001001的基元表决实验用例设计Table 4 Test examples of 1-bit processor for BOU with the reconfiguration 11001001

图10 VV型主光路表决效果Fig.10 Voting results of VV-region

图11 HV型主光路表决效果Fig.11 Voting results of HV-region

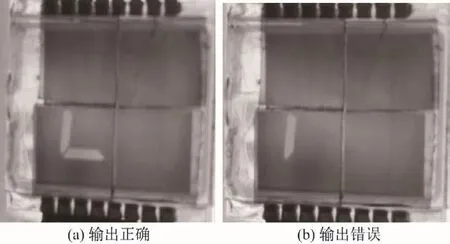

重构指令为10001100的系统基元重构选择VH型主光路.在3个基元的重构指令输入都正确的情况下,对3个基元的主控光路编码分别赋10和11值时,基元主光路将输出水平偏振光,TMR表决效果如图12(a)所示,VH表决区中表决器的2E和2D笔段高亮显示.当对BOU2注入错误的重构指令10011100时,BOU2的主光路输出无光,此时VH表决区中表决器的2E笔段高亮显示,其表决效果如图12(b)所示.

图12 VH型主光路表决效果Fig.12 Voting results of VH-region

重构指令为00010100的系统基元重构选择HH型主光路.当BOU0,BOU1和BOU2重构指令都输入正确,并且对3个基元的主控光路编码分别赋01和01值时,主光路将输出水平偏振光,TMR表决效果如图13(a)所示(HH表决区中表决器的3C和3D笔段高亮显示).当对BOU1注入错误的重构指令00011100时,BOU1的主光路输出无光,此时HH表决区中表决器的3C笔段高亮显示,其表决效果如图13(b)所示.

图13 HH型主光路表决效果Fig.13 Voting results of HH-region

4 可靠性分析

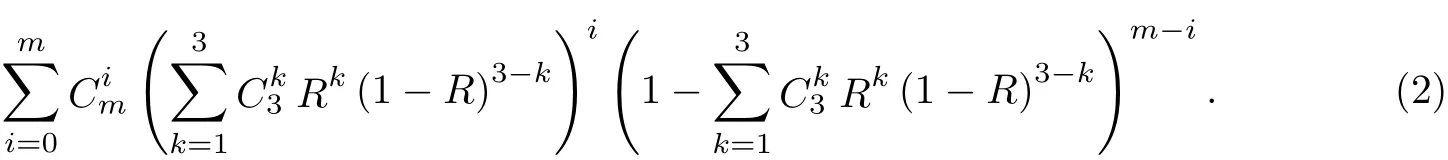

三值光学处理器运算输出的正确性取决于处理器运算单元的重构指令、运算数据性以及硬件性能,即处理器基元只有在重构运算数据和硬件性能强大的基础上才具备可靠运行的可能.设三值光学处理器系统基元重构运算的可靠性因子为R,由硬件不稳定而出错情况的概率为p(0≤p≤1),且因重构运算操作数据出错的概率为q(0≤q≤1),此时R=(1-p)(1-q),在单系统下m位的重构运算器的可靠性为

5 结束语

本工作证明了基元的输出空间适用于三模冗余表决,介绍了三值光学处理器三模冗余表决系统的设计与实现,设计了光电结构的表决器,并介绍了建构三值光学处理器三模冗余表决系统的方案与步骤.对一位的三值光学处理器表决实验进行了详细的设计与实现,并对108个表决用例进行了测试,表决实验的结果均屏蔽了单故障出错的情况.由于实验中的光学部件之间紧凑,并且像素之间存在分离的黑线,因此在像素之间不存在光学串扰干扰,只需区分亮和黑状态,而不需要考虑太多的相对灰度级.在一位的处理器表决实验基础上,可以对位数众多的重构运算器的输出进行表决,这种以基元主光路三模冗余表决的方式能消除类似电路中冗余带来的串行干扰问题.最后对m位的重构运算器进行了简要的可靠性估计,可靠性计算与实验结果表明,在基元主光路出现单故障点的情况下,基于TMR的表决系统能提高三值光学处理器运算输出的可靠性与正确性,进而降低重复计算的可能,提升了系统运行效率.