低失调低踢回噪声双尾动态比较器设计*

2019-06-25周万兴王云峰

周万兴, 刘 昱,3, 王云峰,3

(1.中国科学院 微电子研究所 健康电子研发中心,北京 100029;2.中国科学院 微电子研究所 新一代通信射频芯片技术北京市重点实验室,北京 100029;3.中国科学院大学 未来技术学院,北京 100029)

0 引 言

比较器是组成模/数转换器(analog to digital converter,ADC)的重要模块[1],低功耗是ADC的一个重要需求,特别是对于便携式设备,而比较器是Flash ADC中功耗最大的组成部分,所以引入动态比较器[2]。动态比较器的精度经常由输入参考失调电压所决定,包括静态失调和动态失调两部分。其中静态失调最重要的来源是晶体管的随机失配、工艺变量[3]。

预放大器的输入晶体管尺寸的增大会降低动态比较器的输入失调电压,但会增大负载电容,而比较器的前级一般是一个采样保持电路,因此会增大采样保持电路的功耗[4]。闩锁结构的晶体管的失配也是输入失调电压的一个来源,它被预放大器的增益所减轻。然而预放大器增益的提高会降低比较器的速度[5]。

比较器的输出节点在再生阶段较大的电压变化通过寄生电容对输入电压造成的干扰,称为踢回噪声。踢回噪声改变了动态比较器的跳变点从而降低了ADC的线性度以及信噪比。踢回噪声的降低通常通过降低预放大器输入管漏端的电压摆幅或在比较器的输入和输出之间添加高阻抗通路来实现[6]。

本文介绍了一种增大预放大器的增益以实现低输入失调电压的技术,通过在预放大器的输入和输出之间添加一个高阻抗通路来降低踢回噪声。

1 传统双尾动态比较器

图1(a)为传统双尾电流电压比较器[7]。当时钟信号clk为高电平,比较器处于预充电阶段;clk为低电平,进入比较阶段。预放大器的高增益降低了闩锁结构晶体管的输入参考失调电压和传播延迟,但增大了预放大器的传播延迟。

比较阶段的工作状态分为两个部分:1)预放大阶段:部分是从刚开始进入比较阶段到闩锁结构开始进入再生状态的开始点之间,再生状态的开始点是闩锁结构的其中一个输出节点的放电量达到PMOS阈值电压;2)决定阶段:从进入再生状态到输出稳定。预放大器的小信号增益为

(1)

可以看出,预放大器的增益受IM1的影响较大,而IM1的大小又与晶体管 M1~M3的尺寸以及输入信号的共模电压有关,晶体管M2,M3的尺寸通常会设置为较大尺寸以降低失调电压。对于M1管在尺寸的选择上存在一个关于预放大器增益和比较器延迟的权衡问题,如果M1管的尺寸增大,尾电流也会增大,预放大器的增益降低,使得比较器的延迟降低,而输入失调增大;如果M1管的尺寸减小,那么尾电流也会减小,预放大器的增益增大,使得比较器的延迟增大,输入失调降低。对于高速应用领域,M1管的尺寸应该设置为较大,但将导致输入失调电压增大,从而使得ADCs的分辨率降低。因此,需要一个改变结构来降低失调电压。

2 本文所提出的动态比较器

为得到一个高速低失调电压的比较器,本文提出了如图1(b)所示的电路结构,一对晶体管以交叉耦合的方式级联到输入晶体管以增加预放大器的增益。

图1 二种双尾动态比较器

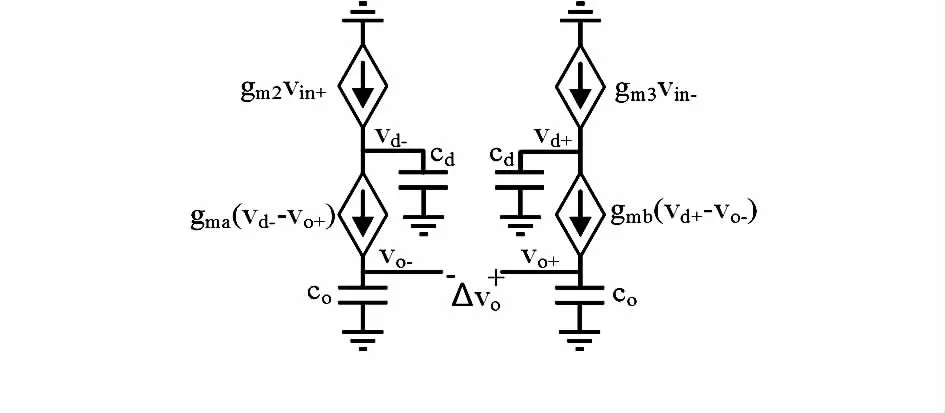

对于差分小信号,本文所提出的比较器的预放大器的增益可以用图2所示的模型进行计算。

图2 预放大器的等效模型

在节点d-,d+,o-,o+运用KCL可得

(2)

由于闩锁结构的输入晶体管的尺寸通常要比预放大器的输入晶体管的尺寸要小很多,所以电容Cd比Co大。所以,方程组(2)可近似解为

(3)

由式(3)可知预放大器的增益得到了巨大提升,即使Cd约等于Co的情况,增益也有较大提升

(4)

对于传统双尾动态比较器和本文所提出的比较器,采取相同的尾电流晶体管尺寸,晶体管Ma和Mb的尺寸设置为与M3和M4相近,使得tamp的值相同。所以由式(4)可以看出,本文所提出的比较器增大了预放大器的增益,从而降低了闩锁结构的失调电压。然而由于级联了一对交叉耦合的晶体管,导致预放大器晶体管的过驱动电压减小,从而增大了预放大器的延迟,降低了M1管的电流。图3所示为传统双尾动态比较器与本文所提出的比较器的预放大器的增益以及输入参考失调电压,随着M1晶体管宽度变化的仿真结果。

图3 预放大器增益和失调电压与M1管宽度的关系

由数学推导分析可知,随着晶体管M1宽度的增加,预放大器的增益应该是减少的,而输入失调电压是增大的。交叉耦合对的级联增大了预放大器的延迟,但在预放大器的输入和输出之间增加了一个高阻抗通路,从而减小了输入晶体管漏端的电压增益,踢回噪声的影响被显著的降低。

3 仿真结果

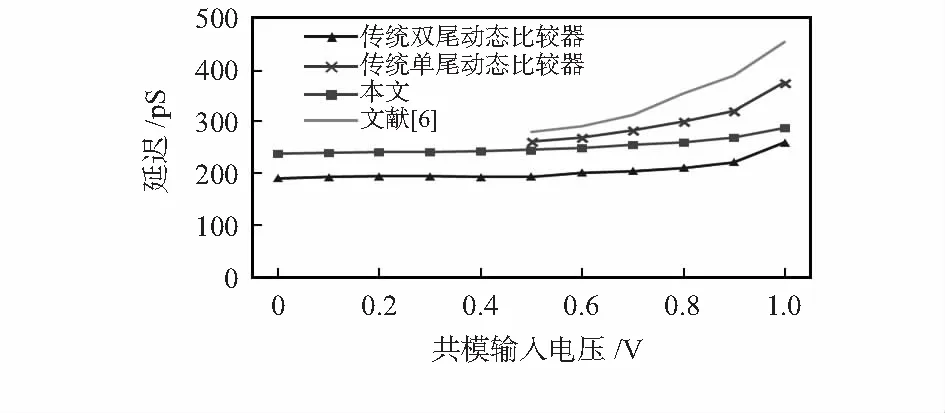

为验证本文所提技术,在TSMC0.18 μm工艺下,对比了其他三种不同的比较器,这四种比较器的输入输出晶体管尺寸和负载电容都相同。四种比较器的延迟特性如图4和图5所示。

图5 延迟特性与共模输入电压的关系

图4所示是在输入共模电压为0.5 V下,4种比较器的延迟与输入差分电压的关系。图5所示是在输入差分电压为50 mV下,4种比较器的延迟与输入共模电压的关系。尽管本文提出的比较器的延迟特性与传统双尾动态比较器相比存在不足,但比传统单尾动态比较器好很多。本文提出的技术增大了预放大器的增益,减少了闩锁结构的延迟,但增加了预放大器的延迟并且减少了预放大器晶体管的过驱动电压和电流系数。

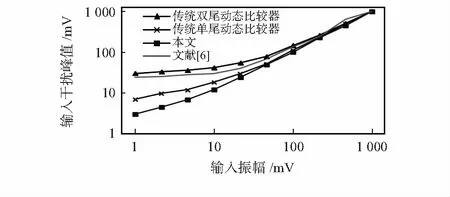

如图6所示是踢回噪声对输入电压的影响,在输入阻抗为10 kΩ时对输入干扰峰值进行了模拟仿真。本文所提出的比较器的踢回噪声非常低,原因是:1)在预放大器的输入和输出之间提供了一条高阻抗通路;2)与输入管级联的交叉耦合对抑制了输入晶体管的漏端电压变化。

图6 踢回噪声对输入振幅的影响

表1为四种比较器的指标,传统双尾动态比较器具有最低的延迟特性,但在给定的功耗条件下,受失调和踢回噪声的影响较大,传统单尾比较器受失调和踢回噪声的影响较小,但是延迟较高。从表中可以看出,本文所提出的的比较器不仅功耗较低,而且降低了输入参考失调电压和踢回噪声。

表1 4种动态比较器的指标

ΔVin=10 mV,Vcm=0.9 V,fclk=100 MHz

4 结 论

本文提出了一种新型低失调低踢回噪声动态比较器。数学分析推导也在0.18 μm工艺条件下不同的仿真中得到了验证。本文通过与其他比较器进行对比,证明本文提出的比较器适用于低踢回噪声、低失调、高速应用领域。