通用任意波形产生模块设计

2019-03-28林沂杰张坤峰

林沂杰,梁 晶,张坤峰

(中国船舶重工集团公司第七二三研究所,江苏扬州225101)

0 引 言

随着雷达技术和电子对抗技术的发展,目前雷达信号仿真对信号的频率、脉宽、功率、调制的控制要求越来越灵活,要求多个参数可以任意组合,对仿真的复杂度和仿真可信度提出了更高的要求。雷达信号半实物仿真,其实质就是通过任意波形产生器在适当的时域、频域、空域产生被试装备所需要的信号,对被试装备的技战指标进行检验、测试、评估。[1]

尽管成熟的商用任意波形产生器有其灵活的波形产生能力,但由于参数编辑复杂,波形文件过大,置频时间长,不能满足高密度仿真、多信号、复杂电磁环境半实物仿真的要求。

随着雷达信号仿真技术的发展,仿真信号波形产生器具备了一定的任意波形产生功能,但大多功能比较单一,结构形式多样,接口繁多,没有统一的标准架构。通用雷达仿真基带任意波形产生模块就是专门针对雷达信号仿真的特点,如切换时间快、脉冲沿陡、波形调制复杂而设计的通用化模块。

1 技术设计

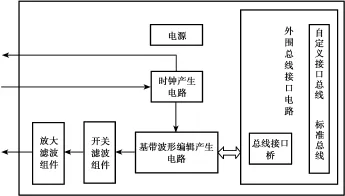

通用雷达仿真基带任意波形产生模块将外围总线接口电路、基带波形编辑产生电路、时钟产生电路、开关滤波组件、放大滤波组件、电源等集成在一个3U壳体内。模块和主机之间通过总线通信,与外围系统通过自定义总线进行系统扩展,所有功能电路、组件相对独立,可以通过更换不同的电路或组件提升系统性能。模块框图见图1。

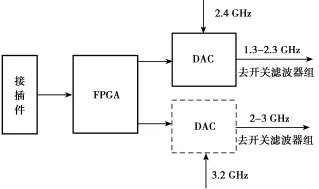

(1)基带波形编辑产生电路由一个FPGA与两片DAC组成。在FPGA上通过编程的方式完成所有基带数字信号的产生,通过DAC以及后端开关滤波组件产生各种所需要的波形,外部接口通过高速接插件和其他组件相连。电路框图见图2,虚框部分表示可扩展功能单元。

图1 模块设计框图

图2 基带波形编辑产生电路图

在本设计中要求2.4 GHz采样率的DAC输出0.1~1.1 GHz/1.3~2.3 GHz 的基带射频信号。 根据采样定理,信号基于每一采样域无限被复制。在理论上,2.4 GHz采样率取第2采样域的信号即可,DAC实际输出1.3~2.3 GHz的基带信号。但是如果不经过特殊处理,信号在高采样域功率和频谱质量远远不能满足实际要求。在变换采样率的情况下,可以改善各个采样域频谱分量结构。对于要求在第1、第2采样域有较好的带内平坦度,可以使用“归零”插值,此时采样率提高1倍,但信号在整个采样域内的功率下降。要求是尽可能提高第2、第3、第4采样域信号的功率,而抑制第1采样率信号的功率,可以使用反向插值或混合插值的方式。反向插值也叫混频插值,其本质就是在采样率提高1倍的情况下将和信号值相反的值插入序列中。这样插入的序列和原始序列频率是一致的,但频谱分量在采样域的分布是不一样的。插值后的序列信号功率在第2、第3采样域功率较高,尤其在第2采样域功率达到最大。[2⁃3]

尽管反向插值在第3采样域信号功率有明显提高,但相对于第2采样域仍有不足。若要求提高更高采样域的信号功率,可以采用混合插值方式。混合插值也叫射频插值,其本质是将原序列某一采样点持续的时间分成多段(一般受DAC带宽的限制,分成3段),第1段为原序列的值,第2段反向插值,第3段归零插值,实现信号的频谱分量尽可能落在高采样域,可以控制每一段的时间改变每一采样域的频谱分量结构。 要实现 2.4 GHz采样率的 DAC 输出 1.3~2.3 GHz的基带信号,实际上就是在100 MHz~1.1 GHz信号序列的基础上进行混合插值,改变采样率,提高第3采样域的信号,抑制其他采样域的信号。

任意波形发生器其核心要求波形任意可编程,具体表现在频率调制、相位调制、幅度调制、脉冲沿形状调制等方面,而用于仿真的任意波形发生器主要体现在频率调制、相位调制、以及部分幅度调制。当然在要求苛刻的场合要求脉冲沿形状调制,由于脉冲沿形状的调制还需采用额外的硬件和采用特殊的方式,在此不作进一步分析和叙述。

无论是频率调制、相位调制、幅度调制都是信号基于时间的函数。在一个调制周期内,可以取1 000个点,即每种调制样式离散成一个1 000点的序列,预先通过加载的方式加载到FPGA的内存中,根据不同的调制周期控制每一点持续的时间,即可获得所期望的波形。所以,波形的设计都是基于自定义方式的。

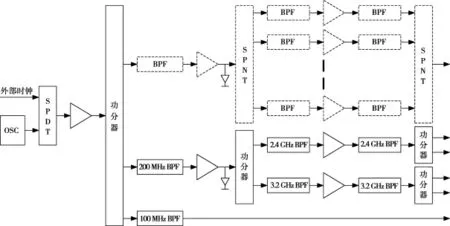

(2)时钟产生电路主要由晶振、开关、功分器、放大器和谐波发生器等组成,其电路原理框图如图3所示,其主要功能为DDS及信号控制模块提供时钟信号和本振信号。

时钟产生电路信号产生过程:对外部时钟或内部晶振放大功分3路,第1路取其谐波信号200 MHz,再经放大器和谐波发生器产生2.4和3.2 GHz本振信号;第2路取100 MHz,为系统提供参考信号;在设计过程中考虑到其他本振信号的使用,第3路为预留通道,方便以后扩展,见图3中虚线部分。

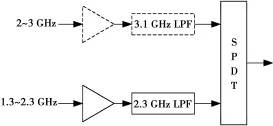

(3)开关滤波组件主要由开关、放大器和带通滤波器等组成,其原理框图如图4所示,其主要功能为DDS及信号控制模块产生的基带射频信号2~3 GHz或 1.3~2.3 GHz进行滤波。

基带射频信号 1.3~2.3 GHz 即是 2.4 GHz 采样率,基带信号100~1 100 MHz取第3采样域的信号。在此过程中也会产生第2采样域的信号1.3~2.3 GHz和第4采样域的信号 2.5~3.5 GHz。 因此,先经带通滤波器进行滤波。为了满足调频带宽50 MHz要求,这里选取 1.275~2.325 GHz带通滤波器。

基带射频信号2~3 GHz滤波器组选取可参考1.3~2.3 GHz基带射频信号。

图3 时钟产生电路原理框图

图4 开关滤波组件原理框图

(4)放大滤波组件主要由放大器、低通滤波器和开关等组成,其原理框图如图5所示,其主要功能为开关滤波组件输出的信号进行放大滤波。

图5 放大滤波组件原理框图

对开关滤波组件输出信号先进行放大,弥补后端低通滤波器和开关插损,再利用低通滤波器对放大信号谐波进行滤除,即可确保输出信号满足指标要求。

(5)外围总线接口电路主要负责与外部通信,通过接插件和基带波形编辑产生电路互联。

2 测试结果

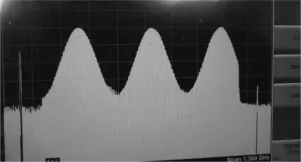

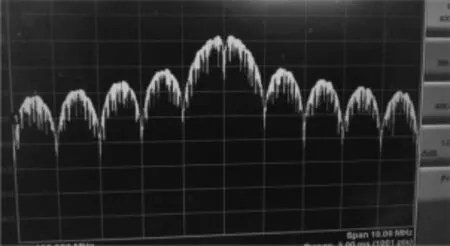

图6~8给出了频谱仪测出的雷达仿真基带任意波形产生模块产生的调幅、调频和调相信号。从图中可看出,产生的信号是理想可用的,达到了设计要求。图6中,横轴为1.36 GHz的扫频带宽,纵轴为每格10 dBm的幅度。图7中,横轴为1.02 GHz的扫频带宽,纵轴为每格10 dBm的幅度。图8中,横轴为10 MHz的扫频带宽,纵轴为每格10 dBm的幅度。

图6 带宽1 GHz、调幅深度40 dBc的调频加调幅信号

图7 带宽1 GHz的线性调频信号

图8 7位巴克码调相信号

3 结束语

本文采用通用雷达仿真基带任意波形产生模块,利用其强大的软件编辑和系统升级功能,实现在一个基带内的频率、脉宽、功率、调制等任意可编程,参数切换时间优于商用任意波形发生器、形成标准模块。该模块应用于雷达信号仿真,可以适应大多数雷达信号仿真的需求,并可以逐步推广到其他领域。