采用硬件加速的宽带数字接收机设计

2019-01-18孔维太全大英金小萍

孔维太,全大英,渐 欢,金小萍,金 宁

(中国计量大学 信息工程学院,浙江 杭州 310018)

在电子战中,侦查接收机往往需要关注以下几个需求,如宽频覆盖、接收机灵敏度和动态范围、多信号并行检测能力、频率分辨率和精度[1-4].现代宽带数字接收机将输入射频信号下变频为中频信号,使用高速模数转换器(analog-to-digital converter, ADC)对其进行数字化后,经数字信号处理器处理.通过提高ADC精度和增加快速傅立叶变换(fast Fourier transformation, FFT)长度可以更好地改善瞬时动态范围(instantaneous dynamic range, IDR).GEORGE等[5]介绍了基于FFT的宽带数字接收机.数字接收机用于多信号检测的信号处理(包括FFT和频谱补偿)时需要对大量数据进行复杂计算和并行处理,信号的实时处理受制于硬件的实现.因此,降低FFT规模的复杂度对于最大限度地降低硬件的集成度和功耗至关重要.然而降低FFT运算复杂度的技术,比如比特截断,不可避免地在FFT各阶段产生误差和损失,从而限制了接收机的IDR性能.并行处理技术的引入改善了通道化数字接收机的实时性能.ZAHIRNIAK等[6]在用于数字接收机的多相滤波器中采用并行技术实时处理.NAMGOONG[7]设计了一种信道化的超宽带数字接收机,该接收机通过将宽带模拟信号分解为子带,实现超宽带信号的有效采样.

随着ADC技术的飞速发展,因分辨率和采样率提高,IDR也随之显著提升.然而,数字信号处理器的处理和存储需求也随之急剧增加.为了加速计算,LI和CHEN[8]使用现场可编程门阵列(field programmable gate array, FPGA)实现了数字接收机设计.同时,图形处理单元(graphics processing unit, GPU)在诸如高性能计算领域得到了广泛应用.SONG等[9]设计了基于GPU平台的雷达接收机.此外,GEORGE等[10]设计了使用NVIDIA Tesla C2050 GPU和Virtex-5 FPGA组成的混合计算平台上实现的雷达接收机,RUPNIEWSKI等[11]设计了基于NVIDIA Tesla K20 GPU和Kintex-7 FPGA的雷达信号处理系统.这些接收机基于FPGA设计又具备了GPU完成复杂运算.

本文设计了一种基于Virtex-7 FPGA的5 Gsps(gigabit samples per second)宽带数字接收机,在动态性能提升的同时,集成度和功耗方面优于前代设计.

本文的研究内容如下:第一部分给出数字接收机的硬件原型的开发方案,分析固件设计中考虑的因素,如数据缓冲策略、并行FFT处理、超分辨率、数据补偿等;第二部分给出仿真和实验测试方法及结果;第三部分是对本设计的总结和展望.

1 宽带接收机设计

1.1 硬件设计和数据接口

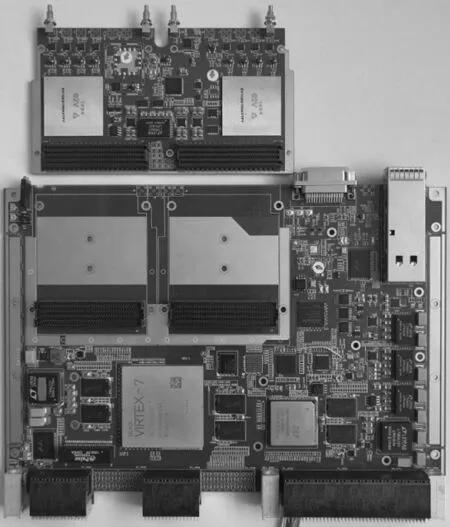

宽带数字接收机原型包含一个采用Xilinx FPGA作为主要计算单元的信号处理载板,以及一个符合VITA 57.1标准的FMC(FPGA mezzanine card)子卡作为ADC处理单元.信号处理载板基于Virtex-7 XC7VX690T FPGA设计,不仅提供了硬件测试环境,还提供了嵌入式处理系统中的通用特性,包括4 GB的64位双通道1866 MTs DDR3内存、独立的数字信号处理器(digital signal processor, DSP)TMS320C6678、连接到背板的8通道PCIe(peripheral component interconnect express)接口、通用I/O接口以及两个400引脚的FMC连接器.ADC FMC子卡提供两个10位高速ADC,可满足两个通道同时工作,最高采样率为5 Gsps.宽带数字接收机原型如图1.

图1 宽带数字接收机原型Figure 1 Digital wideband receiver prototype

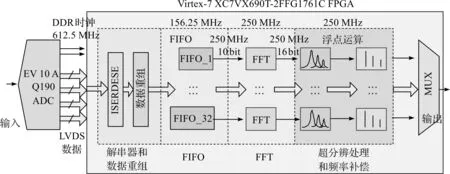

采样信号由E2V EV10AQ190 ADC芯片通过低压差分信号(low-voltage differential signaling, LVDS)以双倍数据速率(double data rate, DDR)输入FPGA.对于5 Gsps采样率,每个ADC具有40对串行DDR数据线,时钟频率为625 MHz.FPGA中的解串器(ISERDES)以1∶8的速率将数据从串行转换为并行,然后将输入的DDR数据流转换为40个时钟为156.25 MHz的单倍数据速率(single data rate, SDR)流.对ADC数据进行解串和重新排列之后,使用两级先入先出(first input first output, FIFO)缓冲器对数据位宽转换和乒乓并行处理.接下来,将32个FIFO的输出结果直接输入到FFT模块.宽带数字接收机体系结构如图2.

图2 宽带数字接收机体系结构图Figure 2 Architecture of digital wideband receiver

1.2 信号处理实现

在实时信号处理时,FPGA的FFT需配置为流水线式的流式I/O架构,虽然在填充管道时引入了初始延迟,但数据在信号处理时没有中断.就FFT所需资源而言,在FPGA上实现全浮点运算所需代价可能非常昂贵,因此,往往采用定点或块浮点FFT运算.由于有限字长效应,在变换过程中会引入噪声,导致输出数据不完全准确.为了保证足够的精度,本文使用块浮点运算.配置块浮点FFT时,需要确定缩放范围以使动态范围最大化.

为了提高接收机检测多个信号的动态性能,引入了超分辨率算法和数据补偿技术.超分辨率算法通过比较两个相邻频率谱线的峰值来估计待检测信号的确切频率.数据补偿技术采用预先计算的峰值幅频响应的FFT结果,通过查找表(look-up-table, LUT)和坐标旋转数字计算(coordinate rotation digital computer, CORDIC)算法迭代实现.从实际响应中减去该响应,就可以实现旁瓣消除,从而提高弱信号捕获能力以供进一步检测.在这一步中,计算精度对于超分辨率频谱估计至关重要,因此,本文使用单精度浮点计算来估计实际频率分辨率并准确地补偿数据.

2 实 验

2.1 FPGA资源

基于FPGA加速的数字接收机设计需要考虑的基本要素是运算速度、精度和消耗的资源[逻辑资源(slice),块存储(block RAM),乘法器(multipliers)等].

在实时处理中,并行数据缓冲和FFT计算是必要的.并行处理模块的数量主要取决于内部FPGA的ADC采样速率fs和工作时钟频率fop.FFT的IP核配置为流水I/O模式,该模式在连续输出时受初始延迟影响.

并行处理模块数N可以按下式计算:

N=fs/fop.

(1)

将参数fs=5 Gsps和fop=156.25 MHz代入式(1),得到并行处理模块数N的值为32.

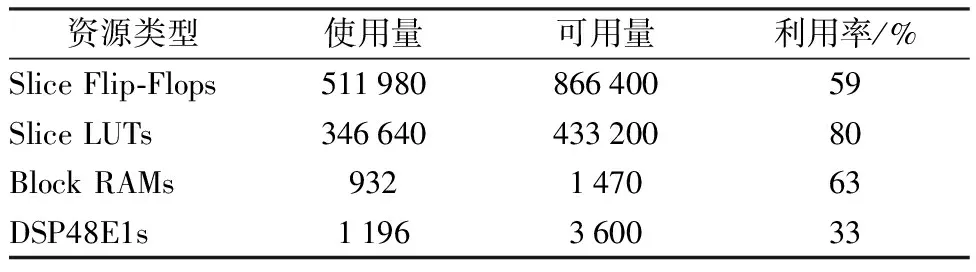

宽带数字接收机采用IEEE标准Verilog HDL与Xilinx提供的IP核(intellectual property core)相结合的方式在Virtex-7 XC7VX690T FPGA上开发.接收机在实时处理时设计保证在下一组缓冲数据处理之前完成当前数据处理工作.FPGA资源消耗如表1,该设计消耗了59%的专用逻辑寄存器,80%的查找表,63%的Block RAM和33%的DSP48E1单元.其中超分辨率算法的实时处理采用逻辑资源与DSP48E1相结合的方式降低资源消耗.

表1 FPGA资源消耗Table 1 FPGA resource consumption

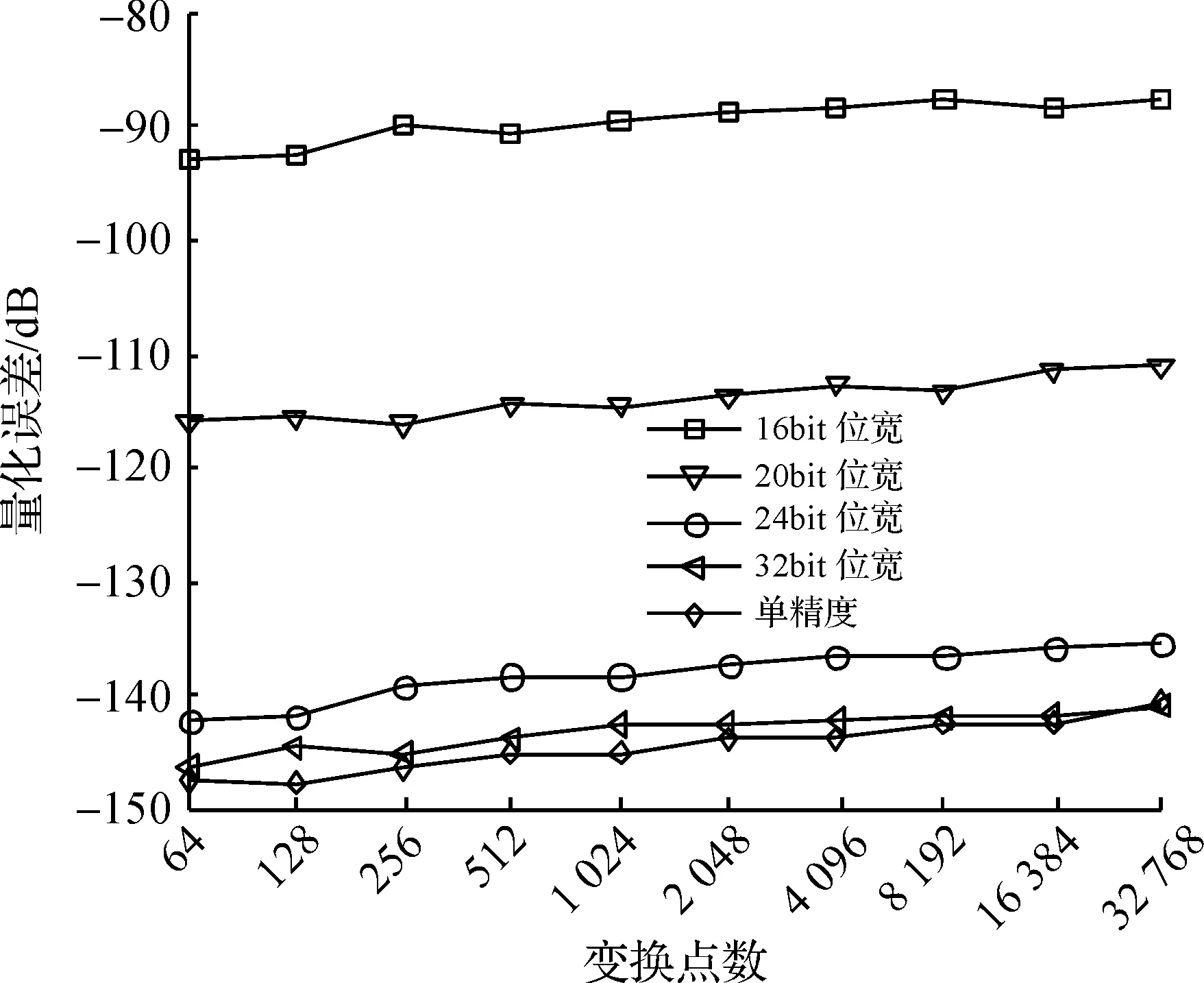

2.2 FFT量化

FFT模块使用块浮点运算来实现.FFT的IP核具有精确的C模型和matlab混合编程功能,专为系统建模而设计.FFT IP核输出的结果与matlab建模完全一致.输入数据和相位因子的位宽取决于可接受的噪声性能和资源消耗.本文对块浮点和单精度浮点FFT之间的误差进行了初步研究.为了精确计算和分析误差信号,使用随机脉冲(在幅值和频率上均随机)量化为10位的输入信号模拟ADC的量化噪声,并重复100次模拟求均方根(root mean square, RMS)误差的平均值.设置不同FFT点数、不同量化数据和相位因子位宽的误差结果如图3.

16 bit位宽的输入数据和相位因子足以满足ADC中有效位数(effective number of bits, ENOB)为8 bit的FFT计算.对于更高的ADC分辨率,FFT的输入数据和相位因子的位宽应设置得更宽.

2.3 采样性能测试

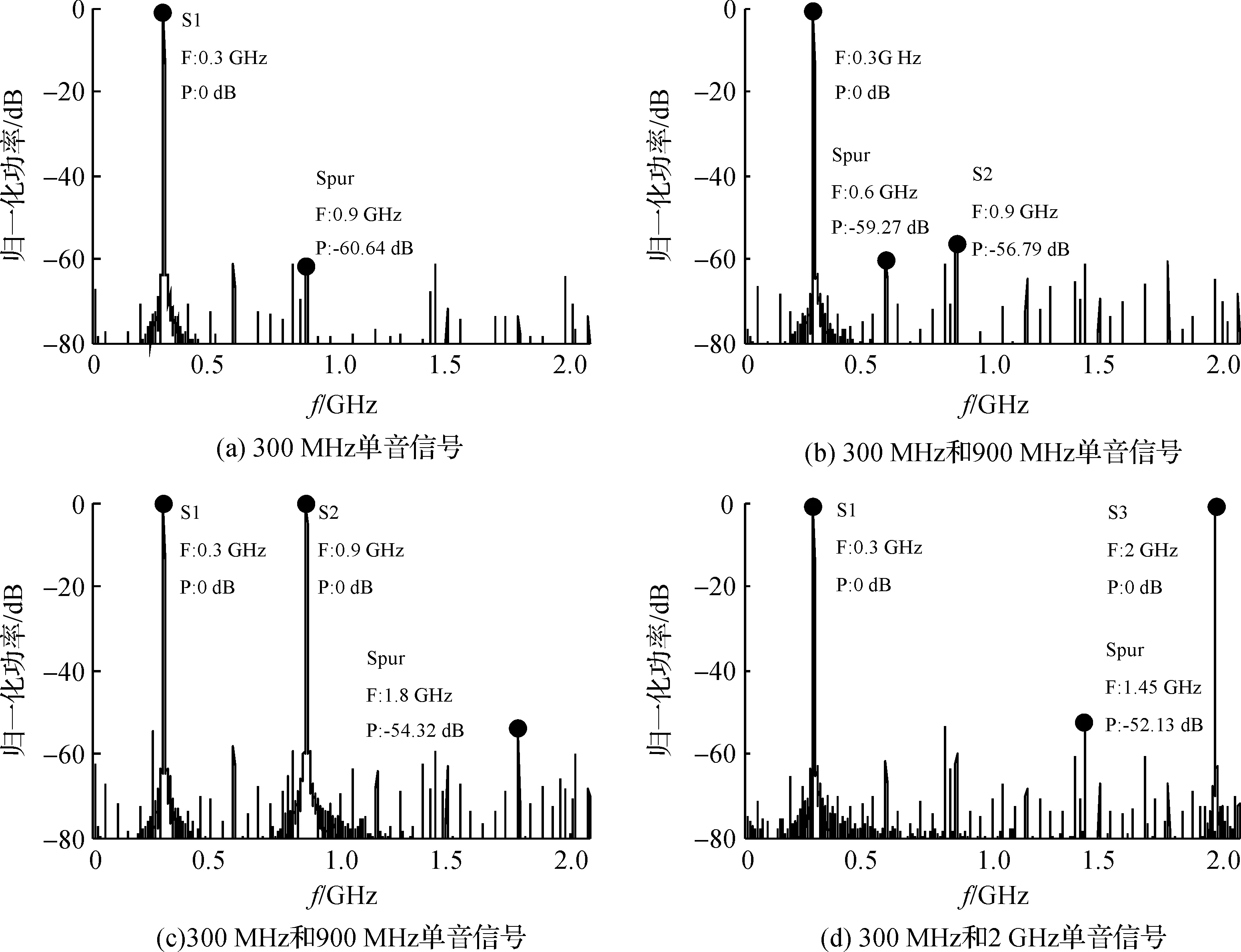

本节通过实验测试数字接收机的动态范围和IDR.为了确定接收机的实际性能,使用矢量信号发生器Agilent E4438C产生具有不同功率和频率的信号并将其发送至数字接收机的ADC.通过改变在2 GHz带宽内信号的功率和频率,测试IDR性能.

图3 噪声性能比较(10位量化)Figure 3 Comparison of noise performance(10 bit quantification)

图4 单音信号测试Figure 4 single tone signal test

图4给出了在四种情况下接收机的信号频谱(输入为单音信号),其中图中标出的Spur为采集得到的最大寄生信号.在图4(a)中,输入频率为300 MHz的单音信号S1,接收机的动态范围可达60 dB;在单音信号S1的基础上叠加频率为900 MHz、相对功率-56 dB的单音信号S2效果如图4(b);图4(c)中的两个单音信号S1和S2的功率均接近接收机满量程,其动态范围减小到54 dB;叠加单音信号S1和2 GHz的单音信号S3,如图4(d)所示,动态范围下降到52 dB.

图4仅给出了部分测试结果,完整的实验表明,本文提出的宽带接收机最大IDR为52 dB,验证了设计的有效性.

3 结语

本文在硬件加速的前提下实现了对5 Gsps宽带接收机的设计和性能评估.在本设计中,采用了更高分辨率的ADC,并在FPGA上实现了计算密集型的处理任务.该设计不仅增加了接收机带宽,而且大幅度提高了IDR和多信号检测能力.在2 GHz带宽内同时检测2个信号时,最大IDR为52 dB.接收器的性能可以通过以下方式得到增强:

1)更好的通道失配校准算法.因为E2V EV10AQ190 ADC芯片交错采样时存在通道失配,需要采用更好的通道失配校准算法提高采样性能.

2)更高的采样率和更高的ADC精度,可以获得更广的频率覆盖带宽和更高的信噪比.

3)更长的FFT点数进行频谱分析,可以增加信号的积累并提高接收机的有效接收通道宽度.

4)更高的并行信号处理能力,可以通过更高性能的FPGA实现.进而可以在给定的一组数据中检测更多的信号,并在紧凑的设计中集成更多的通道.