一起合并单元故障引起的保护误动事故分析∗

2019-01-09周文越李霞

周文越,李霞

(1.国网四川省电力公司电力科学研究院,成都610072;2.国网成都供电公司,成都610041)

0 引 言

合并单元作为智能变电站过程层设备之一,用以对来自电压或电流互感器的数据进行时间相关组合[1-2],并将组合后的数据按照特定的格式发送给继电保护、故障录波等站控层设备。合并单元故障可能导致其输出的采样值报文与实际不符,从而引发继电保护误动、拒动等一系列严重问题[3-4]。文章对某110 kV变电站主变保护误动事件进行了分析[5],通过事故现场的加量试验和波形分析,确定了事故是由合并单元输出的采样值报文异常引起的,并推测采样数据负半波的符号位被清零造成了异常的采样值报文,在此基础上通过改写合并单元内部代码、合并单元硬件结构分析,确认了推断的正确性。最后,分析了故障合并单元的硬件结构,并指出了其设计缺陷。

1 事故简述

某110 kV变电站一次接线图如图1所示,该站为内桥接线,110 kV I线151开关运行,桥开关150运行,110 kV II线152开关热备用。1号、2号主变并列运行。

图1 某11 0kV变电站一次接线图Fig.1 One 110 kV substation primary electric wiring diagram

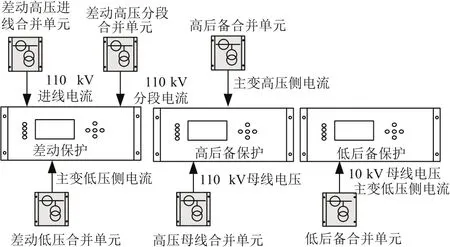

该站的主变独立配置差动保护和后备保护,且差动保护和后备保护配套的合并单元也是独立配置的。主变保护及其合并单元配置如图2所示。

图2 主变保护及其合并单元配置图Fig.2 Configuration diagram of main transformer and its merging unit

某日,在一次设备无任何故障的情况下,2号主变低后备保护限时速断1时限1 505 ms出口,跳10 kV分段930开关,限时速断2时限1 806 ms出口,跳主变低压侧902开关,导致该站10 kV二段母线失压。

2 事故分析

2.1 保护动作情况

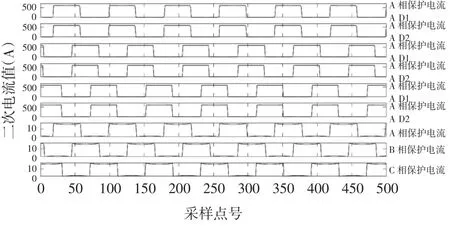

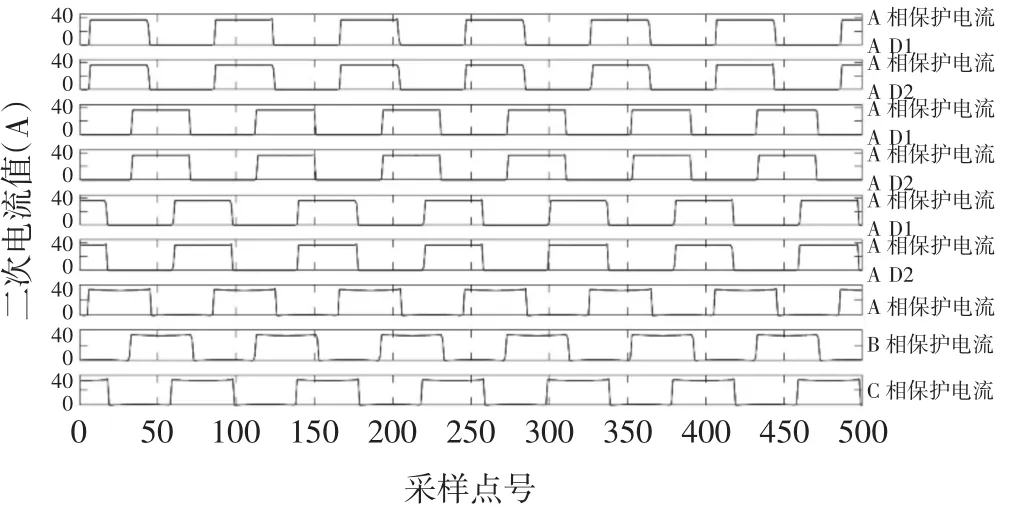

2号主变低后备保护动作时,故障录波器中2号主变低后备保护合并单元的电流波形如图3所示。从图3中看出,合并单元发出的两路保护电流(AD1和AD2)的方波和测量电流均突变为仅有正半波的方波,频率为50 Hz,且每个方波的幅值一致,保护通道二次电流幅值约为596 A,测量通道二次电流幅值约为16 A。故障时的电压与正常运行时的电压一致,未在图3中展示。

图3 2号主变低后备保护合并单元录波Fig.3 Recorded waveforms of No.2 main transformer low voltage back up protection merging unit

2号主变的限时速断为不带方向的纯过流保护,不经电压闭锁,其动作电流定值为27.5 A,一时限1.5 s跳10 kV分段开关,二时限1.8 s跳主变低压侧开关。因此保护的动作行为与整定值一致。

结合保护的动作情况和保护录波,可初步判断:在本次事故中,保护动作正确,2号主变低后备合并单元三相电流突变造成了此次保护误动。

2.2 事故现场处理

检修人员到达现场后,断开了合并单元的外部交流回路,通过测试仪对合并单元施加额定电流(1A),合并单元输出的波形与故障时相似。随后,对装置的CPU插件进行了软重启,加入额定电流后,异常波形依然存在。最后,把采集插件进行带电插拔后(模拟采集插件重新上电),再次加入额定电流,合并单元输出的数据恢复正常。

2.3 故障波形分析

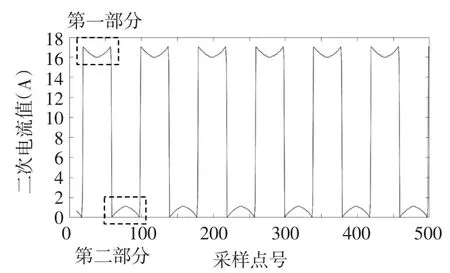

考虑到测量电流的精度高于保护电流,对故障时合并单元输出的A相测量电流波形放大进行分析,如图4所示。可看出每个周期的波形包含两个部分,第一部分类似正弦波的负半波叠加直流分量,第二部分类似正弦波的正半波。

图4 2号主变低后备合并单元A相测量电流Fig.4 Recorded waveforms of No.2 main transformer low voltage back up protection merging unit phase A measure current

进一步将图4虚线框中的两部分波形进行局部放大,如图5所示。

图5 局部放大后的A相测量电流Fig.5 Recorded waveforms of local enlarged phase A measure current

将第一部分与第二部分别与正常情况下2号主变低后备合并单元输出的负荷电流波形的负半波和正半波进行对比,对比结果表明,两者基本一致。

2.4 事故原因分析

在进行事故原因分析之前,简单介绍计算机对正负数的存储方式。在计算机中,二进制数是以补码[6-7]的形式进行存储的;最高位规定为符号位;正数的符号位为0,负数的符号位为1。正负数的二进制补码表示方法如式(1)所示。

根据以上原则,十进制数+3对应的八位二进制数补码为00000011;如果是-3,其补码就是11111101。

因此,可以看出,若负数补码的符号位突变为0,则该负数转换为十进制后,就会变为很大的正数。例如,若11111101变为01111101,则其表示的十进制数将由-3变为+125。

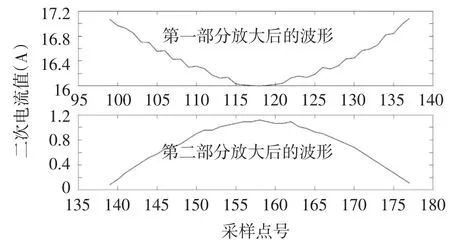

对于文中的案例,根据其波形图的特征并考虑二进制数符号位被改写后的特征,可推断,合并单元输出数据的最高位(符号位)可能被改写。为验证该推断,修改合并单元FPGA程序,在FPGA寄存器中把所有获取到的采样值最高位(符号位)清0。修改之后,在合并单位中加入电流,得到的波形与故障波形形状相似,如图6所示。

图6 修改FPGA程序后2号主变低后备保护合并单元录波Fig.6 Recorded waveforms of No.2 main transformer low voltage back up protection merging unit after changing FPGA program

2.5 事故内部原因分析

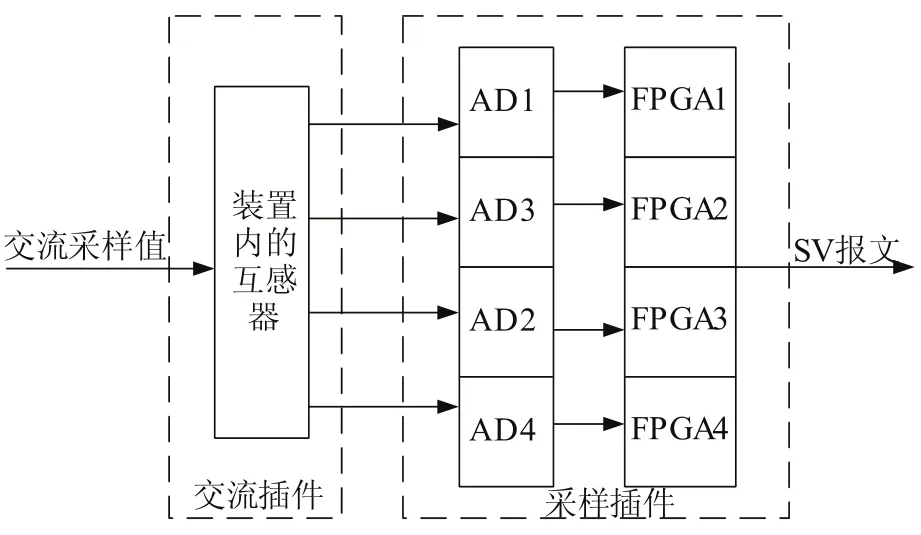

合并单元装置数据采集回路由交流插件和采集插件组成,分别完成模拟量采集和A/D转换功能。合并单元硬件结构如图7所示。

图7 故障合并单元硬件结构Fig.7 Hardware structure of trouble merging unit

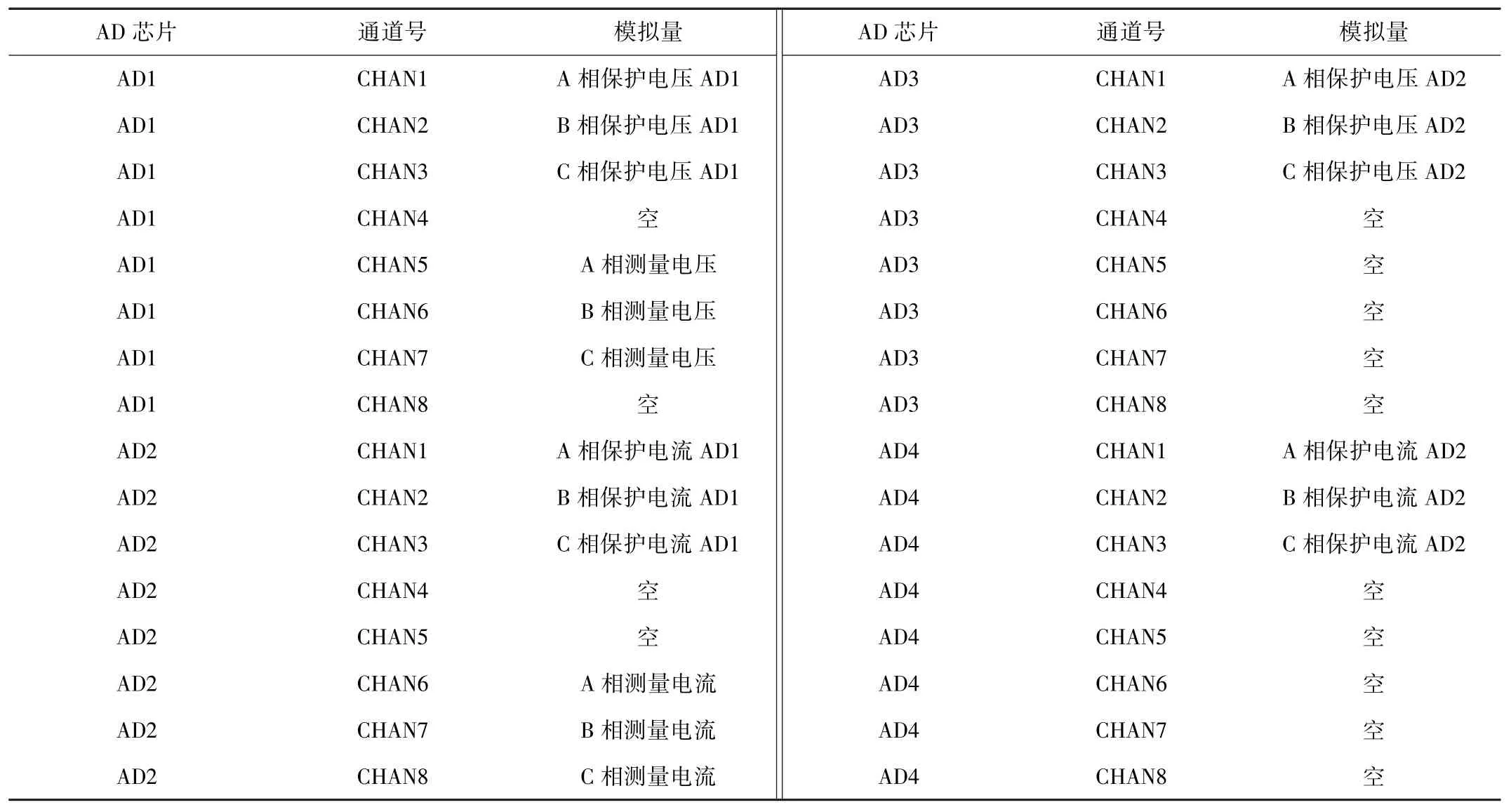

从电流、电压互感器出来的交流电压电流首先进入合并单元的交流插件,交流插件中的互感器将交流电压电流变换为合并单元可处理的交流量,随后,变换后的交流量进入采样插件进行A/D转换和报文打包。其中AD1~AD4为4个独立的A/D转换板卡,负责对交流量进行A/D转换,FPGA负责对A/D转换后的采样值按照IEC 61850规定的报文格式进行打包。4个A/D通道的分配如表1所示。

在本次事故中,波形出现异常的通道是三相保护电流AD1和AD2、三相测量电流。这9个波形异常的通道使用了AD2和AD4两片完全独立的芯片。考虑到,在同一时刻,两片完全独立的芯片,发生同样故障的概率几乎为零。因此,故障不应该是由A/D转换环节引起。

在FPGA中,采样值被打包成固定格式的SV报文,在此环节中,仅有一块FPGA芯片在运行,因此可以推断,故障的原因为采集插件中FPGA某些门电路失效,导致FPGA工作异常,采样数据的符号位被清0,输出异常波形。在文章的2.4节中,修改FPGA程序后,得到的波形与故障波形一致,也侧面印证了此原因。

在2.2节中的现场处理环节中,可看到故障现象在装置重启后消失,因此可推断FPGA的故障应该属于硬件软故障。文献[8-10]提到,单粒子翻转现象导致芯片局部失效是FPGA芯片软故障的典型原因。单粒子翻转是指大规模集成电路在受到空间粒子干扰等情况下,器件逻辑状态翻转,原来存储的"0"变为"1",或者"1"变为"0",从而导致系统功能紊乱,重新上电后故障现象消失。

对于文中的故障合并单元,FPGA程序由FLASH加载到SRAM中后,FPGA根据加载到SRAM中的连线配置运行,当SRAM出现单粒子翻转故障后,就会导致连线错误,使某些电路失效,从而导致程序出现异常,重新上电加载程序后功能恢复正常。

表1 A/D通道分配表Tab.1 Distribution of A /D path

2.6 合并单元结构分析

为保证采样的可靠性,目前的合并单元中的保护通道均采用双A/D转换设计,一路保护用二次电流或电压进入合并单元后,通过双A/D转换,合并单元发出两路保护用的SV采样值。对继电保护装置来说,其启动元件和保护动作元件分别使用不同通道的SV采样值,若两路采样值不一致,则相关保护功能将被闭锁。此机制将保证,在由合并单元异常导致某一路SV采样值异常的情况下,保护不会误动作。

但各设备生产厂家对双A/D的理解和执行存在一定问题。如文中的合并单元,虽然在A/D转换环节实现了双通道独立,但是在报文打包环节,处理芯片未相互独立。导致在此环节,若芯片出现故障,极有可能导致双通道采样值同时异常。在这种情况下,保护装置所采集到的两路SV同时发生异常,保护装置将判断SV正常,从而进入逻辑判断环节,最终导致保护误动。

由此可见,对于合并单元,采样值处理的每个环节都应该相互独立。因此,最佳的合并单元硬件结构应如图8所示。

图8 优化后的合并单元硬件结构Fig.8 Optimized hardware structure of merging unit

3 结束语

分析了一起合并单元故障引起的保护误动事故,并由事故引出目前合并单元设计上的缺陷。合并单元作为智能变电站继电保护系统的数据来源,其重要性不言而喻,设备生产厂家应对文中提到的合并单元设计缺陷引起重视,在设备研发过程中,充分考虑硬件结构,提高合并单元的可靠性。另外,文章在事故原因的分析中还存在一些不足,由于涉及芯片级的原理,且缺乏理论基础和试验手段,并未对单粒子翻转引起FPGA电路失效的原理及诱因进行深入分析,下一步将对此进行进一步的研究。