基于RTD的新型D锁存器设计

2018-11-26姚茂群冯杰沈珊瑚

姚茂群,冯杰,沈珊瑚

(杭州师范大学 国际服务工程学院, 浙江 杭州 311121)

共振隧穿二极管(resonant tunneling diode,RTD)是利用量子共振隧穿效应工作的一种较成熟的量子器件和纳米电子器件[1-2]. 在室温下,RTD因具有独特的负内阻(negative differential resistance, NDR)特性及皮秒量级的开关转换速度,非常适用于高速低功耗数字集成电路. 相较于传统的CMOS(complementary metal oxide semiconductor,互补金属氧化物半导体)器件,RTD的电路结构简单,所用器件数量少,功耗低[3-4].

单双稳态转换逻辑单元(MOno-stable BI-stable transition logic element,MOBILE)是基于RTD电路的一个重要逻辑单元,能实现丰富的逻辑功能[5-6]. 在时序电路领域,由RTD构成的多种结构简单的D触发器已被实现,如SCFL(source coupled FET logic,源耦合场效应晶体管逻辑)接口的D触发器[7]和CML(current-mode logic,电流型逻辑)类型的D触发器[8]. 由RTD构成的D锁存器结构较复杂,目前并不多见[9]. 本文将基于MOBILE的工作方式和输出控制方式,结合RTD自身的负内阻特性,设计一种结构简单的D锁存器.

1 MOBILE的2种工作方式

RTD的电流电压特性曲线如图1所示,Ip和-IP分别为正向和负向波峰电流,IV和-IV分别为正向和负向波谷电流,Vp和-Vp为正向和负向波峰电压,VV和-VV为正向和负向波谷电压[10]. 当RTD正向偏置电压从0开始增大到Vp时,电流逐渐从0增至Ip,该区域称为RTD的第一正阻区;当电压继续增至VV时,电流反而减至波谷电流IV,该区域称为RTD的负阻区;电压继续增大,电流也随之增大,呈现普通二极管的正向特性,称该区域为RTD的第二正阻区. RTD负向电流电压曲线与正向近似并关于原点对称,只是-IP和-IV的绝对值较正向稍小一点,-Vp和-VV的绝对值与正向值接近.

图1 RTD电流电压特性曲线Fig.1 Current and voltage characteristic curve of RTD

基于RTD的MOBILE如图2所示[5-6],由2个RTD串联而成,一个是RTD负载管,另一个是RTD驱动管,V为偏置电压,A为RTD的单位面积. 当RTD电流密度一定时,RTD的波峰电流和波谷电流与其面积成正比,但RTD的波峰电压和波谷电压基本不随其面积的改变而变化. MOBILE也可由更多个RTD串联而成. 本文通过2个RTD串联的MOBILE进行电路设计. MOBILE主要有2种工作方式: 上升沿触发和高电平触发.

图2 MOBILEFig.2 MOBILE

1.1 上升沿触发

上升沿触发是MOBILE的一种常见工作方式[11]. 其偏置电压V为时钟电压,电路在上升沿时,产生需要的输出. RTD负载管和RTD驱动管需要同时满足2个条件: RTD负载管波谷电流小于RTD驱动管波峰电流和RTD负载管波峰电流大于RTD驱动管波谷电流. 工作原理如图3(a)和(b)所示. 当V较小时,RTD负载管和RTD驱动管的工作状态都处于第一正阻区,此时,电路只有一个稳定状态S0点(见图3(a)),输出低电平;当V继续增大并超过RTD波峰电压的2倍时,电路有2个稳定状态:S1和S2点(如图3(b)所示).处于S1还是S2状态,具体要看RTD负载管和RTD驱动管中的波峰电流,波峰电流较小的先进入负阻区,呈现较大的阻抗,此时,电路处于双稳态. 在图2中,由于RTD驱动管波峰电流较小,电路处于S2稳定点,输出高电平. 当V保持高电平时,电路输出保持不变,此时,电路具有自锁功能.

图3 上升沿触发工作原理Fig.3 Rising-edge triggered working principle

1.2 高电平触发

高电平触发是MOBILE不常用的一种工作方式,但在某些数字电路,如触发器、锁存器等电路设计中,发挥着重要作用[12]. 在高电平偏置电压V下工作,RTD负载管和RTD驱动管需满足: RTD负载管波峰电流小于RTD驱动管波谷电流或RTD负载管波谷电流大于RTD驱动管波峰电流,工作原理如图4所示. 当V接高电平且RTD负载管波峰电流小于RTD驱动管波谷电流时,RTD负载管的电流电压曲线如图4的实线所示,由于电路只有一个稳定点S1,所以输出低电平;当V接高电平且RTD负载管波谷电流大于RTD驱动管波峰电流时,RTD负载管的电流电压曲线如图4的虚线所示,电路也只有一个稳定点S2,所以电路输出高电平.

图4 高电平触发工作原理Fig.4 High-level triggered working principle

2 MOBILE的输出控制方式

图5 2种输出控制方式Fig.5 Two output-control modes

为有效控制MOBILE的输出,常用做法是加入三端控制器件,如HEMT(high electron mobility transistor,高电子迁移率晶体管)、HBT(heterojunction bipolar transis,异质结双极晶体管)、HFET(heterojunction field-effect transistor,异质结场效应晶体管)等[13-15]. 常见的输出控制方式有2种: 三端器件直接与RTD并联[16]和三端器件与RTD的串联结构和RTD并联[17]. 以HEMT为例,2种输出控制方式分别如图5(a)和(b)所示. 在图5(a)中,HEMT与RTD驱动管并联,记与RTD驱动管并联的区域为NDR,输入信号D通过HEMT栅极输入. 由于NDR区域的电流电压特性曲线与RTD相似,NDR区域的波峰电流受D控制,当D为高电平时,HEMT导通,NDR区域的波峰电流为此时HEMT的电流与RTD驱动管波峰电流之和;当D为低电平时,HEMT截止,NDR区域的波峰电流为RTD驱动管的波峰电流. 通过适当调节RTD负载管和RTD驱动管的面积和HEMT参数,便可由输入信号D控制电路的输出. 当然,也可将HEMT与RTD负载管并联,或者并联更多个HEMT. 在图5(b)中,HEMT与RTD的串联结构和RTD驱动管并联,同样记与RTD驱动管并联的区域为NDR,输入信号D通过HEMT栅极输入. 此时,当D为高电平时,NDR区域的波峰电流为RTD驱动管的波峰电流和与其并联的RTD的波峰电流之和;当D为低电平时,NDR区域的波峰电流为RTD驱动管的波峰电流,从而达到控制整个电路输出的目的. 三端器件直接与RTD并联的控制方式主要应用在逻辑结构简单的电路上,优点是使用较少的器件便可实现所需的逻辑功能,缺点是需要调节HEMT的参数,使设计变复杂. 三端器件与RTD的串联结构和RTD并联的控制方式主要应用于逻辑结构复杂的电路. 其优点是电路设计时只须改变RTD面积,可忽略HEMT器件对电路的影响,缺点是器件数量增多了.

笔者综合上述2种输出控制方式的优缺点,设计了一种新的RTD控制输出方式,如图6所示. 输入信号D通过RTD1的一端输入,由于RTD的正、负向电流电压曲线关于原点近似对称,当D为高电平时,与RTD负载管并联的区域波峰电流增加,增加值约为此时RTD1的波峰电流;同理,当D为低电平时,与RTD驱动管并联的区域波峰电流增大,增大值约为此时RTD1的波峰电流,以此来控制电路的输出. 这种输出控制方式的优点在于: 充分利用了RTD电流、电压的正、反向特性;无须使用面积较大的三端器件即可控制MOBILE的输出;只须考虑RTD的面积,电路设计更加方便. 缺点在于: 利用MOBILE设计电路时,无法通过该输出控制方式实现所有的逻辑功能,如反相器. 但在设计某些特定逻辑功能电路时,有较大优势,如同相器.

图6 RTD控制输出方式Fig.6 RTD control-output mode

3 新型D锁存器设计

虽然上升沿触发的MOBILE在偏置电压为高电平时能保持电路输出不变,具有自锁功能,但偏置电压为低电平时电路输出归0,与传统CMOS的D锁存器逻辑功能不吻合. 为了获得与传统D锁存器逻辑功能相同的RTD电路,电路设计常常较为复杂. 如文献[9]中设计的D锁存器电路(见图7). 造成电路复杂的主要原因是未将MOBILE的2种工作方式相结合,且未利用RTD电流电压的反向特性.

图7 文献[9]中的D锁存器Fig.7 D-latch in [9]

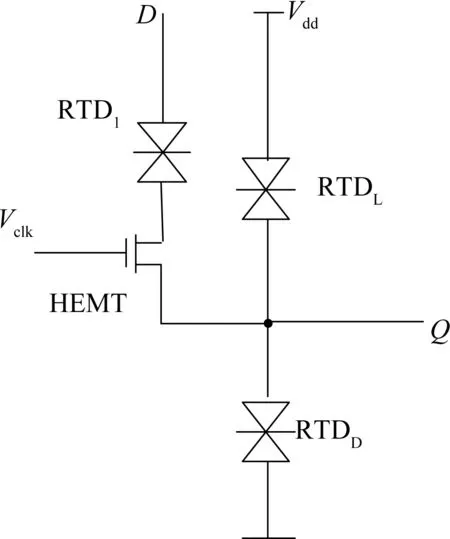

在设计D锁存器时,笔者充分考虑了上述问题,选择偏置电压保持高电平的MOBILE,采用前一节设计的RTD控制输出方式,另加一个三端器件,所设计的D锁存器如图8所示. 其中,Vdd为偏置电压,时钟信号Vclk通过HEMT输入,输入信号D通过RTD1输入,RTD1、RTDL和RTDD需同时满足3个条件: (1) RTD1与RTDL的波谷电流之和大于RTDD的波峰电流;(2) RTD1与RTDD的波谷电流之和大于RTDL的波峰电流;(3) 当Vclk为低电平时,RTDL和RTDD工作在上升沿触发方式.

图8 D锁存器Fig.8 D-latch

电路工作原理分析: 当Vclk为高电平且D为高电平时,由于电路满足条件(1),此时电路工作在高电平触发方式,且只有1个稳定状态,所以Q输出高电平;当Vclk为高电平且D为低电平时,由于电路满足条件(2),此时电路也工作在高电平触发方式,且只有1个稳定状态,所以Q输出低电平;当Vclk为低电平时,由于电路满足条件(3),且Vdd保持高电平,此时,电路具有自锁特性,故电路Q保持原来的状态不变.

仿真及验证: 对所设计的D锁存器进行HSPICE仿真,采用文献[10]介绍的RTD模型,仿真波形如图9所示. 其中,RTD波峰电压为0.28 V,波谷电压为0.52 V,波峰电流密度为9 kA·cm-2,电容为4 fF·μm-2,单位面积A为2 μm2;HEMT采用耗尽型晶体管,阈值电压为-0.1 V,偏置电压Vdd为0.8 V,时钟信号Vclk高电平为0.8 V,输入信号D为0.8 V的脉冲信号;RTDL和RTDD面积均为0.5A,RTD1面积为3A. 从图9中可以看出,该D锁存器具有正确的逻辑功能,且输出Q的高电平约0.72 V,低电平约0.05 V. 相较文献[9]中的D锁存器,本D锁存器不仅电路结构十分简单,只有3个RTD和1个HEMT器件,而且功耗低,只有51.74 μW,最高工作速度可达约30 GHz.性能比较见表1.

图9 仿真波形Fig.9 Simulation waveform

D锁存器器件数量功耗/μW速度/GHz文献[9]3个非门、1个或门、4个RTD和4个HEMT220.0720本文3个RTD、1个HEMT51.7430

4 总 结

介绍了MOBILE的2种工作方式: 上升沿触发、高电平触发;2种输出控制方式: 三端器件直接与RTD并联、三端器件与RTD的串联结构和RTD并联;1种RTD控制输出方式. 上升沿触发的MOBILE虽具有自锁特性,但当电路的偏置电压为低电平时,电路输出出现归零现象,使得在利用MOBILE设计D锁存器时电路结构变得复杂. 本文采用RTD控制输出方式,并结合RTD及MOBILE的特性,大大简化了D锁存器电路的复杂度,同时提升了电路性能. RTD控制输出方式也可用于某些特定的逻辑功能电路,如同相器等,能提升电路的综合性能.