无线传感网络时钟漂移补偿方法设计与实现

2018-07-31郭天星

禹 健,高 超,郭天星

(山西大学 自动化系,太原 030013)

无线传感器网络(WSN)是由大量分布在空间上的传感器节点通过自组织方式构成的网络[1]。融合了传感器、信息处理和网络通信三大技术,可以实现数据的采集、处理和传输。广泛应用于环境监测、工业控制、国防军事等领域[2]。时钟同步是无线传感器网络不可或缺的一部分,测距定位、多传感器的数据融合以及协同工作等方面的应用都离不开时钟同步的支撑[3]。无线传感器网络中的时钟同步是指使网络中所有或部分节点拥有相同的时间基准,目的就是在网络中产生一个全局时钟,使网络内节点的时钟可以达到相对一致性。网络中影响时钟同步精度的因素有很多,主要包括主从时钟的频率不一致、时间戳的精度以及操作系统的延时等。时间戳精度和操作系统延时的影响可以通过基于硬件支持的时间戳标记得以有效解决。一般来说,物理层的抖动延时非常小,在物理层和数据链路层之间的时间戳标记可以获得非常高的时钟精度。而主从时钟晶振的质量、温度、压力、老化程度等都会引起频率的相对漂移[4],时钟同步的精度就与同步周期密切相关,同步周期越小,频率越快,时钟同步精度越高,但相应的功耗也随之增大,对于追求低功耗的无线传感器网络来说,额外的功耗开销是不希望的。

本文将传统的锁相环原理应用到无线传感器网络节点的时钟漂移补偿中,提出一种基于微处理器的时钟漂移补偿锁相环的实现方案,并进行实验验证,证实方案的有效性和可行性。

1 时钟同步

1.1 节点时钟

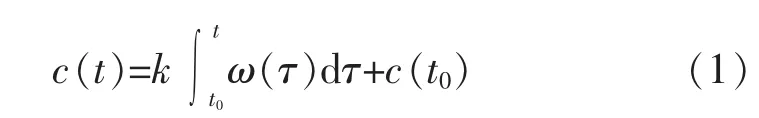

在无线传感网络中,节点的时钟通常使用晶振的脉冲来度量[5]。因此,某一节点在t时刻的本地时钟可以表示为

式中:ω(t)是节点晶体振荡器的频率;k是关于晶体振荡器物理特性的常量;t是真实的时间变量;c(t)与c(t0)分别为t时刻和t0时刻的本地时钟读数。

节点的本地时钟是通过计数器记录晶振产生的脉冲个数构造的。在此基础上,我们可以构造出多种软件时钟。利用本地时钟与同步时钟之间的关系,可以构造出对应的软件时钟以达成同步。

1.2 同步定义

在无线传感器网络应用中,大多数业务的正常运行都要求全网节点间的频率或者时间差异保持在合理的误差范围内,即时钟同步[6]。时钟同步则包括相位同步和频率同步2个概念。相位同步也称为时间同步,是指信号间的频率和相位都保持一致,即信号之间相位差恒定为零。频率同步即维持各节点的频率一致,信号在其相对应的有效瞬间以同一速率出现,以保证所有节点时钟以相同速率运行[7]。

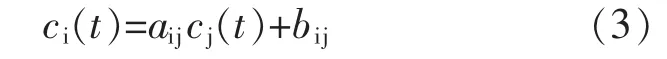

假定晶振的频率在短期内是稳定的,即r(t)=dc(t)/dt是恒定的。 由式(1),节点时钟ci(t)可以简化为

时钟ci(t)与时钟cj(t)之间的关系可以由式(3)表示:

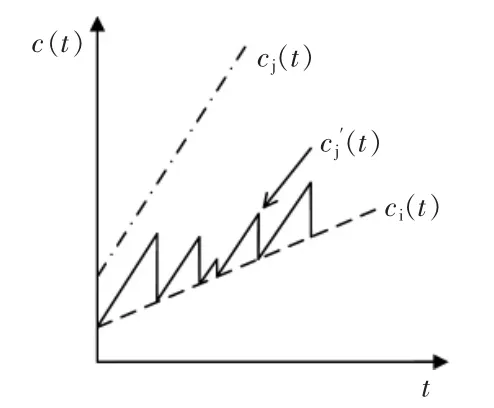

式中:aij为时钟ci(t)和cj(t)之间的相对漂移量,即相对时钟频差;bij为2个时钟之间的相对偏移量,即时钟相位差。对相对漂移量和相对偏移量的补偿是2种基本的时钟同步原理[8]。要实现某一时刻时钟ci(t)和cj(t)的同步,需要求得bij。 图 1 描述了偏移量补偿的过程,时钟cj(t)在一系列同步时刻被同步到时钟ci(t),由此构造出同步时钟cj′(t)。 基于偏移补偿的时钟同步没有考虑时钟漂移对同步精度的影响。 因此,构造的同步时钟cj′(t)与时钟cj(t)在每一个同步周期上有相同的变化速率。如图1所示,同步周期越大,同步误差也就越大。增加同步频率可以提高同步精度,但也会引入相应的开销。

图1 偏移补偿示意Fig.1 Offset compensation diagram

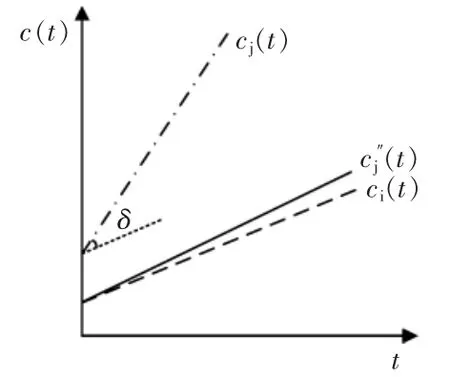

另一种解决途径是对时钟ci(t)和cj(t)相对漂移量进行相应的补偿来减小同步误差。如图2所示,在构造同步时钟时,如果能够得到ci(t)和cj(t)的相对时钟漂移量δ,就可以对时钟漂移量进行人为补偿,同步时钟以接近参考时钟ci(t)的速率变化,而不再依赖本地时钟cj(t)的变化速率。时钟是采用漂移补偿技术构造的同步时钟,如果得到的相对漂移量是比较准确的,那么在很长的同步周期下,同步误差也不会很大。同步误差不再像同步时钟那样与同步周期息息相关。

图2 漂移补偿示意Fig.2 Drift compensation schematic

由此可见,单纯的偏移量补偿只能解决节点间时钟在某一时刻(同步时刻)的相位同步问题,要实现节点间时钟的相位同步需要同时进行相对偏移量和漂移量的补偿。因此,时钟漂移补偿技术在无线传感器节点的时钟同步过程中至关重要,较为准确的漂移补偿技术可以减小同步周期对同步精度的影响,进而减小传感器节点的能量消耗,有助于实现无线传感器网络应用对低功耗的要求。

2 设计思想

2.1 漂移补偿方法

在无线传感器网络的一个广播域内,时钟参考节点(时标节点)以固定频率周期性地广播同步消息,同步消息的发送频率由时标节点的本地时钟驱动,接收节点(被同步节点)用本地时钟记录接收到同步消息的频率。根据二者频率的差值,对被同步节点的本地时钟进行漂移补偿,进而实现二者的时钟同步。

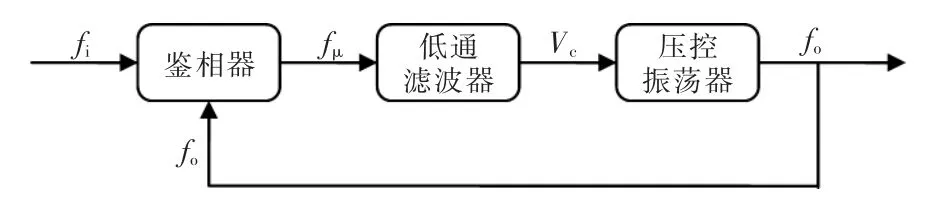

该方法本质上是利用了锁相环的锁频原理进行时钟的频率锁定。为方便论述,首先结合锁相环原理进行补偿方法的介绍。如图3所示,fi和fo分别为时标节点发送同步消息的频率和被同步节点接收到同步消息的频率。通过鉴相器鉴别出二者频率的差值fμ,再通过低通滤波器滤除高频噪声,根据频率差fμ产生被同步节点本地振荡器的控制电压Vc。容易看出,被同步节点本地振荡器的输出频率fo随着频差fμ的变化而变化,从而实现频率漂移补偿。

图3 锁相环原理Fig.3 Phase-locked loop schematic

2.2 锁相环实现

基于锁相环原理的时钟漂移补偿机制需要鉴相器等硬件的支持,对于实现节点低成本来说,增加额外的硬件成本是不希望的。无线传感器网络的节点需要完成数据的采集、处理以及传输等工作,通常配备功能强大的中央处理器来处理本地工作。因此,可以利用节点主机资源设计如下的数字锁相环。

2.2.1 鉴相器实现

鉴相器是锁相环最基本的部件,它的主要工作是完成两个输入信号相位差的鉴别。鉴相器的工作可以利用节点主机处理器的定时器模块完成。

由于时标节点发送同步消息的频率已知,因此可以通过设置被同步节点定时器的分频系数以及自动重装载寄存器的值,使计数器的计数周期与同步消息的发送周期相匹配。以接收到同步消息为触发条件,去捕获计数器的值。在理想情况下,即两个节点的本地晶振没有频率漂移时,被同步节点在每个同步消息被接收到时捕获到的计数器值是恒定的。而当两者的本地晶振存在相对漂移时,多次捕获到的计数器值就会存在偏差,此偏差可以看作是时标节点与被同步节点时钟的相对漂移量。由此可以得到补偿本地时钟漂移量的依据。

2.2.2 滤波器实现

同步消息在传播过程中存在的随机干扰会对频率的测量产生影响,因此需要设计滤波器来消除高频噪声,以提高频率测量的精度。

算术平均值滤波,是数字滤波最简单和最常用的一种。其原理是在某时刻对信号进行连续多次采样,对采样值进行算术平均,作为该时刻的信号值。算术平均值滤波对抑制周期性干扰和随机干扰有良好效果。在时钟漂移补偿过程中,两个时钟的相对漂移量在短时间内相对固定,因此采用算数平均值滤波是合理的。具体来讲,需要捕获多组计数器的值,得到多组相同时间段的时钟漂移量进行算数平均,该平均值作为某一时刻时钟漂移补偿的依据。

2.2.3 控制电压的产生

通过上述鉴相器以及滤波器得到的时钟相对漂移量是一个数值,而非压控振荡器所需的控制电压信号。控制电压信号通过主机的DAC模块产生。将时钟的相对漂移量经过换算控制DAC模块,从而产生控制电压。

3 性能测试

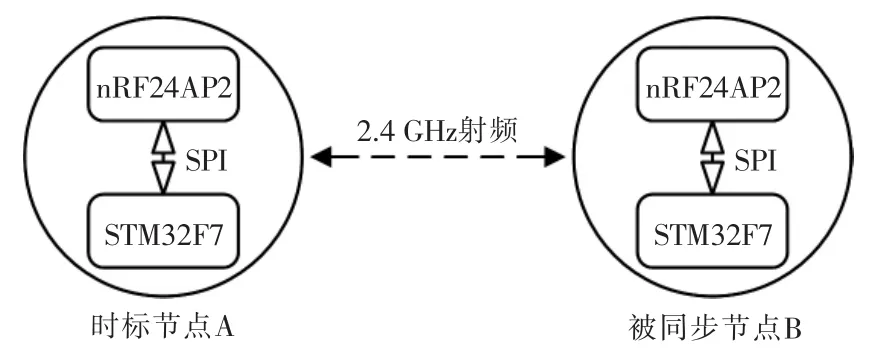

为了验证所设计补偿方法的可行性,我们利用STM32F7微处理器与ANT无线通信模块nRF24AP2实现了该方法。STM32F7与ANT无线通讯模块nRF24AP2通过SPI进行通信,构成无线传感器网络的一个节点。实验配置如图4所示。

图4 实验配置示意Fig.4 Experimental configuration diagram

时标节点A周期性地广播同步消息,被同步节点B相对于节点A的时钟漂移将被补偿。节点A选取同步消息的发送频率为8 Hz。节点B的主机STM32F7的时钟源晶振频率为19.2 MHz,通过倍频和分频以7.2 MHz输出到定时器,计数器的自动重装载值设置为900000,计数周期为125 ms,与节点A发送同步消息的周期匹配。节点B接收到同步消息时触发STM32F7定时器的捕获中断,并在捕获中断的回调函数中读取计数器的当前值。

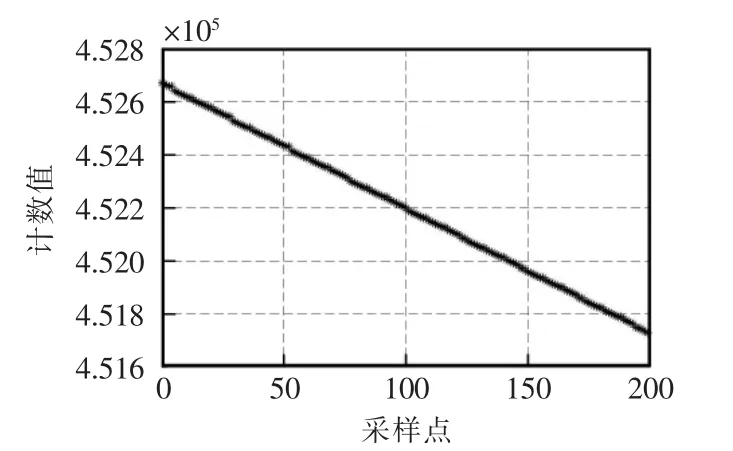

图5为漂移补偿前进行200次采样,计数器读数的变化趋势。由图5可知补偿前计数器读数整体呈下降趋势,表明节点A与节点B之间存在时钟漂移。另一方面,计数器的值虽有抖动,但基本以某一比例线性递减,说明晶体振荡器的频率在短时间内稳定的假设是合理的。

图5 补偿前计数值变化趋势Fig.5 Pre-compensation count value change trend

为了方便说明,将图5计数器的变化值换算成时间绘制出图6。由图6可知,节点A与节点B在每个计数周期(125 ms)的时钟漂移在0.6 μs左右,且抖动较大。

图6 补偿前时钟漂移量Fig.6 Amount of clock drift before compensation

图7为补偿之后进行200次采样,计数器读数的变化趋势。由图7可知,计数器读数没有明显的以某一比例线性递增或者递减,基本保持稳定,表明节点A与节点B之间的时钟漂移得到有效补偿,在相同时间内的相对时钟漂移量较之补偿前明显降低。

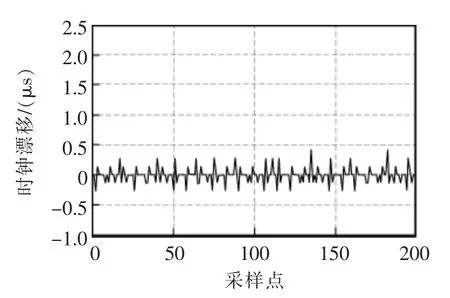

同样将图7计数器的变化值换算成时间绘制出图8。由图8可知,补偿后节点A与节点B在每个计数周期 (125 ms)的时钟漂移基本维持在0 μs左右,虽有抖动,但较之补偿之前更加稳定。

图8 补偿后时钟漂移量Fig.8 Compensation clock drift

为方便比较,作进一步的定量分析,求取补偿前后200次采样时钟漂移的最大值、平均值以及方差,将统计结果列于表1中。不难看出,补偿后平均每个采样周期 (125 ms)的时钟漂移量下降0.58 μs, 时钟漂移峰值由 2.361 μs 下降到 0.417 μs,而且补偿之后的数据样本方差更小,稳定性也有所改善。

表1 200次采样时钟漂移量Tab.1 200 samples of clock drift

4 结语

节点时钟频率的相对同步对无线传感网络时钟同步意义重大,在不需要额外硬件支持下提出一种基于节点微处理器的软件实现方法,可以大幅度改善节点间时钟漂移情况。在对网络时钟同步要求越来越高的大前提下,高精度、低成本是未来时钟同步的主流发展方向。本文介绍的方法结构简单,易于实现,具有较高的工程实践价值,能满足无线传感器网络在多数应用场景下的时钟同步精度要求,为无线传感器网络节点间的时钟漂移提供一种良好可行的补偿方案。