高阶调制信号发生器可变参数基带模块设计

2018-05-21郭业才万逸儒

郭业才, 万逸儒, 吴 星, 胡 峥

(1.南京信息工程大学 电子与信息工程学院,南京 210044; 2.江苏省大气环境与装备技术协同创新中心,南京 210044)

0 引 言

针对现代卫星通信盲均衡系统产业化实现的需求,搭建一个完整的电子测量系统显得十分必要。然而,只有在能够采集到某类信号时,这些工具才能进行测量,绝大多数情况下,这些信号是没有的,所以研制可以稳定精确地产生调制信号的发生器能弥补电子测量系统激励不足的问题,同时为了方便工程师探测盲均衡系统性能的极限,信号发生器必须还具有高阶调制及各个参数灵活可变的功能,使余量测试和检定成为可能。信号发生器的性能指标和考虑因素主要有:存储深度、采样速率、带宽、幅度分辨率、定时分辨率、区域位移功能、输出通道数量、数字输出、排序、集成编辑器、数据导入功能、无杂散动态范围、相位噪声密度等。目前,国内的数字合成信号发生器在技术指标上与国外相比还存在很大的差距[1],例如,比较有名的生产信号发生器的大公司有安捷伦、美国国家仪器NI、罗德与施瓦茨、泰克科技、台湾百科精密仪器、利达电子株式会社等,其中安捷伦仪器的PSG系列信号发生器已经可达毫米波范围,最高可以产生70GHz的射频信号,高品质的射频调制带宽支持为雷达、电子战、和卫星通信测试生成更真实的宽带信号,最大限度提高多普勒雷达或接收机阻塞测试的接收机灵敏度,或在相位噪声测试系统中用作理想的基准:100 Hz 频偏时为-91 dBc/Hz;10 kHz 频偏(67 GHz)时为-126 dBc/Hz,低杂散和谐波(分别为 10 GHz 处-70 dBc 和 55 dBc)的出色性能可以改善信号质量并提高测试精度。

1 系统设计

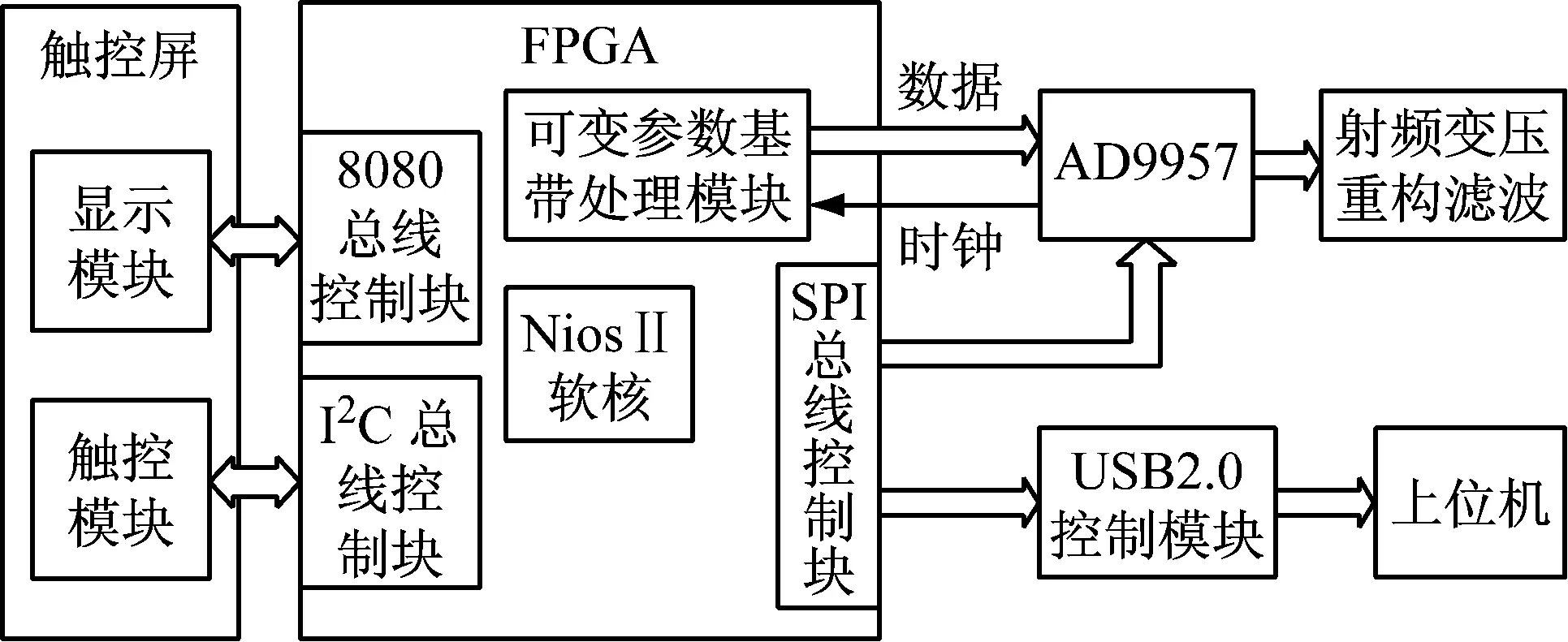

本设计方案使用硬件逻辑可编程的FPGA设计基带硬件结构及基于软件无线电思想的通用、标准化、模块的硬件设计平台,通过Altera FPGA内部集成的NiosⅡ软核[2]设置参数值。系统总体框架,如图1所示。图中,AD9957上变频芯片工作在1GHz频率,内部可通过8-252可编程插值输出同步时钟到FPGA内部可变参数基带处理模块,AD9957通过T1-1T射频变压器将差分型号转换为单端信号,并经过160 MHz截止频率的7阶椭圆模拟重构滤波器输出到BNC接口端。同时,FPGA内部用QSYS搭建SOPC系统,该系统集成了NiosⅡ/fast软核、高速缓存单元、内部紧密耦合寄存器、SDRAM控制模块、EPCS控制模块、JTAG_UART仿真器控制模块、系统时钟单元、时间戳单元、总线(8080总线、SPI总线、I2C总线)控制模块。同时该设计可以通过上位机和基于图形库支持脱机操作的触控屏来完成人机友好界面的交互。

图1 系统总体框架图

2 数字脉冲成型原理

2.1 升余弦滤波器

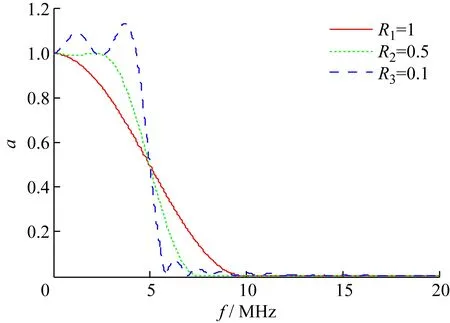

由于矩形脉冲的频谱形状是sinc响应,在码元速率为f0的整数倍处周期性的出现零点,造成基带信号在频谱上无限制的拓展,在大部分数据传输应用中,所传输的信号必须限制在一定的带宽内[3-5].文献[6]中提供了在卫星对地数据传输系统领域,国际空间数据系统咨询委员会(Consultative Committee for Space Data Systems,CCSDS)建议中给出的固态功放(Solid-state Power Amplifier,SSPA)下各种调制方式的频谱密度示意图。由图可见,限制矩形脉冲带宽的低通滤波器是必须的,这种将矩形脉冲形状从门形状变为无陡峭边沿的平滑轮廓线的低通滤波器称之为脉冲整形滤波器。然而,理想低通滤波器在频域表现为门形状,因此在时域必定表现为阻尼衰减的特性,码元经过阻尼衰减的拖尾会产生对邻近码元有干扰的纹波,纹波会导致数据解码的错误。综上所述,必须选择既能限制频域脉冲带宽又能保证时域波形无码间干扰的滤波器。满足这两个条件的著名滤波器就是升余弦滤波器,其频率响应为:

(1)

式中:T是码元周期;α是余弦滚降系数;ω是角频率。

相应的时域响应形式为:

(2)

2.2 余弦滚降系数

滚降系数的概念是建立在升余弦特性频谱带宽相对于理想低通特性带宽的基础上提出来的,余弦滚降系数决定了两个比较重要的频率点,一个是阻带频率点fstop,另一个是通带频率点fpass,它们相对于滚降系数的关系式为:

(3)

式中:f0是脉冲速率;f0/2是奈奎斯特频率点,也称理想低通滤波器的截止频率。

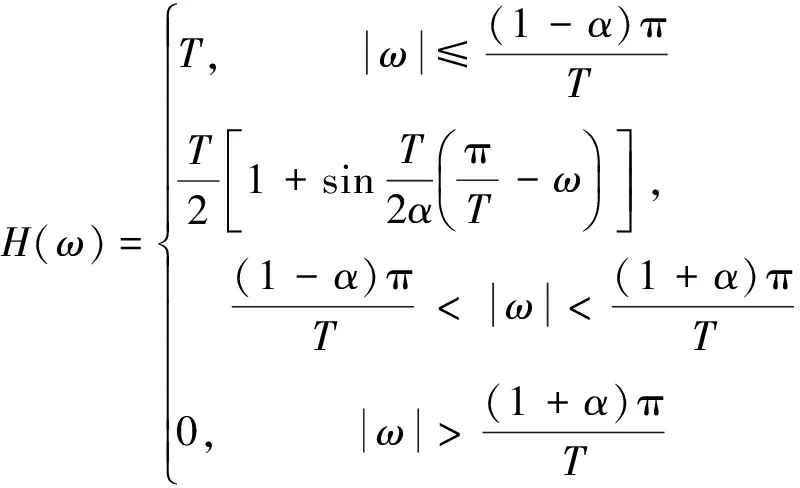

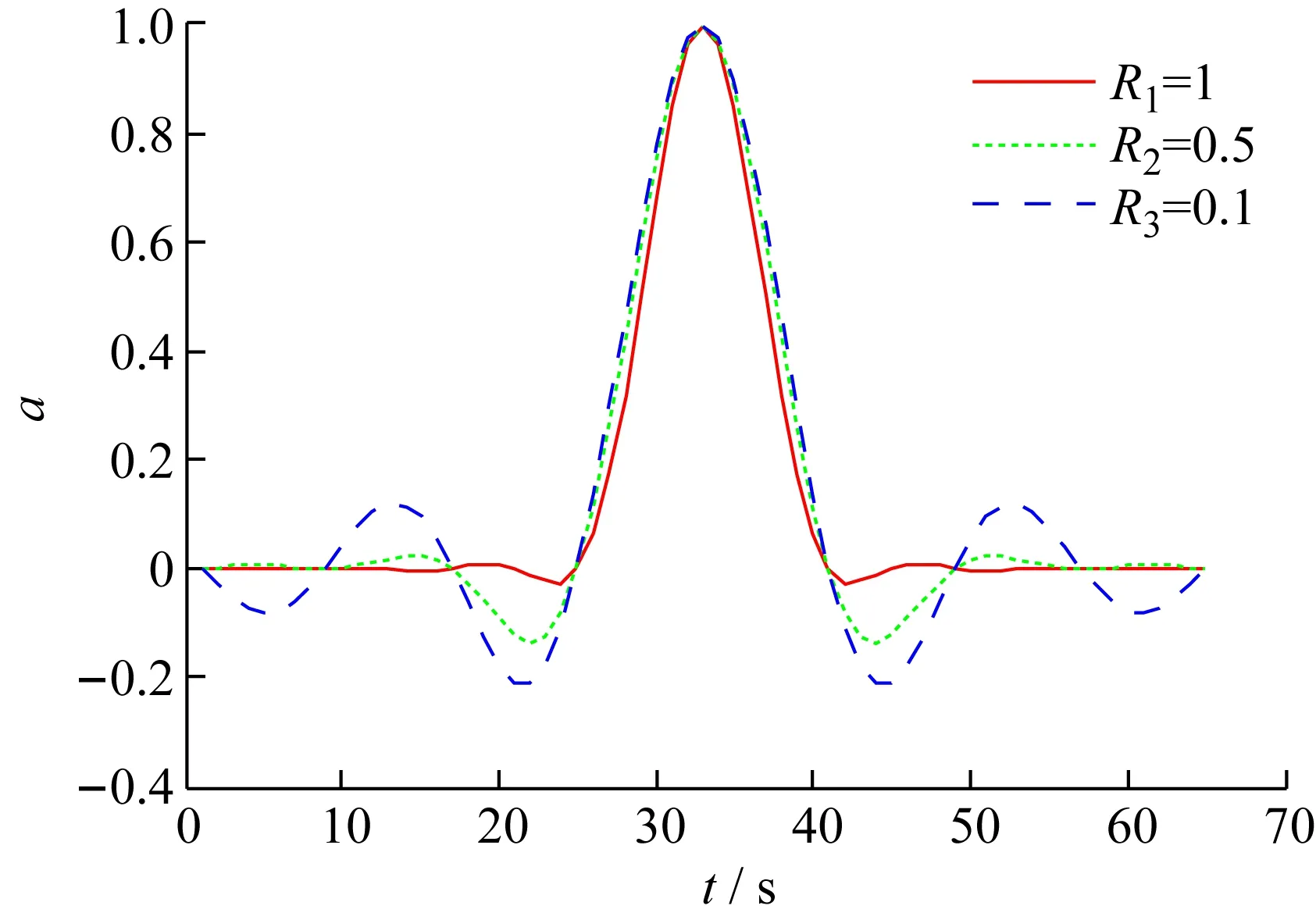

余弦滚降系数与滤波器带宽成正相关关系,在插值倍数为8、双边截断符号码元数为8、码元速率为10 MB、采样速率为80 MB条件下,图2和图3分别仿真了滚降系数为1,0.5,0.1时的滤波器时域和频域特性。

图2 滚降系数为1,0.5,0.1时的时域特性图

图3 滚降系数为1,0.5,0.1时的频域特性图

由图可见,在滚降系数为0.1的情况下,频域特性急剧恶化,图中产生了最大约0.1左右的带内波纹,这里可以通过增加截取符号码元数来弥补波纹的恶化,但会增加滤波器阶数从而提高了硬件系统复杂度和资源耗用。从时域角度来说,滚降系数越小时域拖尾也会越大,接收端符号码同步不可能完全没有误差,只要有一点误差,就会因为较大的时域拖尾而造成很大的码间干扰,恶化系统的信噪比,影响系统的误比特率。当然滚降系数也不能过大,过大会造成系统频带利用率的下降,同时会引入更宽带宽的带内噪声,对数模转换后的低通滤波器和接收端模数转换前的抗混叠滤波来说,在过宽的带宽内保证幅度一致和线性相位是非常困难的,文献[3]中指出了系统误码率在滚降系数取0.5~1之间时区别不大,因此设计了可调滚降系数范围为0.3~0.5。

2.3 双边截断码元数

双边截断码元数与滤波器阶数复杂度成正比,因此要使用满足滤波要求的最小双边截断码元值,文献[7]中给出了基于浮点运算模拟生成的通带边缘频率处误差、奈奎斯特频率处误差、阻带频率处误差随余弦滚降系数和双边截断码元数变化的三维曲面图,说明了可接受的最小截断码元值是由频域特性的带外第一个衰减旁瓣峰值决定的,尤其是在滚降系数极小时,更需要考虑最低阻带衰减特性。在插值倍数为8、双边截断码元数为8、码元速率为10MB、采样速率为80MB条件下,图4分别仿真了余弦滚降系数为0.5,0.3,0.2时的频域特性曲线图。

图4 双边截断码元数为8情况下不同滚降系数频域特性曲线图

可以看出,滚降系数为0.5时阻带第一个衰减旁瓣峰值在-40 dB以下,滚降系数在0.3时第一个衰减旁瓣峰值正好在-40 dB上,滚降系数在0.2时第一个衰减旁瓣峰值在-30 dB左右,此时会引入更多的旁瓣噪声,导致信噪比的恶化,因此余弦滚降系数下限设计在0.3 ,双边截断码元数为固定值8。

截断码元数之所以取固定值是由两方面因素决定的,① 截断码元数在多相时变系数插值滤波器中直接映射为每组子滤波器的系数个数,也就是FPGA中乘法器使用单元数,过多的截断码元会导致乘法器资源的消耗。② 滤波器抽头阶数一般是由Matlab产生的浮点数,需要进行一定比例的放大并取整,放大倍数为

(4)

2.4 插值倍数

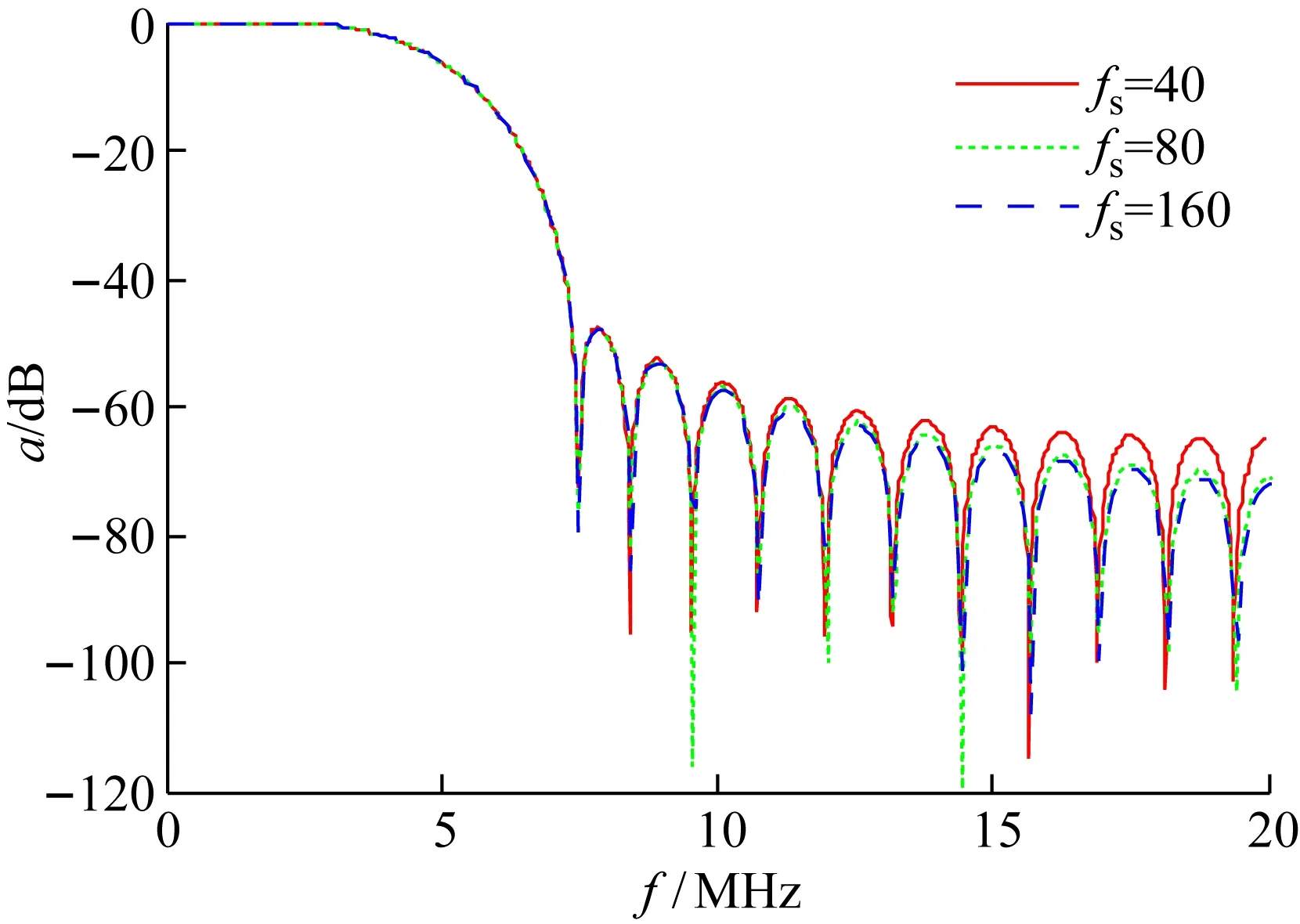

由奈奎斯特采样定理可知,采样频率必须大于或等于带内信号的最高频率,插值倍数是采样频率相对于码元传输频率的比值,根据数字采样定理可知,双边截断码元是对升余弦滤波器时域响应的有限长度截取,而在频域则表现为按采样频率进行周期的幅频特性的搬移。原始的周期脉冲频域形状是众所周知的sinc响应,零点总是出现在码元速率f0的整数倍处,多进制波形可看做是多个二进制振幅波形的叠加,因此频域特性也是多个信号的频域特性之和,尽管叠加后频谱特性较复杂,但就零点出现特性而言,在f0的整数倍上也总是表现为0幅值,当插值倍数为整数时,滤波器按采样频率搬移的通带正好出现在f0的整数倍上,可以有效地降低频率搬移对滤波特性的影响。在双边截断码元数为8、余弦滚降系数为0.5、码元速率为10 MB条件下,图5给出了插值倍数分别为4,8,16即采样速率为40、80、160 MB的幅频特性图。

图5 不同插值倍数下的幅频特性图

从图中可以看出,不同插值倍数虽然不会对第一个衰减旁瓣峰值有所影响,但会影响后级旁瓣峰值大小,采样率越高,时域成型效果越好,频域后级旁瓣衰减越大,但会增加滤波器的阶数,提高FIR复杂度,也会使输出码元速率增大,增大了系统实现难度。

3 可变参数基带处理模块设计

3.1 串行IQ链路多相时变系数滤波器的结构

AD9957、AD9857、AD9854等具有正交调制功能的上变频芯片,它们在并行端口上交替出现I和Q路数据字,并在时钟有效沿进行捕捉,因此在基带处理部分,也可以设计成串行IQ两路串行的串并转换、星座映射、成型滤波,这样可以不用进行时钟分层以及节省下一路的滤波资源和映射编码逻辑,传统的FPGA插值滤波器采用的是全并行分布式算法原理[5],这种基于查找表结构的滤波器可以大大提高电路的执行速度及不需要乘法资源,目前大多数FPGA/CPLD都集成了DSP处理单元,内部嵌入了细颗粒单周期乘法器,用这些乘法器来设计卷积滤波器将大大降低系统复杂度。

假设插值滤波器抽头为

H=[h(1),h(2),h(3),…,h(N)]

式中:N=D×M;D是双边截断码元数;M为插值倍数。将H分解为M个子滤波器:

(5)

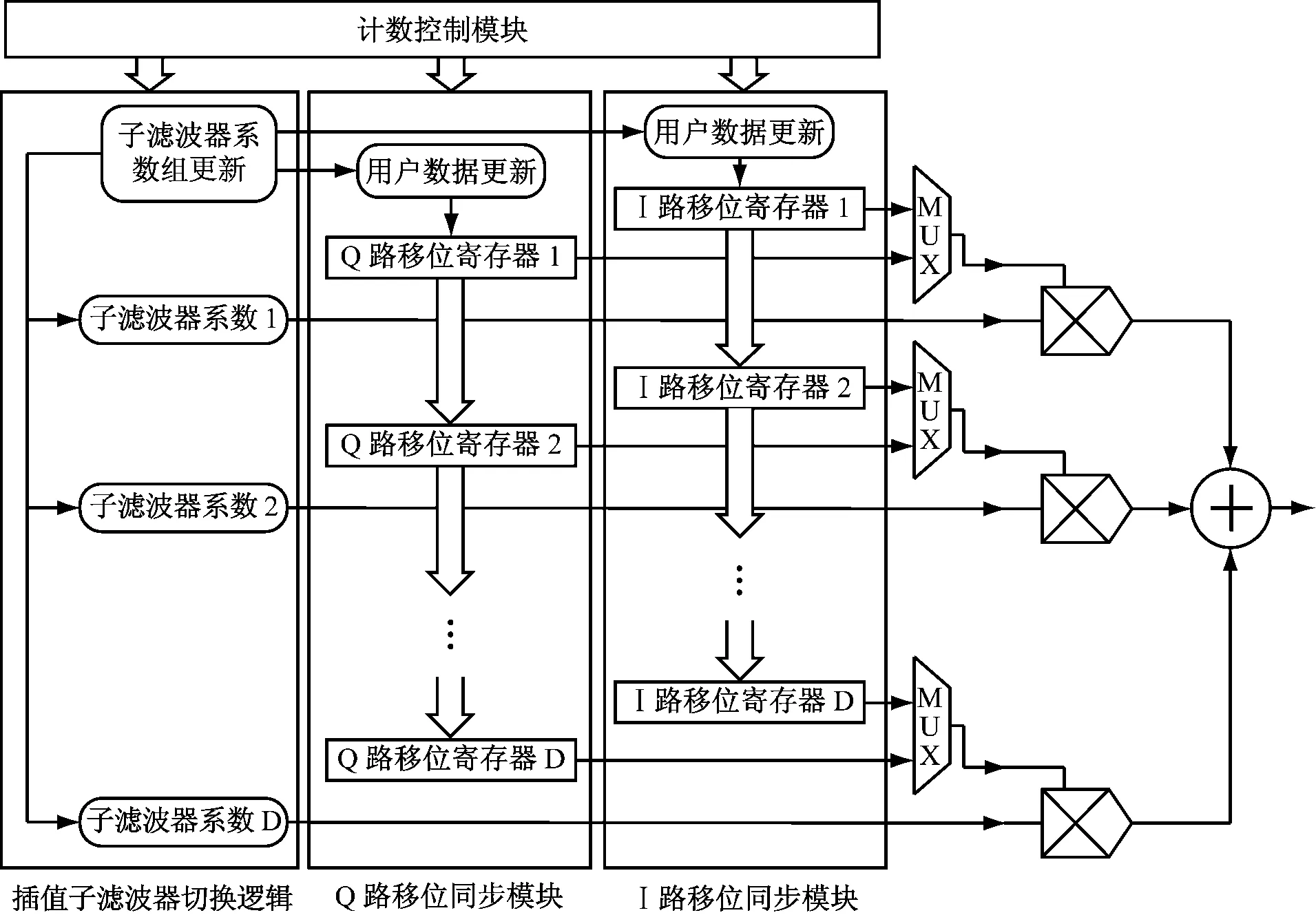

这种结构的插值滤波器只需要D个乘法器资源,相对于采用FIR的IP核要节省M倍的乘法器,图6给出了串行IQ链路多相时变系数滤波器[4]的结构图。

在每个PDCLK时钟周期,计数控制模块都会控制子滤波器系数组都会进行更新,当M组子滤波器都遍历更新过一遍之后的第一个PDCLK周期,计数控制模块控制I路用户数据更新入I路移位寄存器,第二个PDCLK周期,Q路用户数据更新入Q路移位寄存器,并在每一个PDCLK周期由计数控制的MUX选择器控制IQ两路链路串行进入并行乘加单元进行滤波[8-15],并行乘加单元输出18位(1位符号位+17位数据位)数据给AD9957,因为最高使用256QAM,也就是16ASK正交调制,共16个电平位,电平位间隔为2,需要1位符号位+4位数据位,所以用户数据设置为5位,AD9957并行数据输入口为18位,留给串行IQ链路多相时变系数滤波器的有效数据位数是1位符号位+13位数据位,相乘后得到的数据进行3级流水线加法器得到累加输出值。

图6 串行IQ链路多相时变系数滤波器的结构

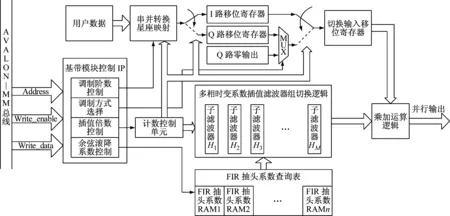

3.2 可变参数基带处理模块数字逻辑设计

可变参数基带处理模块主要实现的是信号调制方式、调制阶数、成型滤波器插值倍数和余弦滚降系数的可变调度,具体结构图,如图7所示。

NIOSⅡ软核通过AVALON-MM总线传输地址、数据、写使能给从端的基带控制模块IP核从而改变IP核内部对参数控制的数据,需要一个地址位映射到两个寄存器:控制数据寄存器和FIR抽头系数寄存器,为了节约FPGA内部存储资源,FIR抽头系数查询表放在SDRAM中,通过Nios的读取并传输到基带模块IP

图7 可变参数基带处理模块结构图

的FIR抽头系数寄存器中。数据总线设计为16位,在控制数据寄存器中[1:0]位传输插值倍数控制参数,[3:2]位传输调制阶数参数,第4位传输调制模式控制参数,第5位传输DAC和正交调制切换选择参数,[15:6]传输余弦滚降系数参数;在FIR抽头系数寄存器中,数据总线只需要14位,每次传输一个抽头系数,因为抽头系数是对称的,因此直到抽头系数通过总线传输个数达到65个即停止。每次参数更改都需要软复位清零一下计数控制单元的计数值,调制方式可选值为QAM和ASK,使用QAM调制时Q路移位寄存器处于工作状态,使用ASK调制时,Q路移位寄存器被旁路,Q路相对I路间隔输出零值,即关闭AD9957的DDS余弦输出功能。调制阶数可选为4QAM/2ASK、16QAM/4ASK、64QAM/8ASK、256QAM /16ASK,插值倍数可调阶数为2、4、8、16,选择这个阶数的原因是这些抽头系数的公倍数是最高可插值倍数16,这样可以节省抽头阶数的存储,16倍插值的成型滤波器抽头系数包含了2、4、8倍插值的抽头系数,插值倍数控制模块通过控制计数单元的步进梯度从而间隔选择不同的子滤波器。余弦滚降系数可选范围为0.3~0.5,更新余弦滚降系数FIR抽头系数查询表切会换到相对应滚降系数的FIR抽头系数RAM,并导入到多相时变系数插值滤波器组中。计数控制单元的最低位映射到IQ链路的切换,高位映射到插值子滤波器的移位更新及用户数据星座映射的更新。

4 调制信号发生器仿真和实验结果

为了提高基带处理模块的最高运行频率,需要对AD9957并行输入端口进行时序约束,根据AltiumDesigner画出的PCB线路统计出18根并行总线和1根时钟总线的PCB传输时延,在介电常数为4.0的条件下,单位走线时延[5]为0.18 ns/1 000 mil,在TimeQuest Timing Analyzer中约束输出最大和最小延时:

Output Max Delay=PCB Max Delay+

AD9957 Setup Time+Clock Max Delay+

(Latch Time-Launch Time)=

0.35 ns+1.75 ns+0.24 ns-5 ns=-2.66 ns

Output Min Delay=PCB Min Delay-

AD9957 Hold Time+Clock Min Delay+

(Latch Time-Launch Time)=0.18 ns+0 ns+

0.23 ns-5 ns=-4.59 ns

(6)

仿真后得到PDCLK最高时钟118.96 MHz,这个结果已经可以满足AD9957内部绝大部分的可编程插值倍数值,其中PDCLK需要配置为极性反转,上升沿驱动,下降沿锁存。

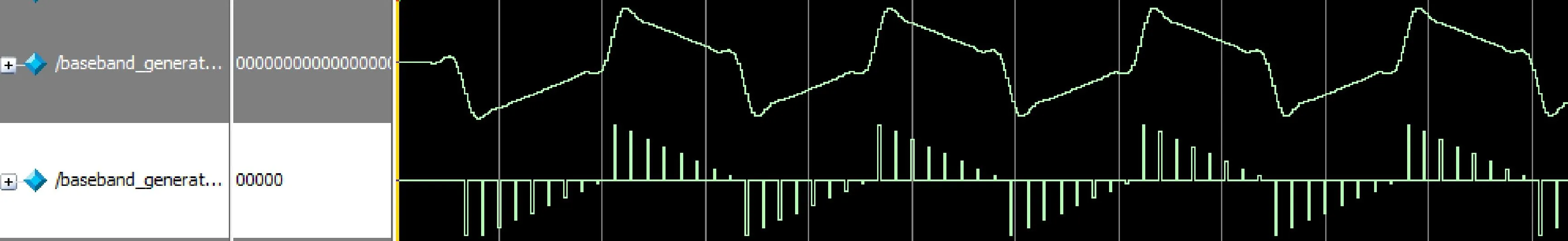

图8和图9分别是用户数据经过脉冲成型后的Modelsim基带波形图和SignalTapⅡ基带波形图,仿真条件:余弦滚降系数0.5,插值倍数8,双边码元截取长

图8 Modelsim基带波形仿真图

图9 SignalTapⅡ基带波形仿真图

找到波形,用户输入数据采用了步进递增符号码。

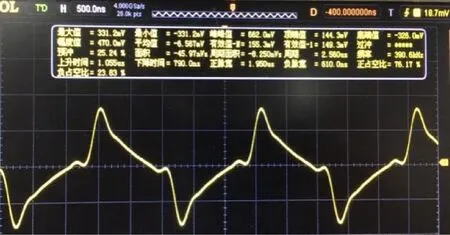

图10和图11是硬件实验结果图,基带配置条件不变,AD9957配置为内部时钟1GB,CCI+HB插值倍数为20倍,反sinc滤波器和反CCI滤波器使能,图10是AD9957配置为DAC模式时输出基带波形,PDCLK时钟为50MB,图11是配置为QDUC模式时输出的16ASK调制波形,PDCLK时钟为100 MB,载波设置为50 MB。

图10 基带波形实验结果

图11 调制波形实验结果

由图可见,基带波形实验结果和仿真结果基本相同,调制波形的包络很好地还原了基带波形的形状。

5 结 语

本文阐述了升余弦滤波器的时域频域特性,并充分分析了FIR升余弦滤波器的余弦滚降系数、双边截断码元数、插值倍数的取值关键要点,设计了串行IQ链路多相时变系数滤波器,提高了系统的时钟资源、逻辑资源及DSP资源的利用率。最后利用FPGA可编程逻辑完成了可变参数基带处理模块,提升了系统的灵活性,并集成为AVALON总线规范的IP核,增加了该模块的可移植性,该设计使用了较低的资源实现了软件可控的高阶调制信号发生器。

参考文献(References):

[1] 吴彬彬,郭业才. 高阶调制信号发生器设计与实现[D]. 南京:南京信息工程大学硕士学位论文, 2015.

[2] Pong P. CHU,基于NiosⅡ的嵌入式SoPC系统设计与Verilog开发实例[M]. 北京:电子工业出版社,2015.

[3] 梁婷婷,迟永刚,刘军军,等.一种具有任意倍升采样的高速率脉冲成型算法[J].哈尔滨:哈尔滨工业大学学报,2015,47(11):53-58.

[4] 付文君,姜景山,王拴荣,等. 一种可变插值比的脉冲成型数字滤波器FPGA设计[J]. 遥感技术与应用, 2006,21(5):445-450.

[5] 吴厚航. 爱上FPGA开发特权同学和你一起学NIOSⅡ[M].北京:北京航空航天大学出版社,2011.

[6] 胡俊杰.卫星数据传输高速调制器关键技术研究[D]. 北京:中国科学院研究生院博士学位论文,2011.

[7] Gentile K. The Care and Feeding of Digital Pulse-Shaping Filters[DB/OL].(2002-04-30)[2017-11-10].HTTP://www.rfdesign.com.

[8] 杜 勇. 数字调制解调技术的Matlab与FPGA实现[M].北京:电子工业出版社, 2015.

[9] 郭业才,章 涛,袁 涛. 卫星信道模拟器数字下变频系统设计[J]. 科学技术与工程, 2014,24(1):54-59.

[10] 刘华侨,林静然.64QAM调制解调关键技术研究与实现[D].成都: 电子科技大学硕士学位论文,2013.

[11] 于伟龙,宗成阁.基于AD9957的信号发生器设计[D]. 哈尔滨: 哈尔滨工业大学硕士学位论文,2014.

[12] 谭龙龙,宗成阁.列车防撞雷达信号源开发设计[D]. 哈尔滨: 哈尔滨工业大学硕士学位论文, 2013.

[13] 任 哲. 嵌入式实时操作系统uC/OS-Ⅱ原理及应用[M]. 2版.北京航空航天大学出版社,2013.

[14] 李 敏,王 孜, 邵奕强,等.自适应低通滤波器的设计与实现[J].实验室研究与探索,2014,33(8):89-93.

[15] 樊开阳,杜小峰, 杨红兵. 基于FPGA的FIR滤波器设计方案优化[J].实验室研究与探索,2014,33(5):91-95.