一款高精度数控振荡器设计与实现

2018-03-06潘天锲

赵 信,潘天锲,王 飙

(上海高性能集成电路设计中心,上海 210000)

1 引言

由于全数字锁相环ADPLL(All Digital Phase Locked Loop)拥有较高的集成度、灵活的可配置性、快速的工艺移植特性,可以解决模拟电路电压裕度不足、无源器件面积过大、抗噪声能力不强、锁定速度慢以及工艺可移植性差等瓶颈问题,所以从全数字锁相环提出之日起,就受到了广泛的关注和研究。在全数字锁相环系统中最重要的模块就是数控振荡器DCO(Digitally Controlled Oscillator)。数控振荡器用来产生高频时钟,本文提出一种改进的环形数控振荡器结构,具有频率范围大、抗噪声能力强、抖动小、可调节分辨率高等优点,适用于先进工艺下高性能SOC(System On Chip)应用。

目前在公开发表的文章中已有一些基于标准单元设计数控振荡器的研究。文献[1]中采用了粗调和精调两级结构,粗调通过调整反相器级数来调节振荡频率,精调部分分为两级,分别采用增加单极反相器的电流和增加反相器的负载来调整反相器的延时。文献[2]的方法类似,粗调同样采用反相器链结构,通过调节反相器的个数来调节DCO频率。在精调部分采用了或与非OAI(Or And Inverter)和与或非AOI(And Or Inverter)逻辑门器件,通过控制信号来控制OAI和AOI器件的延时,但该方法调节线性度较差。文献[3]中粗调部分采用了与门来代替反相器链,增加了使能信号来降低功耗,在精调部分采用三级级联的模式。该方法解决了线性度的问题,但是路径选择上使用了选择器(MUX),这样选择路径的延时较大,降低了DCO的频率范围。文献[4]采用了级联(Cascaded)延时单元结构,该方法可以降低面积及功耗,但是需要定制延迟单元,实现方法相对于基于标准单元库的方法要复杂。

本文提出了一种改进的DCO结构,采用粗调、中调和精调级联的结构,粗调通过选择延时单元的数量确定频率范围,中调通过改变单极延时单元的电流来调节延时,精调则是通过改变单极延时单元的负载来调节延时。为了提高调节精度的线性度,在中调和精调部分做了改进,采用了分组控制和驱动倍数递增的方法。每一级的调节范围需要覆盖前一级的最小调节精度,这样可以避免出现频率盲区,此结构DCO的分辨率达到0.8 ps。

基于此DCO架构完成了一款新的全数字锁相环系统设计,该系统完全采用标准数字单元库实现,在2.6 GHz振荡频率下,系统抖动小于2 ps,满足高性能SOC对时钟低抖动的需求。

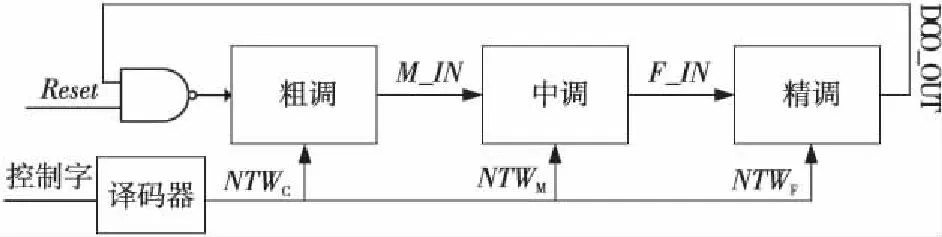

2 数控振荡器结构

数控振荡器用来产生高频时钟,其中最为重要的两个指标就是调节精度和频率范围,通常这两个性能指标需要平衡设计。本设计采用粗调、中调和细调的三级调节机制,频率范围由粗调确定,中调和细调在小的频率范围内微调直到系统锁定,在保证调节范围的前提下提高了调节精度。该DCO结构如图1所示。

Figure 1 DCO structure图1 DCO结构

如图1所示,粗调、中调和精调部件组成了一个环形振荡器。需要保证DCO的输出与环路的输入信号的相位相差180度,这里采用与非门作为复位逻辑,其它逻辑部分都采用正相逻辑,可以保证满足起振条件。

2.1 粗调

粗调部分通过选择延时链中延时单元的数目来确定频率范围,该部分主要设计难点是如何实现宽的频率范围。要覆盖更高的振荡频率,就需要减小延时链上的固有延时。固有延时在粗调、中调和精调中都会存在。

本文提出的架构在文献[3]的基础上进行了改进,一是将延时单元改用buffer代替与门,二是采用三态buffer代替了MUX,可以大大减小延时链中的固有传输延时,扩大DCO的频率范围。其结构如图2所示。

Figure 2 Coarse part structure图2 粗调部分结构

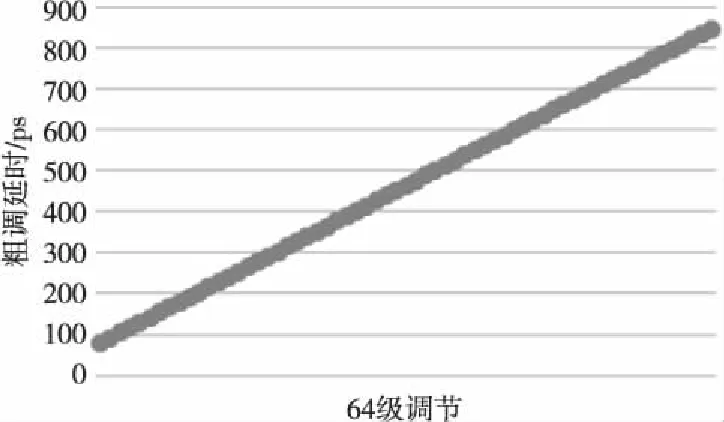

如图2所示,反相器延时链采用两级选择结构。第一级选择8个segmental中的一个,每个segmental中包含8个buffer组成的延迟链,第二级选择一个buffer作为输出。这样一共有64条通路可供选择。在先进工艺下实现了该结构,粗调调节精度约为13 ps,那么总的延时最大为800 ps,加上两级三态buffer作为固有延时。总的粗调仿真结果如图3所示。

Figure 3 Coarse part simulation图3 粗调仿真

从图3可以看出,粗调部分有很好的线性度,固有延时约为50 ps。粗调部分为64选1,所以需要6位地址信号,高三位作为第一级选择地址,低三位作为第二级选择地址。粗调部分调整完毕后基本确定系统的频率范围,该输出信号会送入到中调和精调部分进行精确调整。粗调部分决定了DCO的动态范围,精调部分决定了DCO的精度。

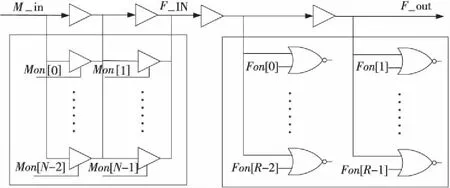

2.2 中调和精调

中调采用调节单极电流的方法调节单极延时单元延时,精调采用调节单极负载的方法调节单极延时单元延时。中调和精调结构如图4所示。

Figure 4 Medium and fine part structure图4 中调与精调结构

如图4所示,中调利用三态buffer与延时链上的buffer并联,通过调节三态buffer的开关来调节延时单元的电流,从而调节单极延时,为了覆盖粗调的最小调节精度,考虑到工艺偏差和工作环境的影响,本级可调节的范围应大于粗调的最小调节精度,这里使用8级调节。

通过控制字Mon[N-1:0]控制8个三态buffer的开关,从而改变了不同状态下的单极电流,单极的延时也会随之变化。这里将8个三态buffer分成了两组,每组4个,分别控制两个延时单元。这是因为随着并联的三态buffer的数量增加,单极延时调节的线性度会下降,所以分成两组来增加线性度。同样,出于线性度的考虑,三态buffer会采用不同的驱动,三态buffer开关状态在改变电流的同时,对负载也有一定影响,所以具体的驱动倍数由仿真确定。中调和精调仿真结果如图5所示。

Figure 5 Medium and fine part simulation图5 中调和精调仿真

从图5a仿真结果可以得到标准工艺下中调单极的调节精度约为3 ps,并保持了很好的线性度;同时,覆盖范围达到27 ps,可以充分覆盖粗调的最小调节精度。

精调是利用调节单极延时单元的负载来调节单极延时,负载采用或非门实现,或非门的一端连在延时链上的buffer输出端,另一端连接控制字。控制字在打开和关闭状态下的负载不同,则延时单位的延时大小不同,利用这个微小的差异可以将分辨率进一步提高。本级采用8级调节,每级的平均延时为0.8 ps,8级调节可以覆盖到上一级最小调节精度,仿真波形如图5b所示。从仿真波形上看,调节的线性度很好,每级调节的精度约为0.8 ps,最大覆盖范围达6.2 ps。随着或非门打开数目的增加,单极buffer延时的调节线性度会变差,所以精调部分同样分为两组,同时通过调节或非门的驱动倍数来调节线性度。考虑到工艺、电压和温度的影响,该级调节范围留出了充分的余量来覆盖中调的最小调节精度。

3 DCO整体仿真

DCO控制字共有12位,粗调部分6位地址,中调和精调部分各3位地址。产生时钟周期的公式如式(1)所示:

TDCO=TC+TM+TF+TD

(1)

其中,TDCO为DCO的周期;TC为粗调部分延时;TM为中调部分延时;TF为精调部分延时;TD为DCO固有延时,即DCO环路中复位电路和选择电路等必要电路的延时。每一级延时如下:

TC=KCNTWC+DC

(2)

TM=KMNTWM+DM

(3)

TF=KFNTWF+DF

(4)

其中,KC、KM和KF分别为粗调、中调和精调的调节精度,NTWC、NTWM和NTWF分别为粗调、中调和精调的控制字,DC、DM和DF分别为粗调、中调和精调的固有延时。

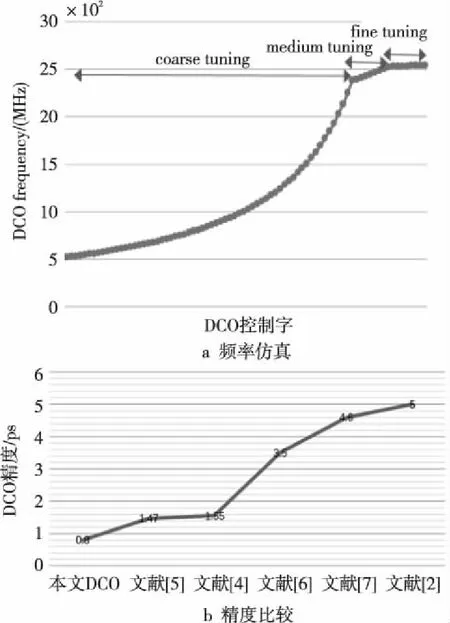

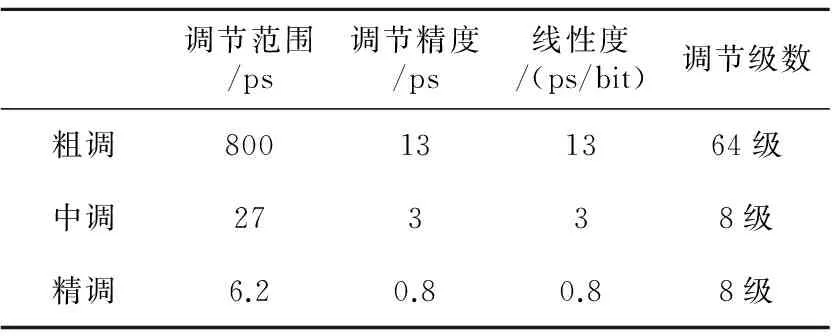

按照图1所示的DCO结构,用门级电路实现了DCO设计,整个设计全部基于数字单元库实现。整个DCO频率仿真和精度比较如图6所示。

Figure 6 DCO simulation and resolution 图6 DCO整体频率仿真及精度比较

从图6a可以看出,粗调部分已基本确定了DCO的振荡频率,中调和精调部分则在小范围内进一步调整振荡频率。最高振荡频率可达到2.6 GHz,最低振荡频率为500 MHz。表1为三级调节的调节精度和频率范围仿真结果。

Table 1 Resolution and frequency range

在先进工艺下实现了此DCO,面积为0.001 mm2,功耗为0.05 mW。版图如图7所示。

Figure 7 DCO layout图7 DCO版图

DCO与对比结构的性能比较如表2所示,可以看到在调节精度、面积和功耗上,本文提出的结构有很大的优势。其中,NA代表Not Available。

Table 2 Performance comparison

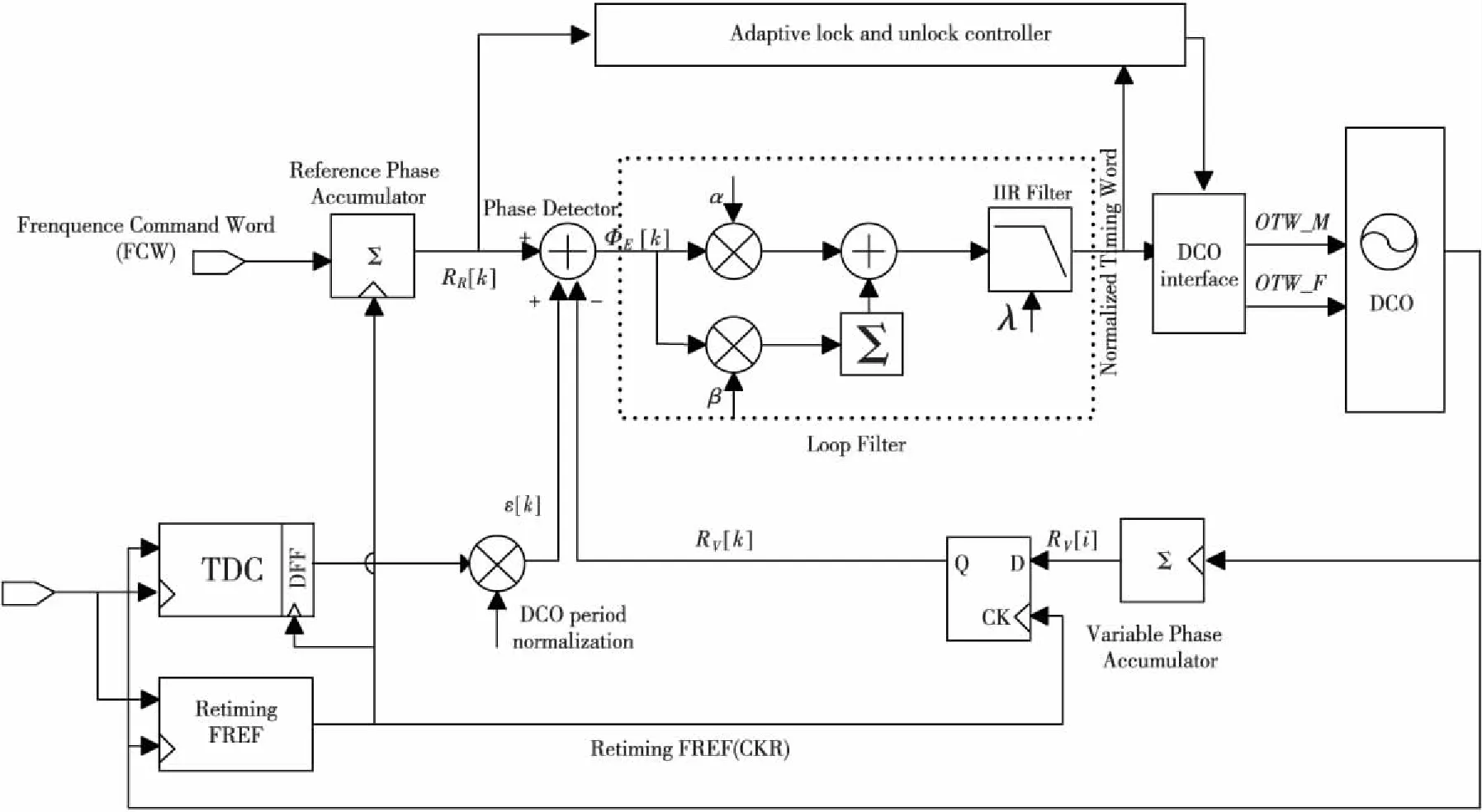

4 ADPLL整体结构及仿真

基于此DCO设计了全新的ADPLL系统,系统结构如图8所示。

Figure 8 ADPLL structure图8 ADPLL系统架构

整个ADPLL的系统同步时钟CKR是由Retiming FREF模块产生的。Reference Phase Accumulator和Variable Phase Accumulator将分别对FREF和CKV(DCO的输出)的整数部分相位进行累加,Reference Phase Accumulator在每个FREF周期累加FCW,FCW即为倍频的倍数,Variable Phase Accumulator在每个CKV周期累加1。FREF与CKV之间的小数部分相位差则由TDC和DCO Period Normalization来估算。PD将Reference Phase Accumulator和Variable Phase Accumulator的计数值相减,然后与TDC的输出相加,便得到了FREF和CKV的相位差。相位差通过Loop Filter滤波之后送给DCO Gain Normalization来消除工艺、电压和温度对环路增益的影响,将得到的控制字送给DCO,用于产生高频时钟。

ADPLL系统由Verilog代码实现,其中DCO和TDC部分采用门级设计,其它模块采用RTL级代码实现。整体时域仿真波形如图9a所示,以系统锁定在2.6 GHz的振荡频率为例。从图9a可以看出,粗调、中调和精调三个调节阶段依次打开,每一阶段结束自动锁存控制字,与此同时系统部分模块进行复位,到锁定状态下,系统处于精调模式。

Figure 9 Noise and jitter analysis图9 噪声分析及抖动分析

图9b为此PLL相位噪声分析,图9a为系统输出时钟周期分析,可以看出TDC量化噪声对于输出噪声的贡献很小,由于DCO的精度变得很高,因此DCO的量化噪声对于输出相位噪声的贡献也很小,经仿真ADPLL整体的抖动小于2 ps,功耗约10 mW,可以满足高性能SOC的应用需求。

5 结束语

本文提出了一款全新的DCO结构,基于全数字标准单元库设计实现,采用粗调、中调和精调级联的调节机制,在保证宽频率范围的要求下,提高了频率精度并加快锁定速度。在先进工艺下实现了此数控振荡器,DCO周期调节精度达到0.8 ps。基于此DCO设计了全数字锁相环,抖动性能达到2 ps,满足高性能SOC应用需求。

[1] Olssonand T,Nilsson P.A digitally controlled PLL for SoC applications[J].IEEE Journal of Solid-State Circuits,2004,39(5):751-760.

[2] Chung C-C,Lee C-Y.An all digital phase-locked loop for high speed clock generation[J].IEEE Journal of Solid-State Circuits,2003,38(2):347-351.

[3] Sheng D, Chung C C, Lee C Y. An ultra-low-power and portable digitally controlled oscillator for SoC applications[J].IEEE Transactions on Circuits and Systems-II:Express Briefs,2007,54(11):954-958.

[4] Huang Qiang,Fan Tao,Dai Xiang-ming,et al.A low power DCO using inverter interlaced cascaded delay cell[J].Journal of Semiconductors,2014,35(11):119-124.

[5] Roth E,Thalmann M,Felber N,et al.Adelay-linebased DCO for multimedia applications using digital standard cells only[C]∥Proc of ISSCC’03,2003:432-433.

[6] Chen P-L,Chung C-C,Lee C-Y. A portable digitally controlled oscillator using novel varactors[J].IEEE Transactions on Circuits and Systems-II:Express Briefs,2005,52(5):233-237.

[7] Chung C C,Ko C Y.A fast phase tracking ADPLL for video pixel clock generation in 65 nm CMOS technology[J].IEEE Journal of Solid-State Circuits,2011,46(10):2300-2311.

[8] Yoo Sang-Sun,Choi Yong-Chang,Song Hong-Joo, et al.A 5.8-GHz high-frequency resolution digitally controlled oscillator using the difference between inversion and accumulation mode capacitance of pMOS varactors[J].IEEE Transactions on Microwave Theory and Techniques,2011,59(2):375-382.

[9] Liscidini1 A, Fanori1 L. A 36 mW/9 mW power-scalable DCO in 55 nm CMOS for GSM/WCDMA frequency synthesizers[C]∥Proc of ISSCC’12,2012:348-350.

[10] Zanuso M, Levantino S, Samori C, et al.A wideband 3.6 GHz digital sigma delta fractional-N PLL with phase interpolation divider and digital spur cancellation[J].IEEE Journal of Solid-State Circuits,2011,46(3):627-638.