基于FPGA的纳秒量级脉冲宽度精确测量研究

2017-06-08于龙洋刘晔孙培钦张耀匀

于龙洋,刘晔,孙培钦,张耀匀

(西安交通大学电气工程学院,陕西 西安 710049)

基于FPGA的纳秒量级脉冲宽度精确测量研究

于龙洋,刘晔,孙培钦,张耀匀

(西安交通大学电气工程学院,陕西 西安 710049)

为使测量光电开关发出的数字脉冲宽度的精度达到1ns和掌握光电开关的实时工作状态。该文通过基于FPGA精确测量法的直接计数法和移相计数法进行测量,得出移相计数法的测量误差在1ns左右,并验证其设计的正确性和有效性。设计通信系统和上位机软件进行实时监控,通信系统采用成熟的串口RS232通信方式,用PFGA设计串口通信模块,实现将数据传输到工控机;再用LabVIEW编写上位机软件,便于工作人员直观观察数据并存储数据到Excel,实验结果证明测量系统可靠、有效。

纳秒量级;FPGA;串口通信;LabVIEW

0 引言

随着控制技术的发展,精确监控光电开关的工作状态是工程实际急需解决的问题,其测量精度达到纳秒量级也是工业自动化技术发展到一定阶段的需求。文献[1]提出的基于DSP结合混沌算法实现的精度测量算法虽然有着广泛的应用前景,但是其系统非常复杂,且成本高。文献[2]提到利用铌酸锂晶体的电光效应,其研制可用于测量纳秒量级脉冲电压的传感器,但是其误差范围在5~7ns,达不到1ns的误差要求。文献[3]基于移相技术的脉冲宽度测量方法能实现纳秒量级测量,且提供了测量数字脉冲的思路,但所需晶振频率达到250MHz,且FPGA芯片价格昂贵,因此本文在此基础上进一步改进其移相技术算法来降低倍频时钟信号,实现低成本的可靠测量系统。论文在脉冲宽度测量方面采用了直接计数法和移相技术法两种算法,并且设计了FPGA与上位机之间的通信。通信系统采用成熟的串口RS232通信方式,LabVIEW在测量领域内是比较普遍的应用软件,与C++等编程语言相比,其图形化语言易理解,存在一定优势。

1 测量原理

1.1 直接计数法

利用FPGA内部锁相环(PLL)模块将外部输入晶振频率倍频到1GHz,使得周期变为1 ns,将其时钟作为计数器时钟对外部脉冲进行计数,这样其计数误差最大不会超过1ns。因此,使用FPGA内部计数器对锁相环(PLL)倍频的1GHz进行计数从而达到纳秒量级的精度,再等待光电开关产生的外部脉冲信号进入[4-6]。以光电开关产生的正脉冲为例,设置计数器上升沿触发开始以PLL模块产生的1GHz进行计数,以外部脉冲的下降沿为结束。计数结果为外部脉冲宽度,其误差在1ns左右。时钟为1GHz,一旦外部脉冲产生其上升沿将触发计数器开始计数,等待外部脉冲下降沿到来停止计数器工作,最终计数器累计数值为测得外部脉冲宽度。算法整体框图如图1所示。

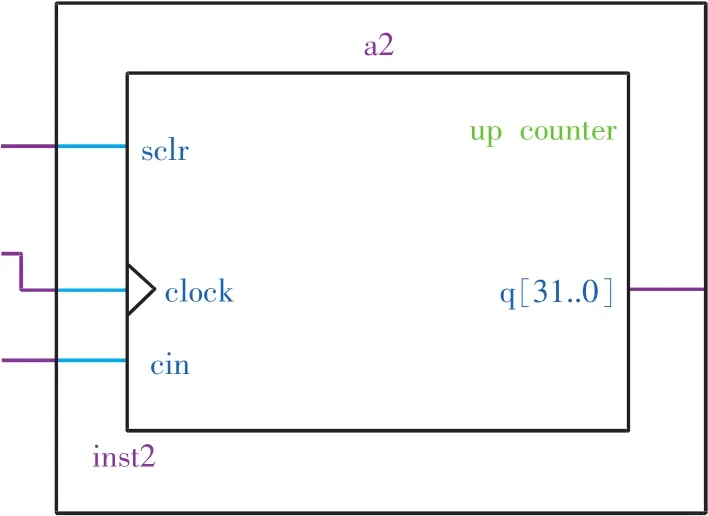

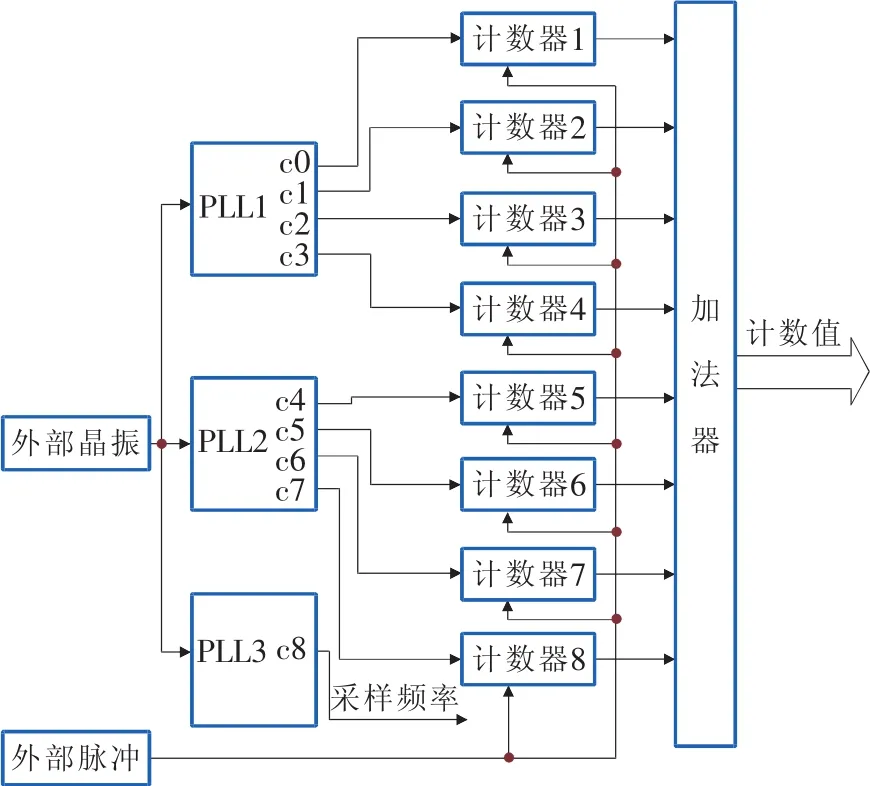

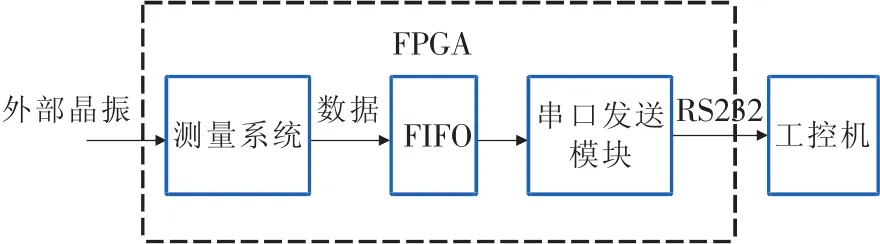

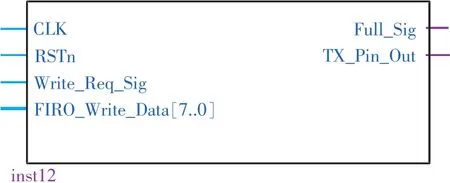

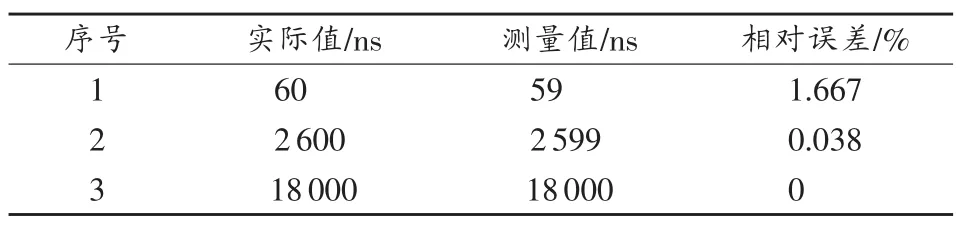

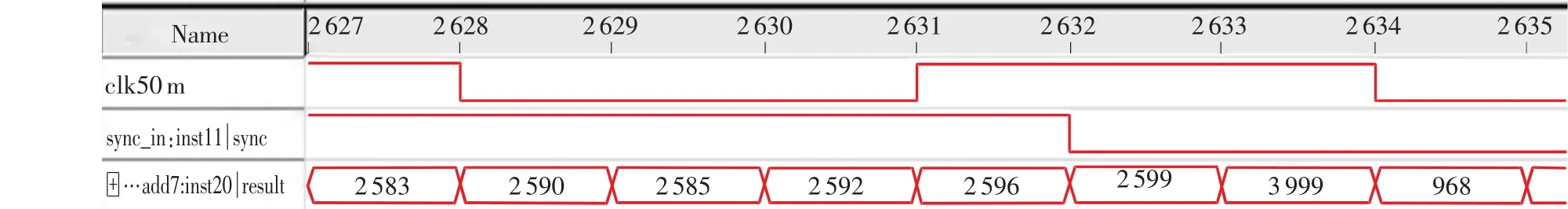

图1 直接计数法

由于FPGA内部有许多IP核,如加法器、FIFO、PLL、COUNTER已经集成,不需要进行编程可以直接设置需要的IP核,为实现各种算法提供了极大便利。FPGA锁相环模块如图2所示。PLL模块的inclk0为外部输入晶振输入端,c0为PLL模块倍频输出端口。通过对PLL模块进行设置使c0达到1GHz。计数器模块如图3所示。clock为时钟输入端,与c0相连,cin为外部脉冲输入端,sclr为清除端,在外部脉冲下降沿到来之后将计数器清0,以便对下一个到来的外部脉冲重新计数。q为32位的计数寄存器,用于储存计数结果。将计数器设置为上升沿使能从而达到本次实验所需要求[7]。为模拟产生一个外部脉冲,在FPGA内部模拟了一个高脉冲来测试搭建的测量模块,设计了一个脉冲发生器,脉冲发生模块算法流程如图4所示。图中a与b为一个常量且a 图2 PLL模块的配置 图3 counter模块的配置 图4 脉冲发生器算法 1.2 移相计数法 直接计数法使测量精度达到纳秒量级就必须使用更为高端的FPGA芯片,其性价比不高。本文介绍一种基于FPGA的移相计数法,可以用中低端FPGA实现其精度,从而极大地降低成本[7-8]。 为实现外部脉冲信号纳秒量级精确测量,本文结合数字移相技术,设计了改进型移相脉冲宽度测量技术,其优势在于FPGA无需倍频至1GHz,就能实现1ns的误差精度。由于FPGA内部锁相环(PLL)设置时钟多输出功能和各输出时钟相位功能,使得多个时钟信号输出各产生一定的相位差来等效1GHz的时钟信号。原理如图5所示。 图5 移相计数法测量原理 通过FPGA内部锁相环移相功能,FPGA的晶振所产生的50MHz时钟信号进行相邻信号依次相差45°处理,例如以第1路输出时钟信号CLK相位为0°,那么其他信号则依次为CLK45°、CLK90°、CLK135°、CLK180°、CLK225°、CLK270°、CLK315°,然后用FPGA内部锁相环多路输出功能产生这8路时钟信号,原理如图6所示。然后将8路信号分别驱动一个计数器,8个计数器分别用N1、N2、N3、N4、N5、N6、N7和N8表示。据此可以精确测量出外部脉冲宽度t,其计算公式为 式中f为8路时钟信号的频率。 对8路时钟信号所驱动的计数器的计数值进行相加相当于采用了8倍频的时钟频率为8f的信号来测量外部脉冲信号,即时钟信号的周期1/8,从而在不提高时钟频率的情况下实现精度要求,其等效的时钟信号如图6所示。由图可见,在计数时钟频率为125MHz时,这种测量方法可得到时钟频率为1GHz的等效时钟,从而使测量精度达到要求,并且大部分中低端FPGA内部锁相环都可以实现125MHz的时钟信号。文献[3]提到的4路输出移相的方法相当于PLL模块要输出250MHz的输出时钟频率,然而这种频率在中低端FPGA的锁相环倍频不是很稳定,从而使测量不精确,无法达到要求。 图6 1GHz等效的8路时钟信号 移相测量方法依然在直接计数法的基础上,等待外部脉冲到来,其上升沿使能8个计数器开始计数,等到外部脉冲下降沿到来停止计数,将8个计数值再通过FPGA内部的加法器相加,最终数值为数字脉冲宽度。总体算法框图如图7所示。 图7 总体算法 实验所使用的FPGA是在ALTERA公司的Quartus II环境下选用Cyclone IVE系列的EP4CE15F17C8芯片进行设计并仿真[9-11],此芯片锁相环(PLL)模块最多有5路时钟信号输出,因此必须使用两个锁相环模块产生8路时钟信号,其中每个锁相环产生4路时钟信号,第3个锁相环是为了产生采样频率而设置,由于每一路时钟信号的频率为125MHz,根据香农采样定理,采样频率必须不低于最大采样信号的2倍,所以经过多次实验用锁相环3产生300MHz的采样频率。8个时钟信号各自驱动计数器,等待外部脉冲到来与结束,将计数结果加和后送出。 实验依然使用锁相环模块,不过这次使用2个锁相环模块产生8路依次相差45°时钟信号,并且每路信号经锁相环倍频到125MHz。仿真如图8所示。 图8 PLL配置的8路时钟信号 图中inclk0为外部输入晶振50MHz,PLL1的c0、c1、c2、c3为频率125MHz的时钟输出,相位角分别为0°、45°、90°、135°,PLL2的c0、c1、c2、c3也为频率125MHz的时钟输出,相位角分别为180°、225°、270°、315°,从而形成8路相位依次相差45°的时钟输出来驱动计数器。其原理为在脉冲计数法基础上,采用8个计数器计数。计数器的clock分别连接锁相环的8路输出时钟信号,然后再用加法器将计数器输出值相加。 2.1 串口通信 经FPGA测量出的信号可以通过串口RS232与PC机相连传输数据,电脑上位机用LabVIEW软件开发平台开发,将测得数据显示在上位机软件上。 实验的开发板上带有串口RS232,再接一个串口与USB的转接线连接PC机,与下位机的串口通信也使用转接线来完成。FPGA与工控机或PC机的整体框架如图9所示。 整体思路是将关电开关产生的脉冲经过FPGA移相脉冲计数法处理得到精确的脉冲时间,放入FPGA内部缓冲器FIFO中,等待串口通信模块空闲时发送FIFO内的数据到PC机的COM端口,用LabVIEW设计上位机软件将脉冲时间数据显示在PC机上[12-13]。首先,必须设计一个缓存器FIFO,因为外部脉冲任意时刻都可能产生,一旦外部脉冲产生会触发8个计数器模块开始计数得到的计数结果直接通过串口模块发送,PC上将显示整个计数器计数的所有数据,所以设计FIFO就是在外部脉冲下降沿到来触发FIFO写使能,将最终计数结果存入到FIFO中等待串口发送模块发送给PC机。串口通信模块如图10所示。 图9 系统结构 图10 串口通信模块 图中FIFO模块已经集成在串口通信模块中,引脚CLK为125MHz,RSTn为复位引脚,Write_Reg_Sig为FIFO写使能,FIFO_W rite_Data为写入FIFO的数据,TX_Pin_Out为串口232发送引脚。在串口通信方面,FIFO起着非常重要的数据缓冲的作用,如果串口通信没有FIFO来缓存数据,有可能测量系统将测量的数据传输到串口发送模块时,串口发送模块处于忙状态,导致传输的数据丢失从而导致测量系统的性能变差,这在工程设计方面是绝对不允许的。 2.2 上位机设计 首先,FPGA将测量数据发送至PC机COM口,使用LabVIEW搭建一个串口接收模块,由于串口接收的是字符串,需进行处理后再送入表格中显示出来。编写的软件界面分为串口号、数据缓冲区和表格3个部分。其中串口号就是来选择FPGA串口所连接的COM口,数据缓冲区为所选串口中的数据,表格是将数据缓冲区的数据进行处理后显示的显示控件。 串口RS232每次发送一帧,每一帧为11位,包括1个起始位、1个结束位、1个校验位和8个数据位。一帧有效位为8位,然而光电开关的数字脉冲宽度在几微秒到几百微秒之间,远超过8位数据的范围,因此将FPGA测量数据设为32位以满足需求,将32位测量数据分成4组8位数据放入FIFO中等待串口发送模块传输。通过串口接收模块接收FPGA串口发送模块传输的字符串,String Subset模块截取相应的8位数据,经数值化处理过后整合成32位数字脉冲宽度,再传输至Build Table与Write to spread sheet File模块中显示。 3.1 直接计数法的结果与分析 在Quartus II环境下选用Cyclone IVE系列的EP4CE15F17C8芯片对设计进行验证,并用逻辑分析仪查看结果。如图11所示,为120 ns宽度的脉冲信号。图中clk50m为外部输入晶振50MHz,sync_in为外部脉冲信号,add1为计数器计数值。可以看出,计数器最终计数的值为132 ns与设定的外部脉冲120ns相差12ns,误差已经远远超过了1ns范围,说明实验使用的中低端PFGA芯片无法实现1ns的精度,无法直接倍频稳定1GHz的时钟信号,对于低成本测量系统来说,直接计数法不适用。 3.2 移相计数法的结果与分析 用脉冲产生模块产生60,2600,18000ns,实验结果见图12~图14。图中,clk50m是外部50MHz的晶振,sync是脉冲产生模块产生的被测量脉冲,result是8个计数器计量结果,由于选用的采样频率是300MHz,所以无法完整的从逻辑分析仪中看PLL模块倍频的125MHz,如果再提高采样频率由于这个型号FPGA自身的硬件设备原因将无法进行实验。 脉冲宽度设定值与实验测量值见表1。由表可见,比较脉冲宽度设定值与测量值可知,其误差为1ns左右,符合设计目标。 表1 脉冲宽度实际值与测量值 图11 实验结果 图12 60ns脉冲波测量结果 图13 2600ns脉冲波测量结果 图14 18000ns脉冲波测量结果 3.3 上位机界面测试 实验用FPGA内部脉冲发生器产生60 ns的高脉冲进行实验,实验结果如图15所示。图中表格中显示的数据跟Quartus II的逻辑分析仪显示的被测数据一致,足以证明串口发送模块设计的准确性,其中数据缓冲区3B为字符串16进制显示,转化成10进制数值就是表格Table中的数据。 图15 60ns实验结果 虽然本文实现了对FPGA测量数据可视化显示,但是一旦关闭工控机软件显示在表格中的数据也会随之消失,无法对测量数据进行保存。LabVIEW则提供了数据保存相关的集成模块能将测量系统传输的数据及时保存。通过编程在工控机软件基础上采用Excel来保存系统测量数据,并且测量数据能实时传输到Excel中,且在工控机软件关闭的情况下,会将测量数据紧接着上组数据下方进行储存。实现保存测量数据的功能。 针对基于FPGA设计的两种脉冲宽度测量方法,直接计数法虽然原理较为简单,但是一般中低端FPGA很难能倍频1GHz时钟信号,高端FPGA虽然能实现算法,但成本过高。 在基于直接计数法的基础上,改进了第一种算法的局限性,设计了基于移相测量算法,其优点为锁相环模块不需要直接倍频到1GHz,通过8路时钟信号依次相差45°来等效1GHz的时钟信号,每一路时钟信号仅125MHz频率,使得多数中低端FPGA的锁相环模块都可以得以实现,极大地降低了整个测量系统的成本。 在串口通信方面,采用了简单可靠的串口RS232的数据传输方式,实现了与工控机之间的基本通信,这种方式优点突出,可靠性高、成本低、易实现,但是有线通信的局限性比较突出使得工控机必须在一定范围内,距离过远会影响通信质量。随着工程需求可以进一步将有线串口通信改成无线通信,能符合大部分工程需求。 LabVIEW是一种G语言编写模式,图形化编程对于编程人员来说易上手,可以节约大量开发时间,并且在做测量系统方面有着较大优势,有很多集成好的模块可以直接应用,例如串口通信模块,通过LabVIEW编写工控机实现PFGA测量数据的传输,实现了整个测量系统的功能。 [1]苌凝凝,鲁昌华,刘春.纳秒级周期脉冲信号检测方法的研究[J].电子测量与仪器学报,2006,20(4):86-101. [2]郭小明,苏进喜,罗承沐,等.纳秒级脉冲电压的电光测量[J].清华大学学报(自然科学版),1997,37(4):65-67. [3]仵晓辉,师廷伟,金长江.基于移相技术的脉冲宽度精确测量方法及FPGA实现[J].周口师范学院学报,2012,29(2):108-109. [4]王珏,张适昌,严萍,等.用自积分式罗氏线圈测量纳秒级高压脉冲电流[J].强激光与粒子束,2004,16(3):399-404. [5]ZHANG Y B,JI F,LIU G M,et al.Communication between industrial computer and micro-energy pulse power supply with nanosecond pulse width[C]∥International Conference on Advanced Technology of Design and Manufacture.ATDM,2010:413-418. [6]STENHLM T J,SOINI JT,HÄNNINEN P E.A long-arm autocorelator for measurement of pico-to nanosecond laser pulse widths[J].Measurement Science and Technology,2004,15(10):1525-1531. [7]张志刚.FPGA与SOPC设计教程:DE2实践[M].西安:西安电子科技大学出版社,2007:57-65. [8]陈传波,杜娟,张智杰.WIN32下基于RS232C协议的串口通信方法及应用研究[J].南昌大学学报(工科版),2005,27(3):71-76. [9]杨建伟,郑琼华,沈昱明.基于LabVIEW的数据保存[C]∥第八届工业仪表与自动化学术会议论文集.上海:中国仪器仪表学会,2007:485-489. [10]陈锡辉,张银鸿.LabVIEW 8.20程序设计从入门到精通[M].北京:清华大学出版社,2007:97-115. [11]施雅婷,郭前岗,周西峰.一种改进的LabVIEW串口通信系统的实现[J].电子测试,2010,8(8):64-70. [12]HAN X H,KONG X X.The designing of serial comm unication based on RS232[C]∥ACIS International Symposium on Cryptography,and Network Security,Data Mining and Knowledge Discovery,E-Commerce and Its Applications,and Embedded Systems.IEEE,2010:382-384. [13]MACHACEK J,DRAPELA J.Control of serial port(RS-232)communicaton in LabVIEW[J].Modern Technique and Technologies,2008(37):121-127. (编辑:李妮) A nanosecond level measurement method of pulse w idth based on FPGA YU Longyang,LIU Ye,SUN Peiqin,ZHANG Yaoyun In order to make the width of digital pulse generated by photoelectric switch reach the precision of 1ns approximately grasp the real-time working state of the photoelectric switch.This paper proposed two FPGA-based accurate measurement methods to measure the precision,directing counting method and phase shift counting method were included.The experiments show that the error of the phase shift counting method is about 1 ns,which verifies its correctness and effectiveness.The communication system and software of IPC were also designed in this paper.The communication system used a RS232 serial interface and the serial communicationmodule transfers data to the IPC was designed by FPGA;IPC software was written by LabVIEW,which enables the data to be observed intuitively and stored to Excel easily.The experimental results show that the design of the system is correct and effective. nanosecond;FPGA;serial communication;LabVIEW A 1674-5124(2017)05-0005-06 10.11857/j.issn.1674-5124.2017.05.002 2016-09-18; 2016-11-20 于龙洋(1992-),男,陕西宝鸡市人,硕士研究生,专业方向为控制理论与科学。

2 测量系统设计

3 实验结果与分析

4 结束语

(School of Electrical Engineering,Xi’an Jiaotong University,Xi’an 710049,China)