多位BCD—B码转换几种方法及其实现

2016-09-27周致杨斌

周致+杨斌

摘 要:目前,在数字电路中应用最为广泛的是B码和BCD码,而作为人机交互的重要组成部分,BCD-B码的转换显得尤为重要。进制转换方法有计数法、组合逻辑法和移位修正法等,本文将以三位BCD转十位B码为例,探讨基于数字芯片的BCD-B码的转换问题。

关键词:BCD-B;计数法;组合逻辑

一、引言

在数字电路中,最广泛使用的进制转换方法有计数法、组合逻辑法和移位修正法等,转换实现形式有软件和硬件两种。软件形式虽然实现较为简单且可以节省资源,但转换时间相对过长;而基于硬件的转换虽然增加了硬件数量,但转换速度大为提高。[1][2][3]

二、基于计数法的BCD-B码转换

1.转换原理

虽然B码和BCD码在进制表示上不同,但对同一个数进行表示时,其真值却是相同。基于这个原理,利用加、减计数器,将待转换的m组BCD码输入十进制减法计数器组中,并将n位二进制加法计数器组清零。然后,启动两计数器组同步计数。当减法计数器中的BCD值递减为零时,停止计数,此时加法计数器中的累加值即为转换后的B码结果。

2.方法实现

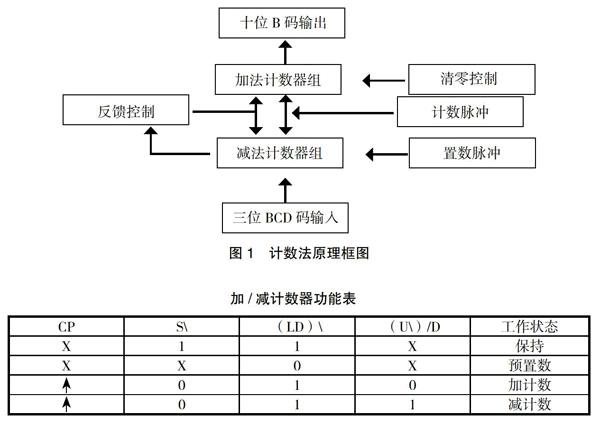

BCD-B码转换采用计数法原理,主要包括减法计数器组、加法计数器组、计数脉冲控制、清零控制、置数脉冲控制和反馈控制等部分,其原理框图如图1所示。

本文选用同步十六进制加/减计数器74LS191和同步十进制加/减计器74LS190作为组成计数法加/减计数器组的主芯片,其功能表如表所示。

根据计数法原理进行电路连接。由于三位BCD码最大表示1001 1001 1001(999),所以减法计数器组的电路由三片74LS190采用异步十进制方式级联组成三位BCD码的减法计数器。将三位BCD码I10~I33分别并行输入。计数开始后,74LS190开始减法计数,当三片减法计数器中数值全部减为0后,输出信号先后通过三个四输入或非门和一个三输入与门通过运算产生保持信号,使计数器停止计数。

加法计数器组电路由三片74LS191采用异步二进制级联组成十位B码的加法计数器。开始时计数器组首先清零,然后与减法计数器组在同一计数脉冲控制下进行同步计数。当减法计数器内数值减为0时,接收保持信号,将置1,停止计数,此时输出的B码即为转换结果。

3.电路分析

采用计数法构成的BCD-B转换电路原理简单,使用芯片数量中等,实现难度中等。但由于计数法转换过慢,特别是在进行较大BCD码的转换时耗时过长,因此不具备转换优势。

三、基于组合逻辑法的BCD-B码转换

1.转换原理

将上述六组十位二进制数依次累加,累加结果即为十位自然B码。

2.方法实现

将十位二进制数累加五次需要用五级十位全加器。然而,由于“0”与任何数相加都等于原数,在实际运算过程中,某些位上的“0”可以不参与累加,只将非零位累加输出。所以,五次累加只需用五级四位全加器便可实现,其原理框图如图2所示。

本文选用5片4位加法器74S283芯片作为主执行单元,根据组合逻辑法原理进行电路连接。输入三组BCD码按照“左移乘2”一般原理转变为六组变形十位B码。其非零位即为原BCD码各位上对应的基数经过移位产生。含“0”位因在累加过程中对实际结果不起作用,在实际累加时,某位与“0”的相加则转变为该位直接输出,参与下次累加或最终输出。

3.电路分析

采用组合逻辑法构成的BCD-B码转换电路,使用芯片数量最少,实现难度最低。而且在转换过程中时序要求低,转换速度在各转换方法中最快,因此具有高性能。

四、结论

本文通过计数法和组合逻辑法两种转换方法实现了BCD-B码的转换。计数法原理简单,耗费芯片数量中等,但转换速度不一,对较大数进行转换时速度过慢,导致转换效果不理想。而组合逻辑法耗费芯片数量最少,转换速度稳定而且为最快,能够较好地实现BCD-B码的转换。这两种转换方式各有优缺点,希望能为BCD-B码的转换方式选择提供参考。

参考文献:

[1]清华大学电子学教研组编.数字电子技术基础(第五版)[M].北京:高等教育出版社,2006:5.

[2]卢 毅,赖 杰.VHDL与数字电路设计[M].北京:科学出版社,2001.

[3]廖裕评,陆瑞强.CPLD数字电路设计[M].北京:清华大学出版社,2001.