基于FPGA和LabVIEW的虚拟频率特性测试仪设计

2016-12-06郭睿楠王义涛

郭睿楠, 李 冶, 王义涛

(吉林大学 仪器科学与电气工程学院,吉林 长春 130026)

基于FPGA和LabVIEW的虚拟频率特性测试仪设计

郭睿楠, 李 冶, 王义涛

(吉林大学 仪器科学与电气工程学院,吉林 长春 130026)

为了提高数据分析处理能力和充分利用计算机资源,设计了一种基于现场可编程门阵列(FPGA)和LabVIEW开发环境的虚拟频率特性测试仪。遵循模块化理念搭建了以单片机为控制单元,USB芯片为通信单元的硬件电路,FPGA实现数据存储和时钟控制等功能,提高了电路的集成度。采用数据流思想,在图形化编程软件LabVIEW中开发了人机交互界面,可以操作仪器发出扫频信号,显示频率特性曲线,还能对数据进行分析,得到用户感兴趣的参数,同时支持数据的存储功能。实验结果表明,仪器能够满足教学领域的要求。与同类设计相比,该方案具有成本低,灵活性高等优点。

现场可编程门阵列; 频率特性测试仪; 虚拟仪器; LabVIEW

0 引 言

传统的电子测量仪器是由厂商制造,采用固化的系统软件和固定的硬件电路的测试设备,其系统封闭,扩展性能差。虚拟仪器以计算机为核心平台,选取基本的测试硬件作为信号的接口,灵活度高,开发维护成本低[1]。

电路在输入正弦信号情况下,输出随输入信号频率连续变化,这种变化关系称为电路的频率特性[2]。频率特性由幅频特性和相频特性组成,是重要的测试参数。传统的频率特性测试仪利用示波管的电子束显示图像,电子束在水平方向受扫频信号影响,在垂直方向受被测信号幅度和相位影响。传统测试仪的生产成本高,且在数据采集分析处理方面存在不足。本文介绍的虚拟频率特性测试仪,采样率高,信号带宽大,能满足大部分被测信号需求,利用FPGA实现数据缓存和时钟控制等功能,使用LabVIEW编辑的上位机软件可完成数据分析处理的功能,充分利用了计算机资源,降低了硬件成本。

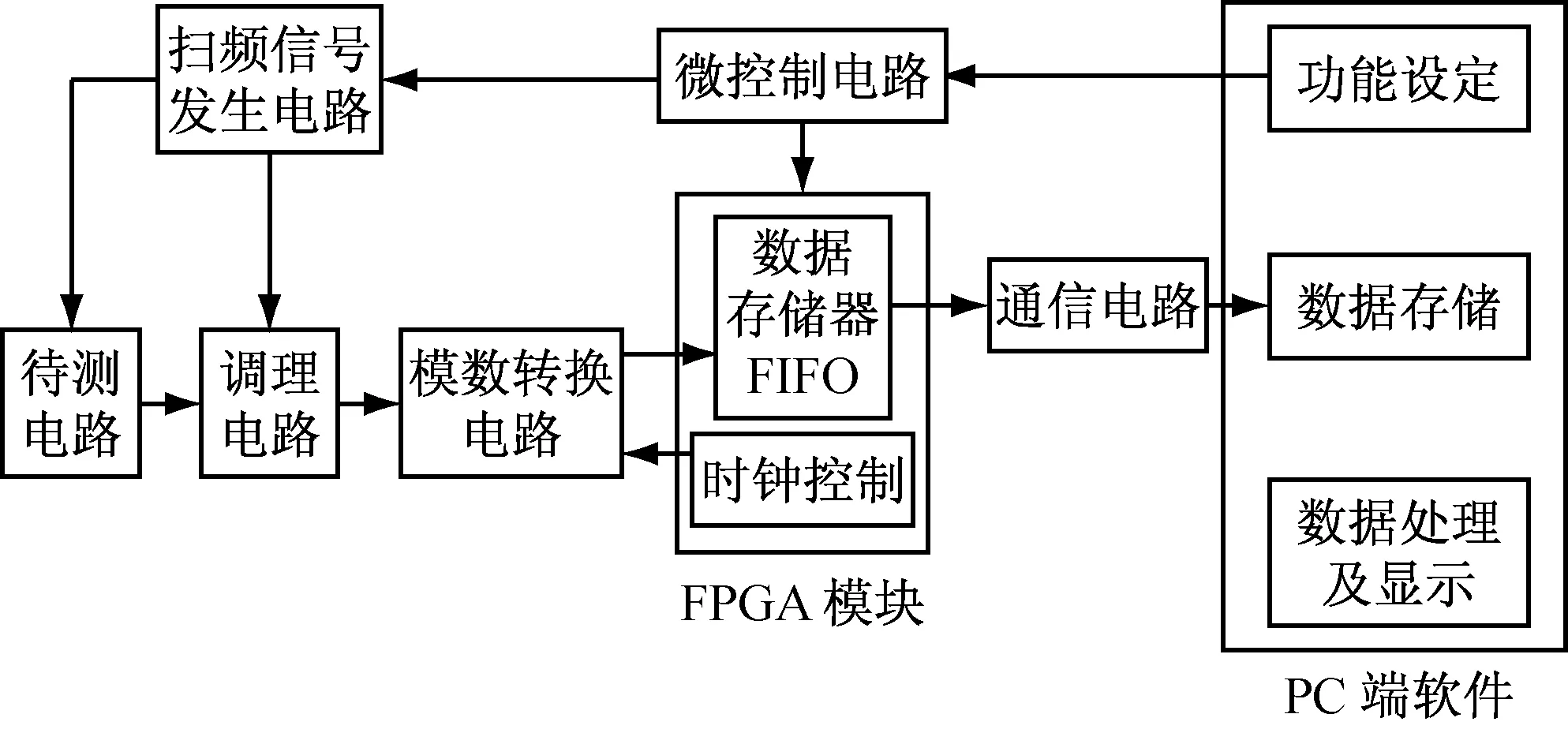

1 虚拟频率特性测试仪总体结构

图1为虚拟频率特性测试仪总体结构,扫频信号发生电路用作激励信号源,激励信号和待测电路的输出信号在调理电路中被衰减和滤波,而后经过模数转换,存储于由FPGA实现的数据存储器中,最后这些数据经由通信电路上传到PC机中,由仪器操作软件进行分析处理,并将幅频特性曲线图、相频特性曲线图及相关特性参数呈现给使用者。此外,对仪器进行功能设置也是由PC机软件完成的。在该过程中,PC机软件起到总体控制的作用,仪器微控制器则起到协同管理的作用。仪器的各硬件模块均集成在标准3U尺寸的电路板上[3],使用直流电流源供电,通过USB线与PC机连接。

图1 虚拟频率特性测试仪总体结构

2 虚拟频率特性测试仪硬件设计

2.1 调理电路

虚拟频率特性测试仪的调理电路有两条通道,通道A用于接入由仪器自身或外部其他仪器产生的扫频信号,通道B用于接入待测电路的输出信号。调理电路由衰减电路和驱动放大电路两部分组成[4]。模数转换电路所使用的模数转换芯片AD9288要求输入信号幅值小于0.5 V,因此衰减电路的作用是将输入信号电压调整到模数转换芯片的输入电压范围内。考虑到扫频信号频率较大时,电路中的分布电容会使输入信号失真,衰减电路采用补偿分压电路和直接电阻分压电路相结合的方案;又考虑到外部其他仪器产生的扫频信号幅值可能比本仪器自身产生的要大,衰减电路设计了1,10,20和50倍四个档位,档位的切换由微控制器通过FPGA调节继电器开闭来实现。AD9288有差分输入的要求,因此在衰减电路后面设计了驱动放大电路。将经过衰减电路的信号一路直接接入AD9288差分输入其中一个引脚;另一路经过驱动放大电路接入差分输入另一个引脚,以此来完成对于AD9288差分输入的目的。驱动放大电路选用TL072D放大器,TL072D是一款JFET输入运算放大器,它的功耗低,输入共模和差模电压范围宽,输入偏置电流和输入失调电流小,谐波失真小,噪声低,电压转换速率高达13 V/μs,带有输出短路保护,完全能够满足本仪器需求。

2.2 模数转换电路

仪器选用1片AD9288-100作为模数转换芯片[5]。芯片每个通道采用差分输入,这样就减小了模数转换电路的误差,提高了模数转换电路识别小信号、抗干扰和处理双极信号的能力。AD9288的两个通道分别接入经处理的扫频信号和待测电路输出信号,两通道的基准电压输入引脚接入芯片内部基准电压。FPGA模块为芯片的两个通道提供时钟信号。出于数据处理的需要,要求芯片的数字输出格式为偏移二进制码,即将芯片的S1引脚置为高电平;S2引脚置为低电平;DFS引脚置为低电平[6]。模数转换电路的数字输出接入FPGA电路。

2.3 FPGA模块

仪器选用Altera公司Cyclone系列的EP1C3T144C8N作为FPGA模块的核心芯片,FPGA模块采用自顶向下的设计思想,使用Quartus II开发,利用VHDL语言编写[7]。FPGA模块实现了时钟控制,数据存储器等功能。

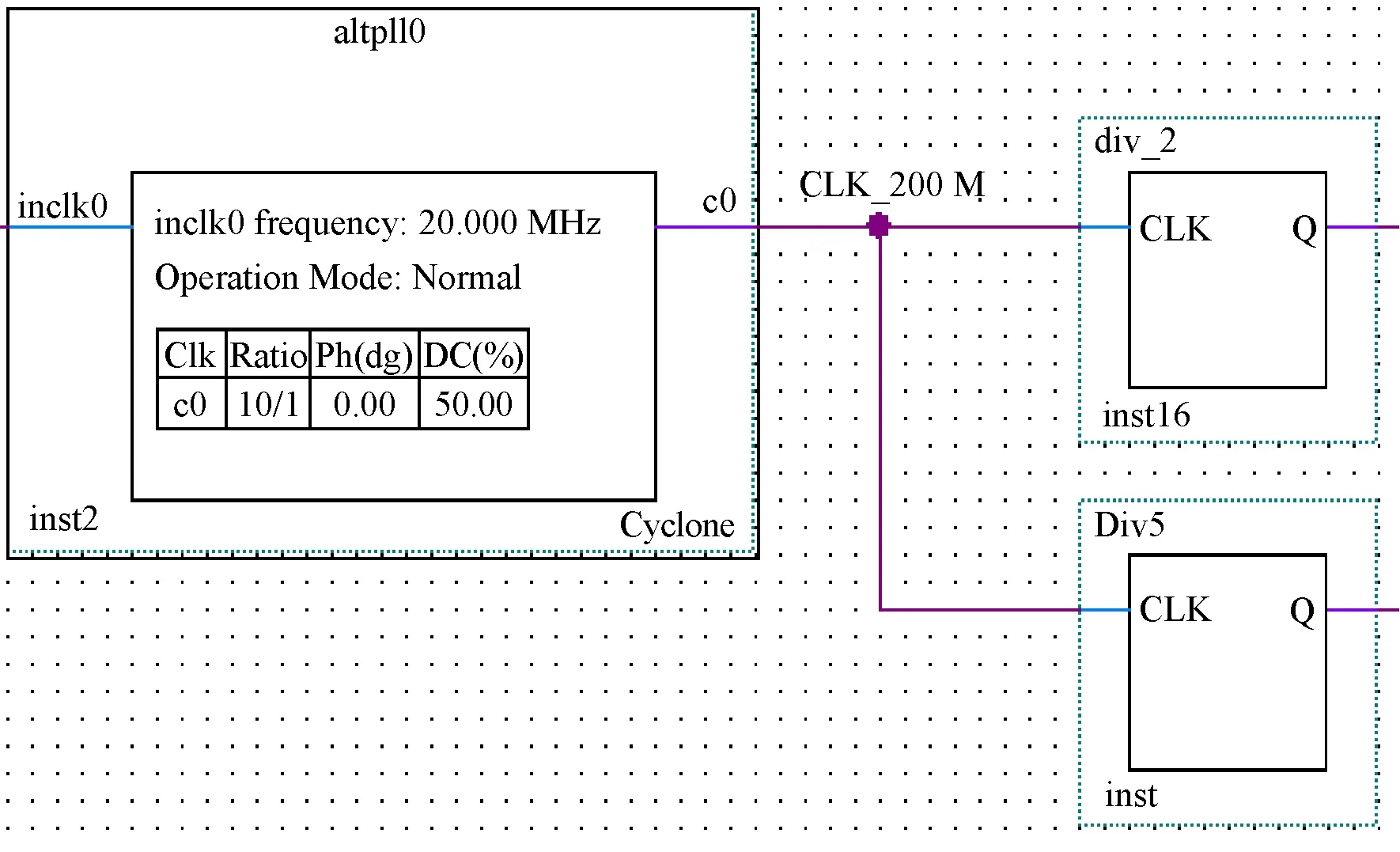

时钟控制功能是将外部晶振的20 MB时钟接入FPGA,由锁相环倍频到200 MB,再分频成各模块所需要的时钟[8],如图2所示。

图2 时钟控制模块局部

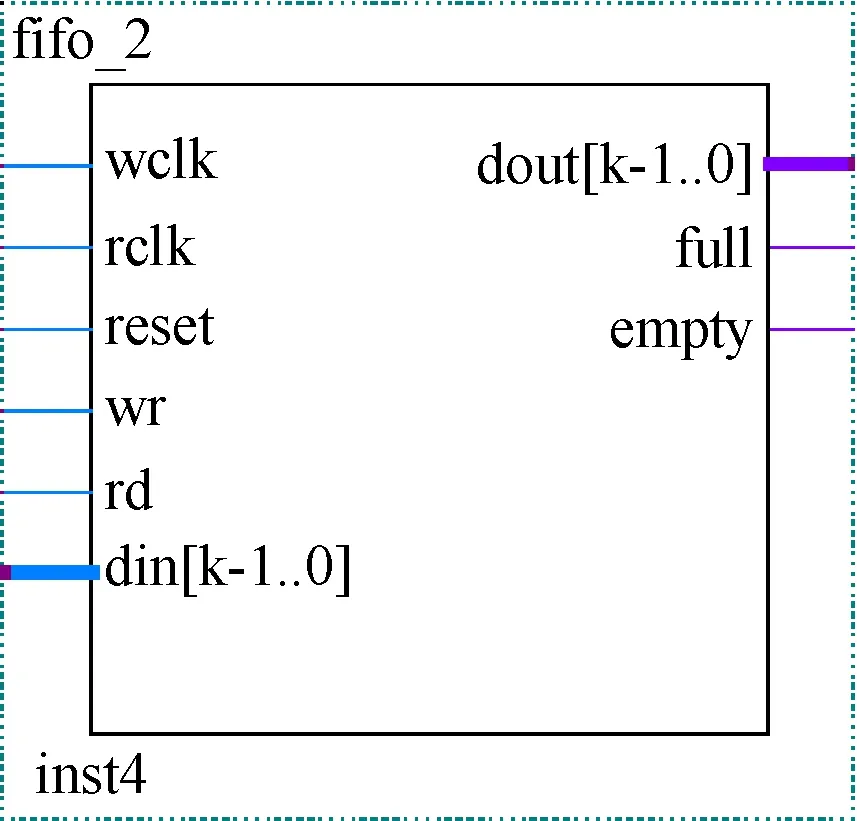

由FPGA实现的数据存储器为FIFO类型[9],即先入先出型存储器。模数转换电路采集到的数据首先暂存到FIFO存储器中,而后当PC机软件下达从硬件读取数据的命令时,FIFO存储器的数据再被上传到PC机中。本仪器为扫频信号输入通道和被测电路输出信号通道分别配置了一块容量为2 kB的FIFO,其外观如图3所示。

图3 FIFO存储器外观模型

除此之外,FPGA模块还有控制调理电路衰减部分的继电器,以及实现扫频信号电路所需地址发生器等功能。

2.4 扫频信号发生电路

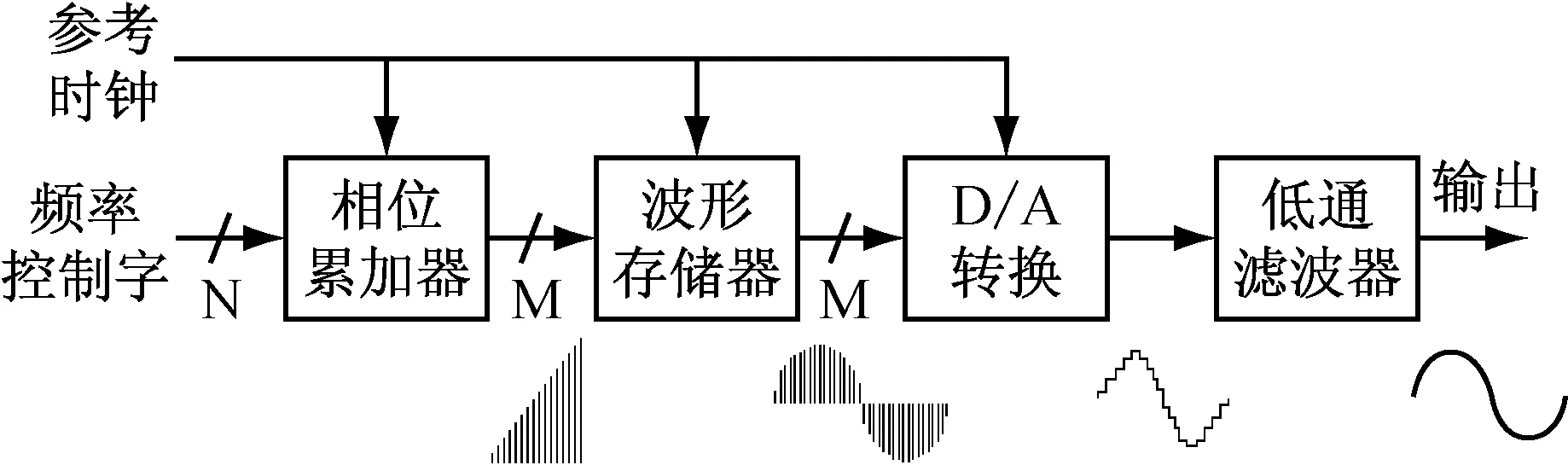

本仪器通道C为内置扫频信号发生通道。扫频信号发生电路应用了直接数字频率合成(Direct Digital Synthesizer,DDS)技术,它的原理如图4所示。DDS技术是先将一个相位与幅度相对应的波形表存放在存储器中,再通过一个地址发生器对波形表中的数据寻址读出,最后将读出的数据经过数模转换和低通滤波获得所需要的波形[10]。本仪器的波形存储器使用SRAM芯片CY7C1021CV,模数转换芯片使用DAC902,地址发生器由FPGA电路实现。

图4 DDS技术原理框图

2.5 微控制器电路及通信电路

本仪器的微控制器由单片机89S52实现,单片机程序使用Keil编写。仪器运行时,通信电路将由PC机发送来的命令ID传输给单片机RAM,单片机读取RAM数据并执行与命令ID相对应的函数。单片机的数据线及地址线与电路各关键控制端口相连,以实现对仪器整体的控制。

仪器通信电路采用Cypress公司EZ-USB FX2系列的CY7C68013芯片来实现[11]。该芯片的微处理器程序基于Cypress公司提供的完整固件程序架构[12],依照仪器需求添加其他端点收发数据的代码后,该芯片即成为与仪器运行模式相契合的通信模块。

3 软件设计

虚拟频率特性测试仪软件由前面板和程序框图两部分组成,前面板由LabVIEW多种显示控件组成,用于设置仪器各项参数、反馈仪器状态及观察频率特性有关的数据和波形。程序框图由节点和数据连线构成,节点之间由数据连线按照一定的逻辑关系相互连接[13]。软件具体包括波形显示、波形观察工具、仪器状态显示、仪器参数设置、通信和数据处理部分。

3.1 软件流程图

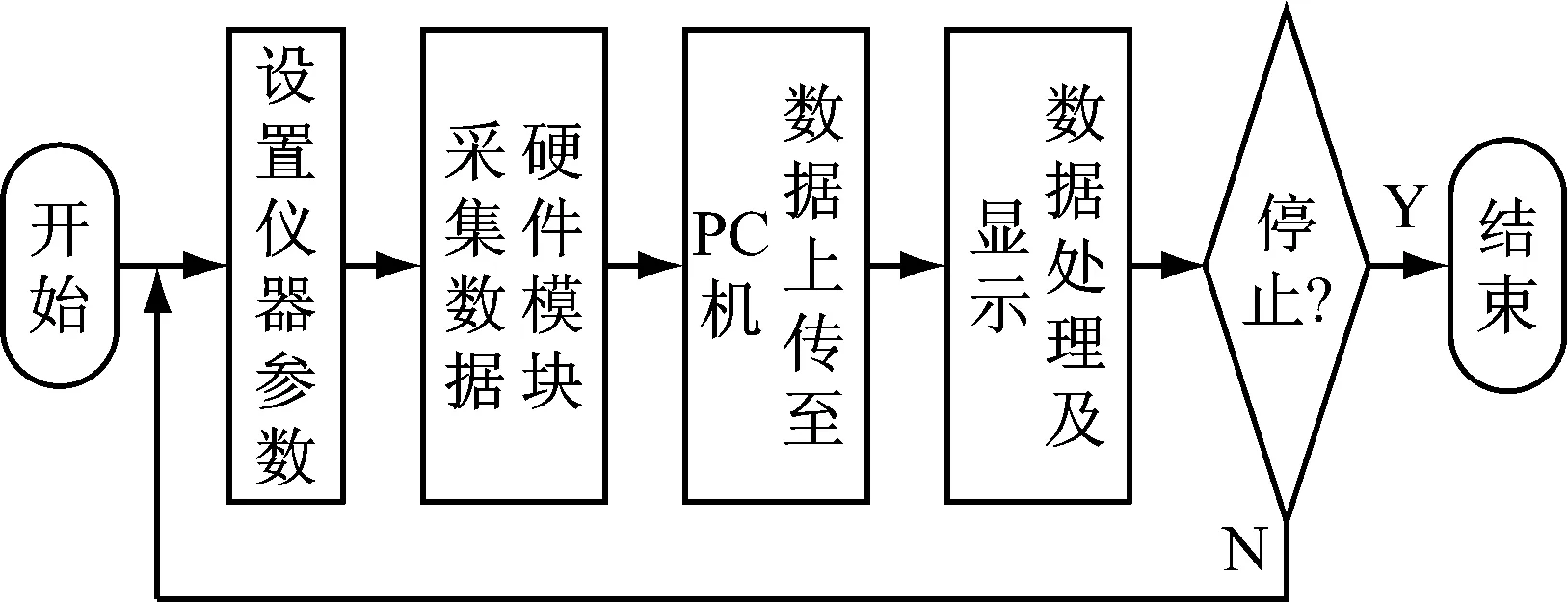

如图5所示,首先运行PC机软件,在前面板对仪器各项参数进行调整,软件通信模块完成参数在仪器硬件上的配置,硬件按照软件前面板设定的参数要求发射和采集信号,采集到的数据经由USB线发送到PC机,软件通过对采集到的数据进行处理,将被测网络频率特性曲线及有关数据显示在PC屏幕上。每完成一次数据采集处理后,软件都会判断停止键是否被按下,若被按下,则结束程序;若未被按下,则重复前面的运行过程。

图5 软件流程图

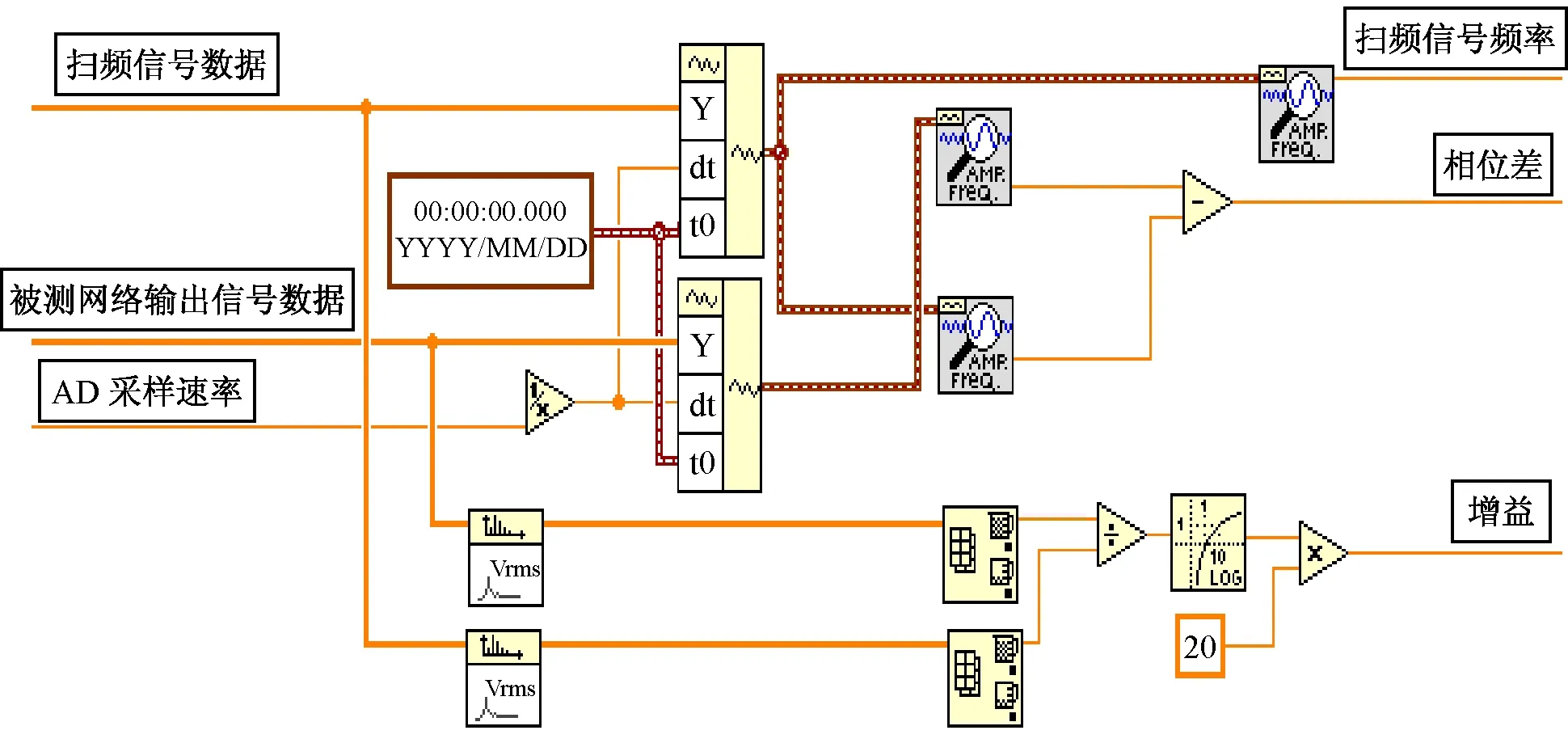

3.2 数据处理与显示

上传到PC机的是扫频信号和被测网络输出信号的时间序列,还需要软件进行处理,如图6所示。软件采用快速傅里叶变换获取信号幅度谱,其中的一次谐波幅值即为当前频率下该信号的幅值,再利用两信号幅值计算得到用于表达待测网络幅频特性的增益。软件利用带汉宁窗的快速傅里叶变换获取信号频谱[14],再将频谱结合模数转换器采样率进行处理,得到扫频信号频率及两信号的相位,两信号的相位差即是用于表达网络相频特性的量。

图6 数据处理方式

对于已经得到的相位差和增益数据,采用如图7的方式将其转化为波形显示。将每次得到的新增益或新相位差和与之对应的扫频信号频率分别添加到FOR循环结构的两个移位寄存器数组中,再将两移位寄存器数组捆绑成簇,并接入XY图显示控件[15],这样就实现了幅频特性曲线图和相频特性曲线图随扫频信号频率变化,逐点显示出波形的功能。XY图显示控件还为用户提供了可以放大、缩小及移动波形等处理功能。

图7 波形显示方式

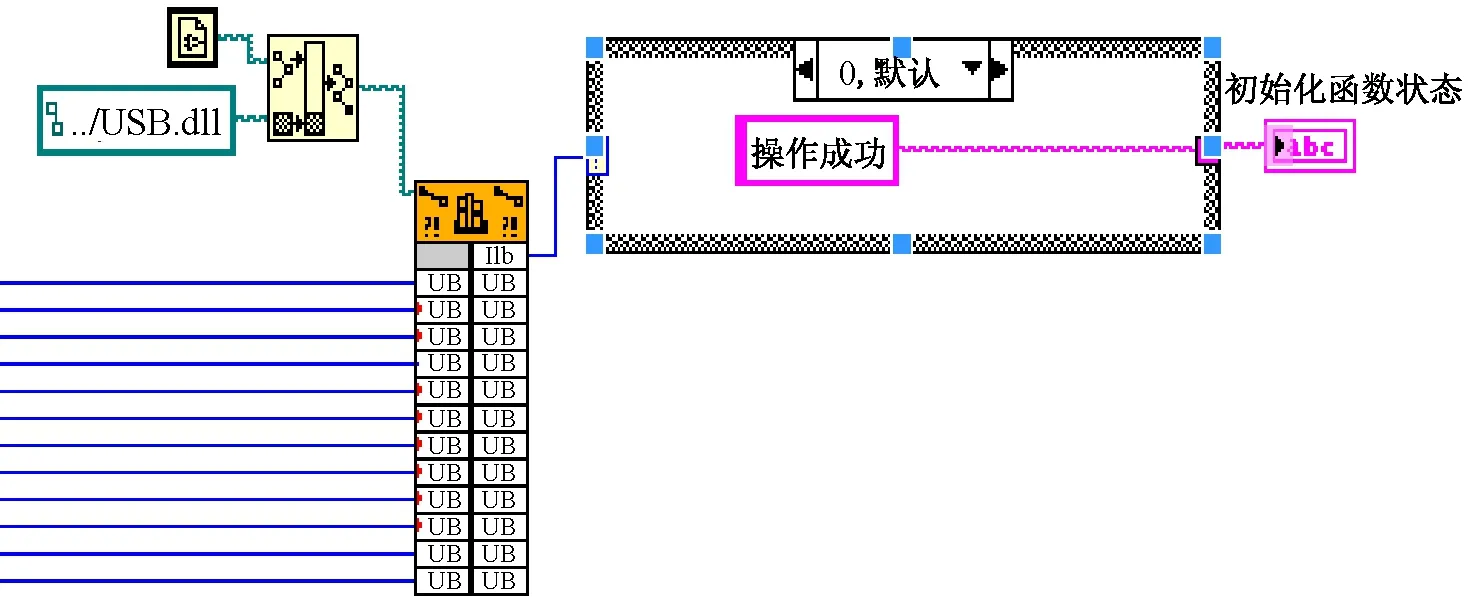

3.3 软件通信模块

软件通过使用LabVIEW的“调用库函数节点”控件来完成与硬件的通信[16],如图8所示。该控件所需的动态链接库使用VC++6.0生成,其关键代码首先通过调用win32函数CreatFile()得到通信电路驱动程序的句柄,然后调用win32函数DeviceIoControl(),经由得到的句柄把I/O Control Code和相关的输人输出缓冲区提交给驱动程序,进而实现通信。

图8 调用库函数节点

4 测试结果

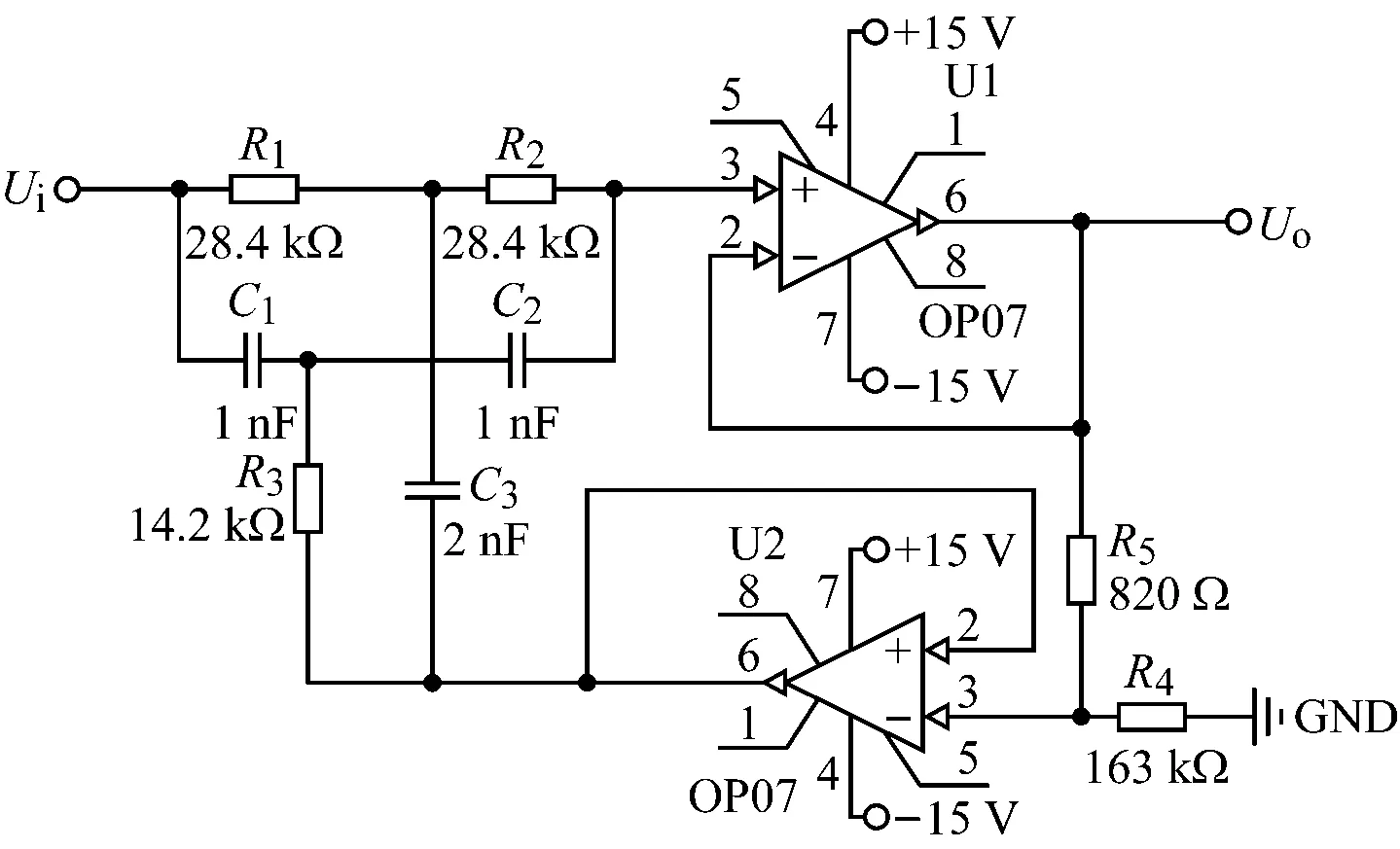

测试电路为双T双跟随陷波器,电路如图9所示,其中心频率约为5.6 kHz,带宽约为1 kHz。虚拟频率特性测试仪的内置扫频信号发射通道与扫频信号输入通道和待测网络的输入端相连,待测网络的输出端与

图9 双T双跟随陷波器

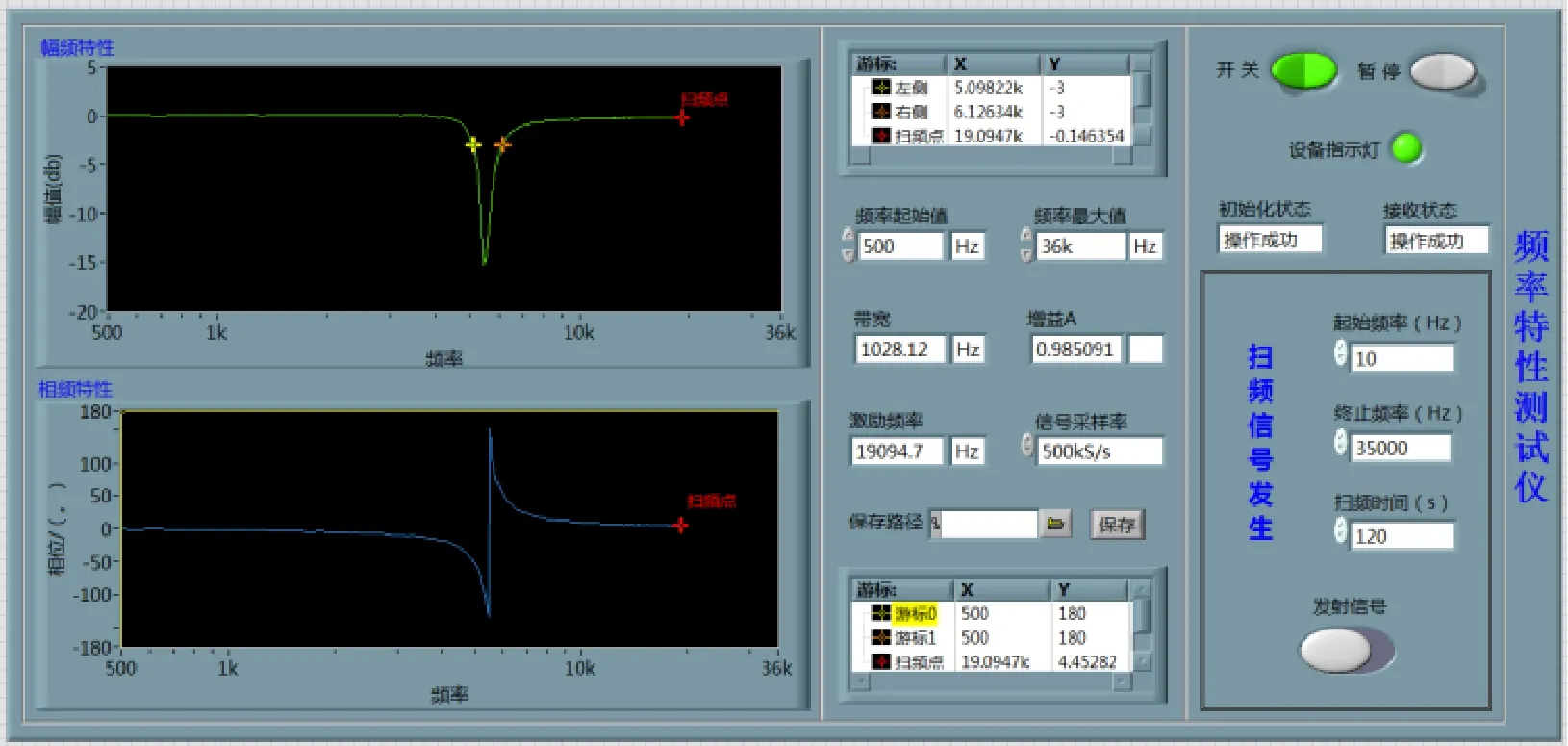

虚拟频率特性测试仪的待测信号输入通道相连。测试结果如图10所示,得到的幅频特性曲线和相频特性曲线与实际一致,基本满足要求。

图10 软件界面及测试结果

与传统频率特性测试仪相比,本虚拟频率特性测试仪有以下优点:①可依据用户不同需求对波形进行放大、缩小和移动等操作,人机交互界面友好;②系统易于维护和拓展功能,开发效率高;③系统充分利用PC机资源来处理数据,采样率高,成本低廉。

5 结 语

本文介绍了一种基于FPGA和LabVIEW的虚拟频率特性测试仪设计。该仪器除了实现传统频率特性测试仪显示和存储波形的功能外,还具有协助用户细致观察和分析频率特性的功能。仪器硬件部分采用AD9288芯片实现了高采样率,利用FPGA实现了时钟控制与数据存储器等功能;仪器软件部分使用LabVIEW编写数据处理功能强大,交互界面友好的软件。试验表明,该仪器稳定可靠,能够满足测试要求,具有操作简洁灵活等特点。

本仪器成本低,易于调试和维护,具有开放性,既可通过升级硬件亦可通过升级软件来提高性能,可预见该虚拟频率特性测试仪在教学中有良好的前景。

[1] 陆绮荣. 基于虚拟仪器技术个人实验室的构建[M]. 北京:电子工业出版社,2006:8-10.

[2] 宗荣芳. 基于虚拟仪器技术的频率特性测试仪[D]. 南京:南京理工大学,2008.

[3] 韦建荣. 可重构测控系统的研究与设计[D]. 长春:吉林大学,2005.

[4] 何 达. 数字频率特性测试仪的优化设计[D]. 武汉:华中师范大学,2013.

[5] 缪军同,鲁新平. 模数转换器AD9288及其应用[J]. 山西电子技术,2006(5):42-49.

[6] 白炳良,王灵芝. 基于PIC及FPGA的简易信号分析仪设计[J]. 大学物理实验,2015,28(1):14-18.

[7] 耿三钧. 基于FPGA的多平台虚拟仪器研究设计[D]. 武汉:武汉理工大学,2009.

[8] 徐龙飞. 基于FPGA的数据采集系统[D]. 太原:中北大学,2014.[9] 李洪革. FPGA/ASIC高性能数字系统设计[M]. 北京:电子工业出版社,2011:49-51.

[10] Langlois J M P, Al-Khalili D. A Low Power Direct Digital Frequency Synthesizer with 60 dBc Spectral Purity[C]//Proceedings of the 12th ACM Great Lakes Symposium on VLSI. New York: ACM, 2002: 166-171.

[11] 胡 宁,屈 勇,蒋文峰,等. 虚拟仪器通用USB接口设计[J]. 实验室研究与探索,2014,33(10):41-45.

[12] 李 鉴,黄大勇. 基于CY7C68013的USB数据采集系统[J]. 微计算机信息,2009,25(1-1):97-98.

[13] 周 鹏,许 钢,马晓瑜,等. 精通LabVIEW信号处理[M]. 北京:清华大学出版社,2013:12-14.

[14] 林春方. 电子测量与虚拟仪器技术教程[M]. 合肥:安徽大学出版社,2008:206-210.

[15] Yan Li. The Reality of Data Acquisition System Based on Virtual Instrument[C]//Proceedings of 2011 IEEE International Conference on Information Theory and Information Security. Hangzhou:ICITIS,2011:83-87.

[16] 刘景峰. 基于LabVIEW的数据采集与多功能分析系统设计[D]. 太原:中北大学,2015.

Design of Virtual Frequency-characteristic Measuring-testing Instrument Based on FPGA and LabVIEW

GUORui-nan,LIYe,WANGYi-tao

(Instrumentation and Electrical Engineering, Jilin University, Changchun 130026, China)

Aiming to enhance the ability of data processing and take full advantage of computer resources, a virtual frequency-characteristic measuring-testing instrument is designed based on field programmable gate array (FPGA) and under development environment of LabVIEW. Following the idea of modularity, the hardware circuit is constructed with a microcontroller as control unit, and a USB chip is used as the communication unit, in which FPGA realizes functions such as data storage and timing control, and improves the circuit’s integration. Adopting the thought of dataflow, an interactive interface is developed in the graphical programming software of LabVIEW, it contains functions of operating the instrument to generate swept-frequency signal, displaying frequency-characteristic curve, analyzing data to acquire parameters that interests users and supporting data storage capabilities as well. Experimental results show that the instrument can meet requirements in the field of teaching. Compared with similar designs, this project has many advantages, for instance, low cost and high flexibility.

field programmable gate array (FPGA); frequency-characteristic measuring-testing instrument; virtual instrument; LabVIEW

2015-08-27

郭睿楠(1989-),男,吉林长春人,硕士生,主要研究方向为虚拟仪器。Tel.:13596435587;E-mail:kskmfl@163.com

李 冶(1958-),男,吉林长春人,教授,硕士生导师,主要研究方向为虚拟仪器。Tel.:13039311688;E-mail:lye@jlu.edu.cn

TM 933

A

1006-7167(2016)05-0101-04