基于CORDIC算法的改进的平方环设计

2016-10-22荆黎明

荆黎明

(河海大学计算机与信息学院,江苏南京211100)

基于CORDIC算法的改进的平方环设计

荆黎明

(河海大学计算机与信息学院,江苏南京211100)

在数字通信中,载波恢复电路是非常重要的电路环节,而其中的平方环变换以其电路的简单受到了广泛的使用。为了进一步简化该电路结构,提出了一种改进的平方环电路,这种改进的平方环省去了2分频电路,同时在文章中作者进一步改进了这个电路,将其中的多个乘法器用CORDIC算法来实现,该算法仅使用移位运算与加法器,便于流水线结构实现,降低了电路的复杂特性。最后,将该改进的电路联合ISE14.7和Modelsim10.1a进行仿真,恢复出了输入信噪比分别为6 dB和80 dB下的载波信号,验证了该电路的可行性。

载波提取;NCO;CORDIC算法;ISE;Modelsim

在电台互相通信时,要正确地接收对方的信息,接收方必须从接收信号中恢复出载波信号,使双方载波的频率、相位一致,这就是所谓的载波同步[1]。而载波同步的方法中,我们比较常用的是直接从接收到的信号中提取,也就是载波提取电路,比较常用的有平方变换法和科斯塔斯锁相环,而平方变换法以其电路结构的简单而得到了广泛的使用。

在传统的平方环电路中,在环路锁定过程中,从NCO输出的信号是两倍的载频,需要经过一个二分频电路才能提取到载频信号。但是二分频电路在实现过程中,特别是对NCO进行数字分频时,电路很复杂,用FPGA实现时会消耗许多资源[2]。同时,电路中由于使用了较多的乘法器,也会消耗很多资源。

因此本文中提出了一种基于CORDIC算法的改进的平方环电路,既避免了二分频电路,同时又优化了乘法器的结构,可以实现从输入BPSK信号中提取载波的功能,结构简单,并且对其进行了仿真,验证了其可行性、运行速度快和易于实现的优点。

1 锁相环及其平方变换法的原理

1.1锁相环的工作原理

锁相环是一个相位的负反馈控制系统,虽然有各种形式的环路模型,但是最基本的还是由鉴相器(PD)、环路滤波器(LF)和电压控制振荡器(VCO)3个基本部件组成[3]。鉴相器是一个相位比较装置,用来检测输入信号相位和反馈信号相位之间的相位差,通常可用乘法器和低通滤波器的串接作为模型。而环路滤波器具有低通特性,它一方面可以起到低通滤波器的特性,更重要的是它对环路参数调整起着决定性的作用。压控振荡器是一个电压-频率变换装置,在环路中作为被控振荡器,它的振荡频率应随着输入控制电压线性地变化。如图1是锁相环的基本组成原理图。

图1 锁相环的基本组成

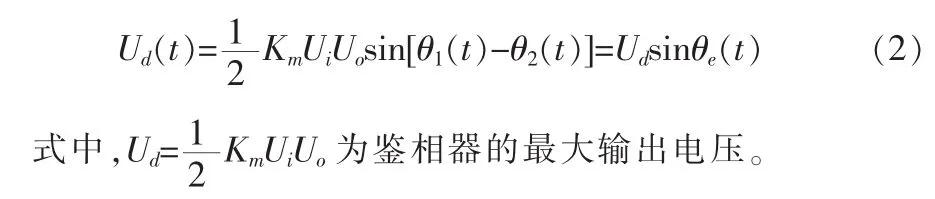

其中鉴相器是能够进行相位跟踪的关键部件,假设乘法器的相乘系数为Km(单位为1/V),输入信号ui(t)与反馈信号uo(t)相乘后的输出为:

乘法器输出结果经过低通滤波器滤除频率为2wo的高频分量之后,得到误差电压为:

这就是鉴相器的其中一种最常用的电路模型。然后由这个误差电压Ud(t)经过环路滤波器,得到控制电压uc(t),由这个控制电压加到压控振荡器上使其产生频率偏移,从而跟踪输入信号频率wi(t)。若输入wi为固定频率,在uc(t)的作用下,压控振荡器的固有瞬时角频率wv(t)向wi靠拢,一旦到达两者相等时,在一定条件下,环路就可以稳定下来,稳定之后,压控振荡器振荡频率和输入信号频率相同,且维持一定的稳态相差,这就是锁相环的捕获和跟踪过程。

1.2平方变换法的原理

平方环是直接提取载波技术中受到广泛使用的一种电路。在调制信号过程中,为了节约传输信号功率,我们大多采用抑制载波的技术。但是这种抑制载波的技术的接收信号中没有直接的载波频率分量,不能进行直接的载波同步。但是信号中显然含有载频信息,只要经过非线性变换即可产生载波的倍频分量。例如,最典型的BPSK信号[4]。

式中,m(t)为不含有直流分量的调制信号,对于BPSK来讲,m(t)=±1,wc为载波频率。显然,已调信号s(t)中不含有载频wc的频谱分量。如果我们对接收到的信号进行平方变换,则可以得到:

从式(5)中可以看出,经过平方变换后的接收信号中,包含了两倍频的载波频率分量。因此,我们可以采用普通锁相环路对两倍频的载波分量进行提取,而后通过二分频就可以得到我们所需要的相干载波信号,这种抑制载波信号提取的方法就成为平方环变换法。图2为平方环提取载波的原理框图。

图2 平方环提取载波原理图

2 基于CORDIC算法的乘法器

CORDIC算法是用于计算广义矢量旋转的一种迭代运算,是J.D.Volder于1959年提出的,主要用于三角函数、双曲函数、指数和对数的运算。该算法使得矢量的旋转和定位运算不需要三角函数表及乘法、开方、反三角函数等复杂的运算,仅需要进行加减和移位即可。文献[5-6]采用CORDIC法可实现常用函数的计算,其中包括了乘法器的实现,而文献[7]中提出了对这种乘法器的进一步改进。

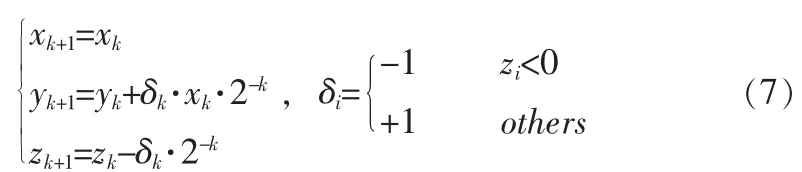

定义三参数的序列迭代集[5-6]{(xk,yk,zk)},当k≥0时,CORDIC迭代方程为:

式(6)中,εk,m的取值取决于所计算的函数。

当m=0时,可以实现乘、除运算,此时,CORDIC算法的迭代方程为:

我们进行若干次迭代后,zk+1→0,有:

因此,对于这种CORDIC算法提出的一种改进方法是[7]:当时≥2,取,并用之同时对x0,z0做归一化处理,即:,再按CORDIC算法计算x与z的乘积,之后,最终的乘积结果再进行一次反操作,即A=z×。

3 改进的平方环电路及其硬件实现

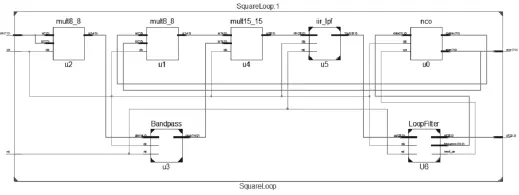

文中提出了一种基于CORDIC算法的改进的平方环设计,既避免了传统平方环设计中复杂的二分频电路,同时将电路中的多个乘法器用CORDIC算法来实现,大大降低了电路的复杂特性,同时降低了载波同步的捕获时间。改进的平方环原理图如图3所示。

图3 改进的平方环原理图

利用DDS产生的NCO数控振荡器能够输出完全正交的正余弦信号,我们利用三角函数关系式sin(2wct+2△φ)=2sin(wc+△φ)cos(wc+△φ),可以将NCO中产生的信号直接作为要提取的载波信号wc,同时将NCO中产生的正余弦信号相乘,就可以实现增益两倍的目的,然后将这个两倍频信号反馈到鉴相器中,就可以实现载波的提取,因此,用一个乘法器就可以代替复杂的二分频电路。

同时,从原理图中我们可以看出,平方变换,鉴相器和NCO产生信号的扩频各需要一个乘法器。传统的乘法器多采用改进的Booth算法产生部分积,用Wallace树形加法器完成对部分积的求和,但是Wallace树形加法器随部分积项的增多,电路互联变得较为复杂,因而采用上述CORDIC算法来实现乘法器。

在硬件实现过程中,FPGA芯片选用的是XILINX公司的SPARTAN6系列中的XC6SLX16芯片,并且联合ISE 14.7和Modelsim 10.1a进行了仿真,将仿真结果在Matlab中进行比较,验证其可行性。图4是改进的平方环顶层RTL原理图。

图4 改进的平方环RTL原理图

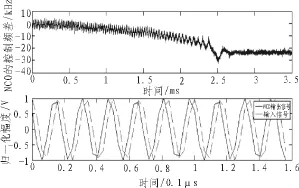

仿真输入:发送端为4 MHz的原始码速率,接收端处理后为70 MHz的载波中频信号,且中频采样位数为8位,调制方式采用DPSK调制。分别设置输入信噪比为80 dB和6 dB,得到NCO的输入频差信号和从NCO中输出的载频信号,并将载频信号和输入端的载频信号相比较,在Matlab中实现如图5、图6所示。

从图5和图6中可以看出,即使信噪比为满足锁相环的最低要求的6 dB时,本设计仍然能够正常捕获载频信号并且最终锁定,验证了本设计的可行性。从仿真图中,我们可以看出,信噪比越高,捕获时间越短,并且锁定后NCO的输入频差信号的波动值越小。同时,我们注意到NCO的输出信号和要提取的载波信号始终保持了一个稳定的相位差,这是因为在改进的平方环电路中,输入信号经过了一系列的乘法器以及滤波器处理,这些处理都有着一定的延时,延时就导致了一定的相位差,但这个延时是可以计算出来的。因此,在最终的解调过程中,将输出信号进行一定的延时处理,就可以提取到与输入信号同频同相的载波信号。

图5 信噪比为80 dB的仿真分析图

图6 信噪比为6dB的仿真分析图

4 结束语

该平方环提取载波电路避免了对锁相环中本振信号的二分频处理电路,同时将复杂的乘法器用CORDIC算法来实现,运行速度快,并且大大地节约了硬件资源。在成本不高的运行环境中,该平方环电路以其电路结构简单,成本低的优点,可以得到广泛的使用。

[1]樊昌信,曹丽娜.通信原理[M].北京:国防工业出版社,2010.

[2]吕鑫宇,姚远程,谭清怡,等.基于直接提取载波技术的平方环设计[J].现代电子技术,2010(1):189-192.

[3]杨勇.数字通信同步技术的MATLAB与FPGA实现[M].北京:电子工业出版社,2013.

[4]陈联连,孙玲.两种抑制载波双边带信号的载波提取方法比较[J].南通大学学报:自然科学版,2011,10(1):10-15.

[5]Volder JE.The CORDIC trigonometric computing technique[J].IRE Transactions on electronics Computers,1959,8(3):330-334.

[6]Walther J.A unified algorithm for elmentary functions[J].Joint Computer Conference Proceedings,1971,38(4):379-385.

[7]高顺先,梁芳,周宏安.基于CORDIC算法的乘法器的VLSI实现[J].陕西理工学院学报:自然科学版,2010,26(2):18-21.

Design of modified squaring loop based on CORDIC algorithm

JING Li-ming

(College of Computer and Information,Hohai University,Nanjing 211100,China)

Carrier recovery is a very important part of the circuit in digital communication,and the squaring loop has been widely used for its simple circuit structure.To simplify the structure of the circuit further,a modified squaring loop circuit was proposed,which eliminates the need for two devided-frequency circuit.At the same time,we improve the circuit further by using CORDIC algorithm to realize a plurality of multipliers in this paper.The algorithm can be easily realized by pipelined architecture,and can reduce the complexity characteristic of the circuit,as this algorithm uses merely shift mathematical operation and adder.At the end,we unites ISE 14.7 with Modelsim 10.1a to go with the simulation of the modified circuit.Then we get the carrier signal of input SNR 6dB and 80 dB,respectively,which turns out to be feasible.

carrier extraction;NCO;CORDIC algorithm;ISE;Modelsim

TN911.8

A

1674-6236(2016)17-0093-03

2015-09-18稿件编号:201509134

荆黎明(1993—),男,河南焦作人,硕士研究生。研究方向:探测与对抗技术。