基于FPGA的GPS接收机位同步帧同步设计与实现

2016-09-08魏可友余金培

刘 成,魏可友,余金培,梁 广

(1.中国科学院上海微系统与信息技术研究所,上海 200050;2.上海微小卫星工程中心,上海 201203)

基于FPGA的GPS接收机位同步帧同步设计与实现

刘 成1,2,魏可友1,2,余金培1,2,梁 广1,2

(1.中国科学院上海微系统与信息技术研究所,上海200050;2.上海微小卫星工程中心,上海 201203)

为了能在GPS接收端获取正确导航电文,研究了GPS接收机位同步、帧同步的基本原理和实现方式。提出一种采用FPGA来实现位同步、帧同步系统的设计方案。使用Xilinx开发软件,通过Verilog代码完成对位同步、帧同步的设计并在硬件平台上进行调试。通过Chip Scope和逻辑分析仪进行验证,结果表明该设计方案正确可靠,满足设计要求。

GPS接收机;位同步;帧同步;FPGA

随着空间技术的不断发展,星载GPS接收机已经逐渐发展成为航天器的一个重要平台载荷。它可以为航天器提供全球、全天候、实时、高精度的导航信息,并且提高航天器运行的自主性。

GPS接收[1]主要包括射频前端、捕获、跟踪、位同步、帧同步、数据解调模块。由射频前端接收GPS卫星信号,经过处理后,由捕获来获取完成伪码粗同步,跟踪模块完成载波环路、码环的跟踪锁定后进入位同步、帧同步模块获得导航电文数据,最终解调输出PVT(位置、速度和时间)信息。

文中主要研究位同步、帧同步模块的设计方法和实现过程。采用 Xilinx公司 Virtex4系列的 XC4VSX55芯片,用Verilog编程实现,通过仿真验证后下载到硬件平台上调试。测试数据采用SMJ100A信号发生器模拟GPS卫星信号,经过捕获、跟踪模块所得,通过ChipScope和逻辑分析仪最终验证了算法的正确性。

1 位同步

位同步也称为定时同步、符号同步、码元同步,它是数字通信系统特有的一种同步,并且不论是基带传输还是频带传输都需要位同步。在数字通信系统中[2],为了限制被传输的数字信号频谱,需要对数字进行滤波成型后再对载波进行调制,以实现信号的带限传输,接收端进过相干解调、采样判决后恢复出发送端的数字信号。由于信道传输延时及收发两端时钟的偏移,接收端采样无法在最佳时刻进行,使恢复出的数据与发送数据之间有误差。接收端为了得到最佳采样值恢复发送端所发出的数据,要求接收时钟与发送时钟同步,需要有同步措施来调整接收端的采样时钟,这个同步过程称为位同步。

导航信息比特的同步,是以载波和伪码的锁定状态为前提的。信息比特的同步处理就是要确定信息比特的起始位置,并获得信息比特的值。在这里需要使用相关器输出连续1 ms相关信号和1 ms码元计数值。

完成信息位同步的方法主要基于下面两个条件:

1)卫星的导航信息比特周期固定,且为码周期的整数倍。

2)相关器每1 ms输出一次累加数据信息。

导航信息位同步可以共用公式(1),使SUM_IPk值最大的k就是信息比特的位置。

其中:E{x}表示x的均值;k=0...19最佳比特位置的20个可能值;r=N20现在码周期数的模20值;d=19。

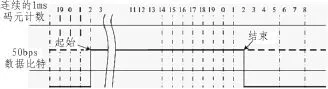

图1表示一个数据比特,从图中可以看出,当k=2时,SUM_IPk得到最大值,从而可以得到数据比特的起始位置,完成数据比特的同步。

图1 数据位同步示意图Fig.1 Bit synchronization sketch map

在接收机中的导航信息位同步方式,主要有下面几个步骤:

1)在接收机中维持20个起始位置依次相差1 ms的滑动窗口,滑动窗口的长度为20 ms;

2)接收机对每个滑动窗口内的20个相关值进行累加,找出累加值最大的滑动窗口;

3)如果在一段时间内(通常为2秒),都是同一滑动窗口的累加值最大,则可以认为该滑动窗口起始位置为信息比特起始位置,完成信息位同步。

FPGA实现:本设计采用2个计数器、2个缓存器和一个滑动累加器。通过滑动累加器计数累加20次,缓存判断累加峰值,达到峰值即可认为起点处为比特数据的起始位置。然后,以该起点位基准连续20组数据进行累加多次判断确认是否都能出现累加峰值。如果均为峰值说明完成位同步,否则重新进行判断。位同步的仿真波形如图 2所示[3-4]。

图2 位同步的仿真波形图Fig.2 Bit synchronization simulationwaveform

其中,clk:系统时钟;bitsync_flag:位同步的标识;data_out:输出的比特数据;bitsync_valid:比特数据有效脉冲。

从仿真波形图可以看出,在完成位同步判断后,标志位变为高电平。并且,输出的比特数据是重新开始下一个20周期累加值的判断后再输出,所以与标志位电平会有20 ms的延迟。测试文件设置为0、1交替输出,即仿真结果满足设计要求,实现了位同步过程。

考虑到实际接收到的GPS卫星信号可能会存在信噪比很低的情况,会影响相关器累加值发生跳变。如果仍然采用2秒时间累积逐次判断方法,会导致位同步时间加长严重影响接收机的性能。因此在低信噪比条件下,应加上阈值判断。在2 s内,累加峰值正确判断的概率大于90%(可以根据不同信噪比条件适当调整),即认为完成位同步。

图3表示下载到硬件平台上,采用信号发生器产生的实际GPS数据验证位同步,通过ChipScope软件抓取硬件内部信号进行分析。经过分析得出以下结论:每20相关器的累加值进行累加判断,累加和为正数代表比特1,累加和为负数代表比特0。每20个累加和之后才输出比特值,完成位同步的判断,结果满足设计要求。说明该设计正确有效,可以在实际的工程中进行运用。

图3 ChipScope软件调试波形图Fig.3 Chip Scope debugs waveform

2 帧同步

在数字通信过程中,发送端以一定数目的码元组成一个个“字”或“句”,即组成一个个数据帧进行传输,因此帧同步信号的频率很容易由位同步信号经分频得出,但每个帧的开头和末尾却无法直接由位同步信号获取,为此,帧同步的主要任务就是要获取每个数据帧的起始及结束位置。显然,帧同步是以位同步为前提的,也就是说需要在位同步基础上获得帧同步。

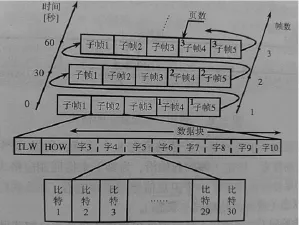

本小节主要讨论GPS导航电文格式的帧同步技术。卫星导航电文以帧与子帧的结构形式编排成数据流D(t)。如图3所示,每颗卫星一帧接着一帧地发送导航电文,而在发送每帧电文时,卫星又以一子帧接着一子帧的形式进行[5-8]。

图4 Frame synchronization simulationwaveformFig.4 GPS navigation message

每帧导航电文长1 500比特,计30 s,依次由5个子帧组成。每个子帧长为300比特,计6 s,依次由10个字组成。每个字长30比特,其最高位先被发送,而每一子帧中的每一字又均以6比特的奇偶校验码结束。其中,每一比特长20 ms,其间C/A码重复20个周期。

系统获得帧同步的依据有以下几点:

1)检测到preamble

2)TLM的校验成功

3)HOW的最后两个校验位为0

4)HOW的校验成功

5)子帧标号合理(1~5)。

6)子帧校验和解码成功。

当以上6个条件全部满足时,才认为获得帧同步。

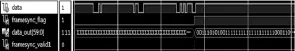

FPGA实现:根据系统获得帧同步的6个判断依据可以设计一个状态机,由每一个状态逐个进行判断,从而最终找出帧头。根据所设计的状态机,编写代码后进行仿真,波形图如图5所示[9-11]。

图5 帧同步仿真波形图Fig.5 Frame synchronization simulationwaveform

Data:输入的比特数据;frameync_flag:帧同步标志;data_out:输出帧同步后的导航数据;framesync_valid1:导航数据有效高脉冲。在完成帧同步的判断,同步标志位置高同时从帧头开始输出导航数据。

GPS接收机在完成环路跟踪后,把累加值送入位同步模块,完成位同步后进入帧同步模块。因此,帧同步必须以位同步为前提,把两个模块进行拼接后进行联合调试,如图6所示。

图6 比特/帧同步联合调试Fig.6 Bit and frame synchronization joint debug

其中,bit_flag:位同步标志;Bit:位同步后输出比特;frame_flag:帧同步标志;data_out:完成帧同步后的导航数据。

可以看出,首先完成位同步,然后完成帧同步,同步后数据输出的低8位为10001011,正好是GPS导航数据的前导码,子帧标号为001即第一子帧,说明完成了对位同步和帧同步模块的联合测试验证。

3 结 论

详细介绍了位同步、帧同步的基本概念、实现方法、仿真波形图及硬件调试结果。经过分析FPGA仿真和硬件调试结果,证明设计满足设计要求。测试数据采用信号发生器模拟的GPS卫星信号更加真实客观,说明设计方法适合运用在实际的GPS接收机中。

[1]谢钢.GPS原理与接收机设计[M].北京:电子工业出版社,2009.

[2]杜勇.数字通信同步技术的MATLAB与FPGA实现[M].北京:电子工业出版社,2015.

[3]田耘,徐文波,张延伟.无线通信FPGA设计[M].北京:电子工业出版社,2007.

[4]段吉海,黄志伟.基于CPLD/FPGA数字通信系统建模与设计[M].北京:电子工业出版社,2004.

[5]范寒柏,谷力伟,赵冉.帧同步系统的FPGA设计与实现[J].电子设计工程,2009(8):17-8

[6]管立新,沈保锁,柏劲松.帧同步系统的FPGA设计[J].微计算机信息,2006(9):177-178.

[7]吴玉成,许太火,王黎明.帧同步电路设计[J].现代电子技术,2003(4):69-71.

[8]陈惠珍,包天珍.一种基于FPGA的帧同步提取方法的研究[J].电子技术应用,2003(10):70-72.

[9]王梦源,闫峥,东昕.一种精确帧同步算法及FPGA实现[J].电子设计工程,2015(2):151-154,159.

[10]朱娟娟,姚远程,秦明伟.高速数传中定时同步设计与FPGA实现[J].电子科技,2014(3):117-119,132.

[11]石峰,吴笛,祁建华.基于FPGA的有源电力滤波器高速数据采集系统设计[J].陕西电力,2008(10):36-39.

Design and implement of GPS receiver synchronization module based on FPGA

LIU Cheng1,2,WEI Ke-you1,2,YU Jin-pei1,2,LIANG Guang1,2

(1.Shanghai Institute of Micro-system and Information Technology Chinese Academy of Science,Shanghai 200050,China;2.Shanghai Engineering Center for Micro-satellite,Shanghai 201203,China)

For obtain correct navigation message of the GPS receiver,the basic theory and implementation of GPS receiver was studied.Abit synchronization and frame synchronization is realized by using FPGA.Usingdevelopment software of Xilinx,by Verilog code to complete the bit synchronization and frame synchronization design and debug on the hardware platform. Validated by Chip Scope and logic analyzer,the results show that the design scheme is correct and reliable,meet the design requirement.

GPS receiver;bit synchronization;frame synchronization;FPGA

TN915

A

1674-6236(2016)01-0156-03

2015-06-02稿件编号:201506035

国家自然科学基金(61401278);国防科技创新基金(CXJJ-15S086)

刘 成(1989—),男,四川泸州人,硕士研究生。研究方向:无源定位算法。