高隔离度和ns级响应时间的主动式射频前端限幅设计方法

2016-09-02杜平

杜平

海军装备部驻保定地区航空军事代表室,河北保定071000

高隔离度和ns级响应时间的主动式射频前端限幅设计方法

杜平

海军装备部驻保定地区航空军事代表室,河北保定071000

用于防止射频前端受到物理损伤的限幅器,其限幅输出电平难以得到有效抑制,并且容易导致敏感的低噪声放大器进入深度饱和状态,影响接收通道的正常工作。因此,提出一种具有高隔离度和ns级响应时间的主动式射频前端限幅模块设计关键技术。经实验验证,所设计的模块通过集成检波器、高速比较器和多级PIN二极管,能够较大程度的降低限幅模块的饱和阻抗,提高强射频信号注入时的隔离度,从而降低泄露到后级敏感模块的功率等级,防止接收机进入深度饱和状态。

射频前端;限幅器;PIN二极管

0 引 言

电磁脉冲辐射导致的射频接收前端饱和是射频系统面临的主要电磁脉冲危害。针对典型射频系统的实验表明,对于低噪声放大器,在幅度为mW级、脉宽为ns级的脉冲作用下,会导致长达数百微秒的饱和时间。饱和期间,射频通道对于有用接收信号会丧失放大功能,导致接收机无法正常对信号进行传输和处理,如果电磁脉冲重复频率达数千赫兹以上,接收机饱和导致的危害将更加严重。目前,国内外电磁脉冲辐射危害效应的研究主要聚焦在高功率毁伤效应上,对饱和问题的研究尚处于起步阶段[1-3]。为解决低噪声放大器的饱和问题,侦察接收系统通常在低噪声放大器前端采用限幅模块,但限幅模块的限幅效果非常有限,限幅输出的信号功率通常在5~7 dBm,仍然接近低噪声放大器饱和信号功率,无法有效解决低噪声放大器在电磁脉冲辐射作用下的深度饱和问题。

本文将主要针对电磁脉冲辐射导致的射频前端敏感低噪声放大器深度饱和问题,提出一种基于集成检波、高速比较和多级PIN二极管的主动式射频前端限幅设计方法,以显著降低限幅模块饱和阻抗,从而降低泄露到后级敏感模块的功率等级。

1 防护限幅模块设计方法

1.1总体设计思路

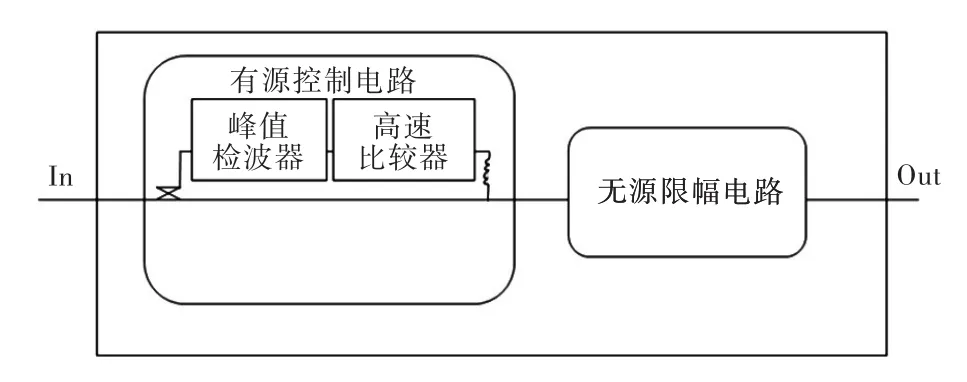

限幅器包括有源控制电路和无源限幅电路2个模块,如图1所示。其中,有源控制电路主要包括峰值检波器和高速比较器,其功能是对输入信号进行检波、比较,当信号幅度超过阈值时,输出脉冲偏置信号,使无源限幅电路进入低阻状态,峰值检波器和高速比较器的响应时间决定了有源偏置电路在检测到电磁脉冲信号后的动作时间;在无源限幅电路加工工艺方面,采用PIN二极管的裸芯片替代传统的SOT塑封二极管,以金丝球焊工艺与微带线连接,提高大信号注入时的隔离度。

图1 防护模块的基本构成框图Fig.1 The diagram of protection module

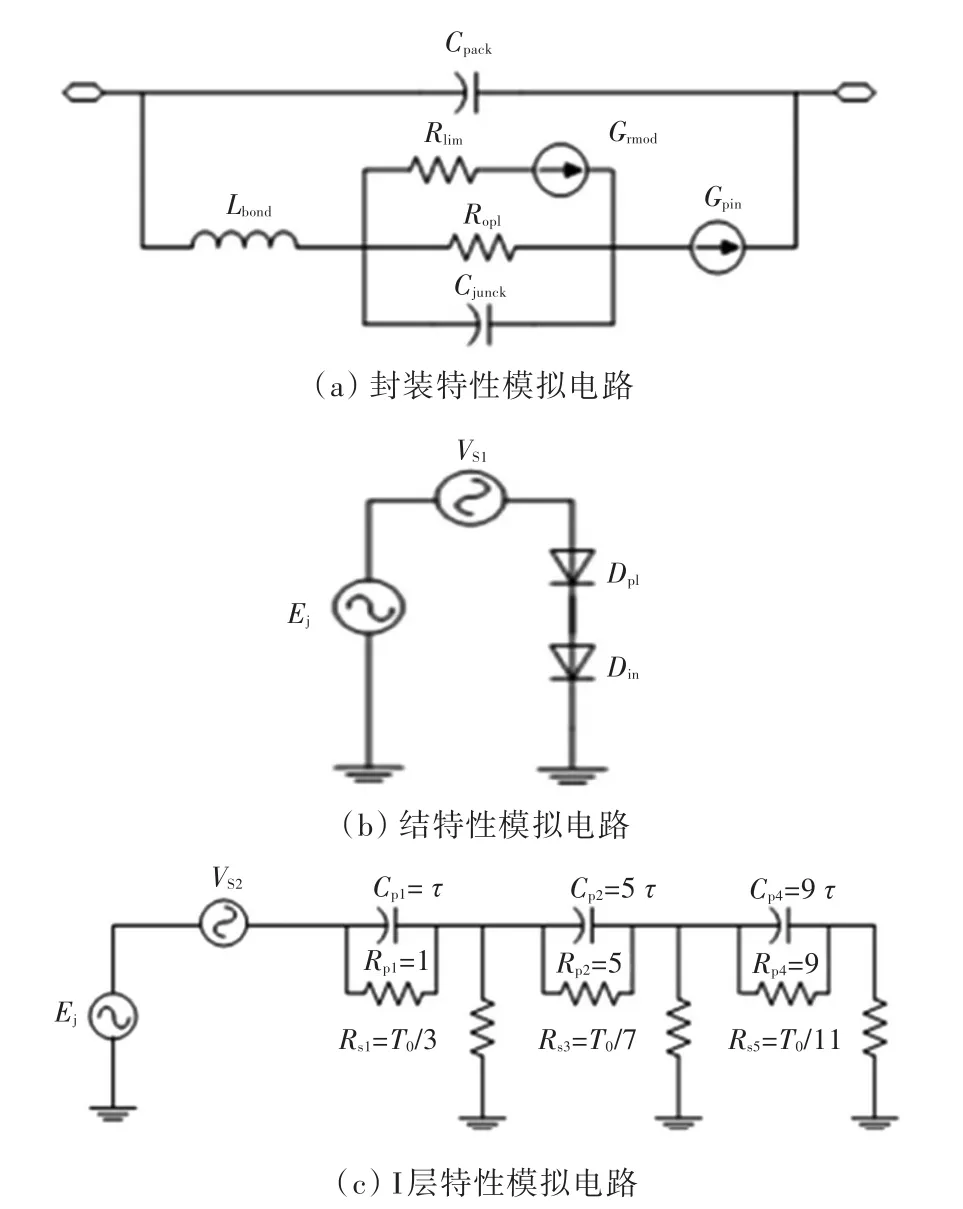

限幅模块设计方法的核心在于PIN二极管的建模。由于常规PN结二极管时域模型不能模拟PIN限幅二极管在电磁脉冲作用下的瞬态响应特性,因此,为分析PIN二极管的微波性能,建立了基于“封装—PN结—I层”一体化模拟电路的射频前端限幅模块仿真模型(图2)。在该模型的基础上,构建了射频前端限幅模块的仿真模型,用以较准确地预测限幅模块的电磁脉冲响应。所建立的PIN二极管仿真模型包括3个部分:1)封装特性模拟电路,用于模拟二极管引线电感和封装电容的作用;2)结特性模拟电路,用于模拟PI结和IN结的特性;3)I层特性模拟电路,用于模拟脉冲电流注入时在I层发生的电荷存储效应。

图2 基于“封装—PN结—I层”的等效电路模型Fig.2 The equivalent circuit model based on Package-PN junction-I layer

PIN二极管建模的核心在于,用等效电路表达I层的电荷存储模型计算公式。具体实现方法是:从PIN二极管I层双极载流子扩散方程出发,通过拉普拉斯变换和有理分式逼近,建立I层等效子电路模型。PIN二极管I层特性模拟电路建立流程如图3所示。

图3 PIN二极管I层特性模拟电路建立流程Fig.3 The modeling flow of analog circuits for the I layer characteristics of PIN diode

1.2有源控制电路设计

有源控制电路主要包括峰值检波器和高速比较器。这2个有源器件的响应时间决定了有源控制电路在检测到电磁脉冲信号后的动作时间。

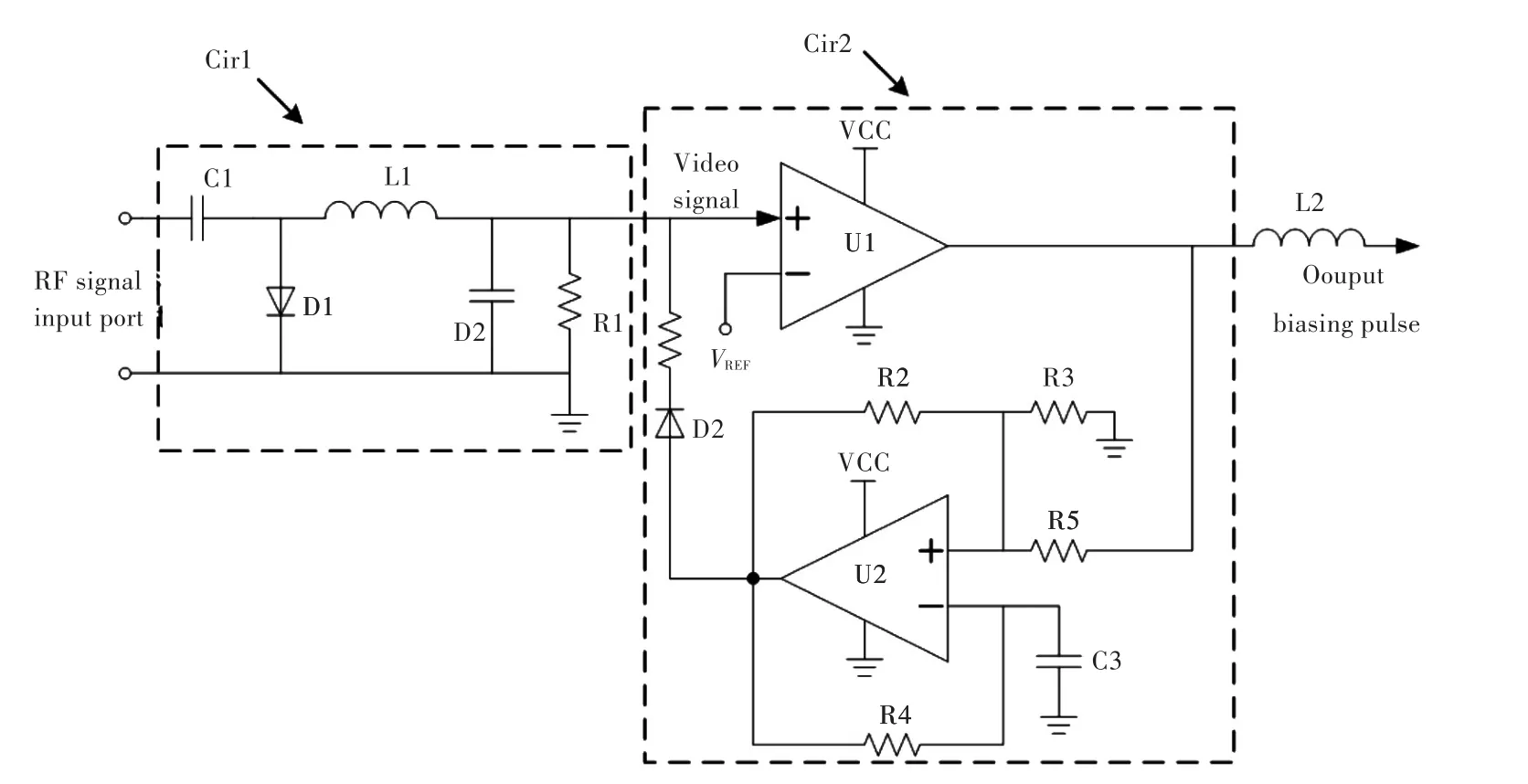

控制模块的内部电路结构如图4所示。图中Cir1所示是峰值检波电路;Cir2所示是比较电路。在Cir1内,包括了肖特基二极管D1、滤波电容C1和C2、扼流电感L1以及匹配电阻R1,其作用是提取输入射频信号的包络,形成视频信号,并提供给比较电路;在Cir2内,包括了具有ns级传播延时和mV级响应阈值的高速比较器U1和U2,定时元件R4和C3以及相关外围电路元件。比较电路Cir2具有捕捉ns级快速瞬变信号的功能。如果控制模块采用单个检波比较器时所具备的驱动能力不能满足要求,则可以采用多个检波比较器,以同步驱动的方式为PIN二极管提供偏置电流。图5为有源控制电路原理样件的照片。

图4 有源控制电路的内部结构Fig.4 Internal structure of the active control circuit

图5 有源控制电路的原理样件Fig.5 Principium sample of the active control circuit

1.3无源限幅电路设计

在无源限幅模块加工工艺方面,没有采取传统的SOT塑封二极管作为限幅元件,而是采用PIN二极管的裸芯片,以金丝球焊工艺与微带线连接,可大幅降低引线电感,从而降低高功率信号注入时的限幅阻抗,提高隔离度。图6(a)[4]是常见SOT-23塑封PIN二极管的结构,其中键合线的电感约1 nH,2个外部引脚的电感各0.5 nH,总电感约2 nH。当频率为1 GHz时,二极管串联电感的感抗即达到了12.6 Ω,远大于PIN二极管本身的导通电阻(1~2 Ω),大大削弱了限幅效果。采用图6(b)[5]结构安装的PIN二极管,由阳极引出2根键合线串联于电路板上的微带线之间,导致这两根线上流过的电流方向相反。由于它们贴合得非常近(距离小于2 mm),因此电流流过时产生的磁场可以在很大程度上互相抵消,总体上的效果相当于串联电感几乎为0,有助于降低PIN二极管大信号等效阻抗,提高限幅效果。

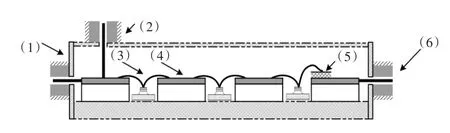

为进一步提高限幅模块的功率承受能力和隔离度,限幅电路采用三级限幅的方法,如图7所示。其中:(1)为RF信号输入端;(2)为控制信号输入端;(3)为二极管的键合线;(4)为微带电路的中心导线;(5)为输出端隔直电容;(6)为RF信号输出端。

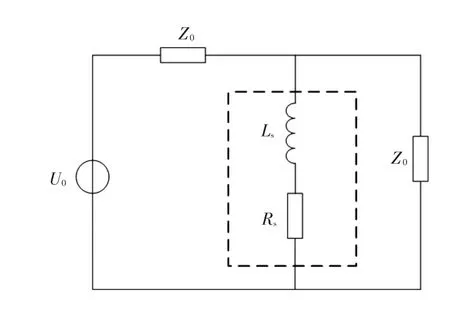

3个I层厚度2 μm的PIN二极管并联在传输线的芯线和地线之间,用等效电路表示(图8)。图中:Z0表示射频系统阻抗(50 Ω);LS表示3个二极管并联后的等效串联电感;RS表示并联后的等效导通电阻。

图6 塑封PIN二极管与金丝焊PIN二极管的对比Fig.6 Comparison of the plastic-sealed PIN diode with the gold wire bonding PIN diode

图7 三级PIN二极管的低功率限幅模块结构示意图Fig.7 Diagram of the lower power PIN diode internal architecture

图8 射频前端限幅器等效电路Fig.8 Equivalent circuit of RF front-end

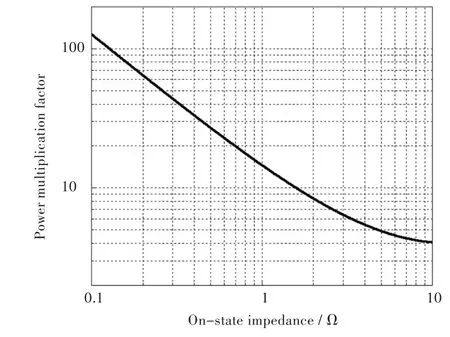

通过计算输入功率PL和限幅耗散功率PD,可以得到

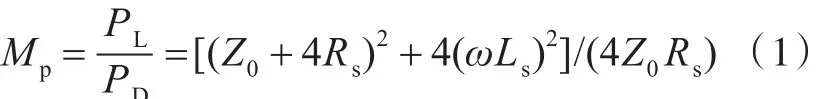

式中,Mp为输入功率PL与二极管中的损耗功率PD之比,称为功率传递倍乘因子,其随等效导通电阻的变化曲线如图9所示。在敏感系统工作频率较低时,ωLs<<Z0,式(1)可以简化为

图9 限幅器功率倍乘因子Mp随等效导通电阻RS的变化曲线Fig.9 Variation of limiter's power multiplication factor with respect to equivalent on-state impedance

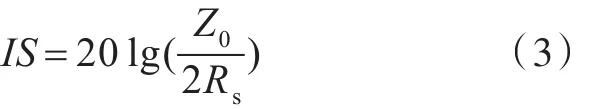

理想情况下,等效导通电阻越小,功率传递倍乘因子越大,二极管所能承受的入射功率也越大,因此,采用三管并联方式,使大信号阻抗降低为单管的1/3,同时,根据隔离度计算公式,也可实现隔离度增加9.5 dB。

2 实验验证

2.1有源控制电路的测试结果

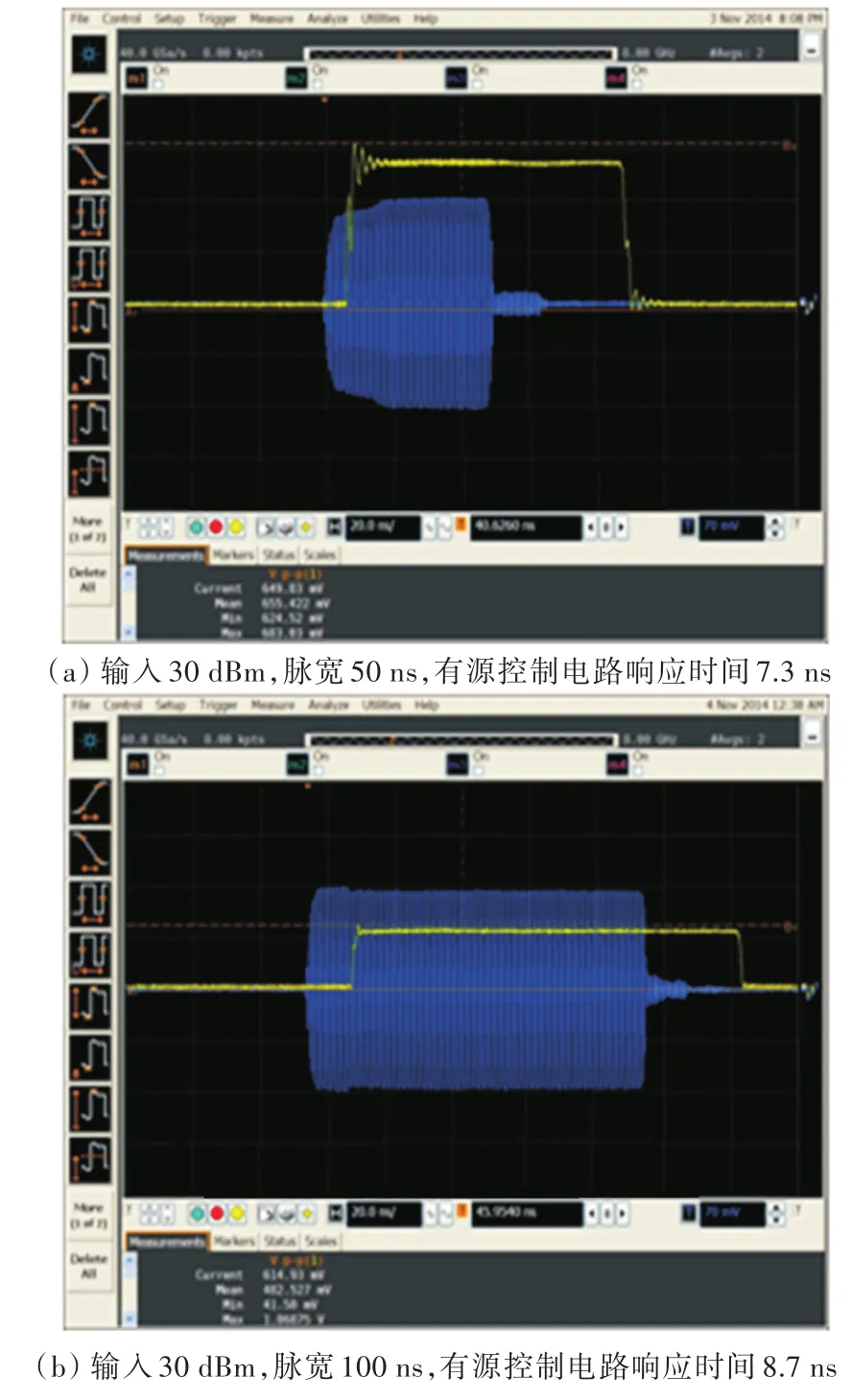

利用信号源产生中心频率1 GHz的脉冲信号,将其注入到有源控制模块的参考信号输入端,利用示波器监测模块输出端的有源偏置脉冲,而射频信号输入端接50 Ω匹配阻抗,实验配置如图10所示。实验表明,所设计的有源偏置电路启动电平可低至-10 dBm,动态范围大于35 dB,启动时间小于10 ns(典型值7~9 ns),如图11所示。

图10 有源控制电路的测试配置Fig.10 Test configuration of the active control circuit

图11 有源控制电路在不同输入信号功率、不同脉宽时的启动时间测试图Fig.11 Test diagram of start up time for active bias circuit with different input power and pulse width

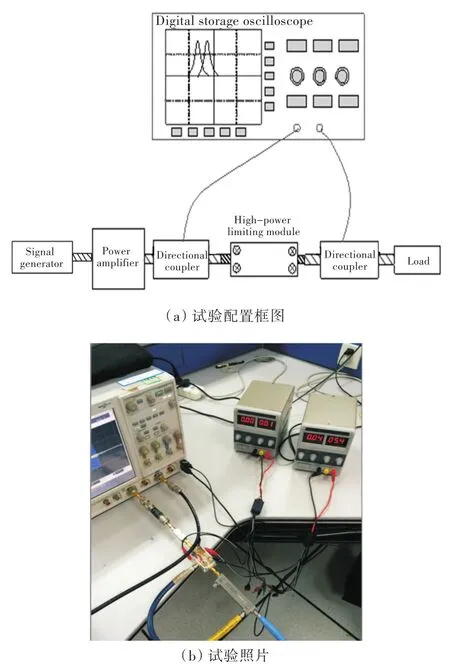

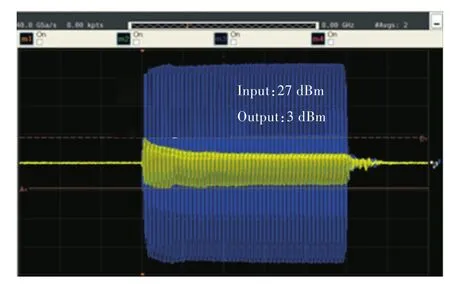

2.2无源限幅电路的测试结果

利用图12所示的实验配置,测量限幅模块的时域响应。实验结果表明,相对于常规塑封二极管,基于裸芯片PIN二极管的无源限幅电路具有较低的限幅输出电平,如图13和图14所示结果的对比。对于相同的输入功率27 dBm,裸芯片PIN二极管限幅器的输出电平为3 dBm,比塑封PIN二极管限幅器所输出的9 dBm功率低6 dB。

2.3限幅器的测试结果

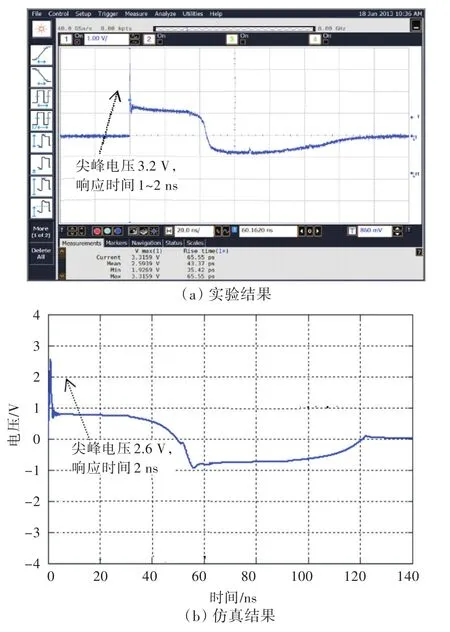

将有源控制电路和无源限幅电路组合之后构成限幅器,利用图12所示的实验配置,测量限幅器的时域响应。

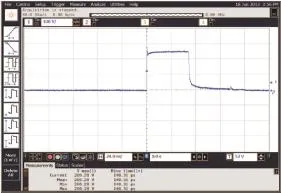

传输线是微带结构,建模特征参数包括电长度和特征阻抗。电长度由实际物理尺寸得到,分别为:TL1=TL2=0.01λ,TL3=0.03λ,TL4=0.05λ,TL5=0.09λ,其中λ=30 cm。根据微带线阻抗计算公式,得到特征阻抗为51 Ω。限幅模块中,第1级限幅元件为I层厚度7 μm的双向PIN二极管,第2级为厚度5 μm的PIN二极管,第3级为厚度2 μm的PIN二极管。每个二极管的键合线电感均为1.5 nH。结合传输线模型,得到限幅模块的电磁脉冲响应模型。设定不同的注入电压源波形,通过仿真,可以观察到限幅模块的输出波形。如图15~图17所示,基于所开发的限幅模块时域建模方法,能够较准确地预测电磁脉冲注入时限幅模块的启动时间、泄露电平,仿真结果与实测数据误差少于3 dB。

图12 高功率限幅模块测试的实验配置Fig.12 Experiment configuration of high power limiter module

图13 基于塑封PIN二极管限幅器的输入—输出脉冲波形Fig.13 The input-output pulse waveform for plastic sealed PIN diode limiter

图14 基于裸芯片PIN二极管限幅器的输入—输出脉冲波形Fig.14 The input-output pulse waveform for naked PIN diode limiter

实验结果表明,输入微波脉冲幅度为40 dBm时,限幅输出电平小于0 dBm,远低于现有常规防护模块输出电平5~7 dBm的平均值。限幅模块在偏置状态下的阻抗约为0.2 Ω,隔离度达40 dB。注入电压50 V前沿0.3 ns

图15 注入到UHF频段多级限幅模块的方波脉冲波形Fig.15 The waveform of square pulse injected into the multi-level clipping module in UHF frequency range

图16 方波脉冲注入时UHF频段多级限幅模块的时域响应波形Fig.16 The waveform in the time domain while the square pulse injecting into the multi-level clipping module in UHF frequency range

图17 防护模块的时域测试结果Fig.17 Time domain measurement results for protection module

3 结 语

当射频、微波敏感电子信息系统暴露于电磁脉冲辐射场时,接收通道会受到电磁脉冲能量冲击,需要重点关注限幅模块的性能,其在电磁脉冲注入时的时域响应特性与接收通道的受干扰程度和效应密不可分。本文通过针对射频通道电磁脉冲的限幅设计研究,探索了防止接收机低噪声放大器饱和的主动式限幅方法,通过原理样机验证表明,控制电路响应时间可控制在7~9 ns,隔离度达40 dB。

后期将根据需要,重点增加滤波、延时、有源开关等功能模块,形成新型防护模块的电路设计方案,并通过多参数迭代仿真,进一步实现优化设计。

[1]WHALEN J J.The RF pulse susceptibility of UHF transistors[J].IEEE Transactions on Electromagnetic Compatibility,1975,EMC-17(4):220-225.

[2] KUBOYAMA S,SUZUKI T,HIRAO T,et al.Mechanism for single-event burnout of bipolar transistors[J]. IEEE Transactions on Nuclear Science,2000,47(6):2634-2639.

[3] 李平,刘国治,黄文华,等.半导体器件HPM损伤脉宽效应机理分析[J].强激光与粒子束,2001,13 (3):353-356.

LI Ping,LIU Guozhi,HUANG Wenhua,et al.The mechanism of HPM pulse-duration damage effect on semiconductor component[J].High Power Laser and Particle Beams,2001,13(3):353-356.

[4]Skyworks Solutions Inc.PIN limiter diodes in receiver protectors[M].U.S.A:Skyworks Solutions Inc.,2006.

[5]Agilent Technologies.Low cost surface mount power limiters[M].U.S.A:Agilent Technologies,2010.

A design method for high isolation and nanosecond response RF front-end active limiter module

DU Ping

Baoding Military Representative Department,Naval Armament Department of PLAN,Baoding 071000,China

The output voltage level of the limiter for protecting the RF front-end from physical damage is difficult to reduce,and often leads the low noise amplifier to enter into deep saturation,disturbing the normal function of the receiving channel.To solve this,we introduce a high isolation and nanosecond response RF front-end active limiter module with key technology of parameter design and measurement.The proposed limiter module is made up of an integrated detector,high-speed comparator and multi-stage PIN diode.The saturation impedance of the limiter module is degraded on a large scale and the isolation is increased remarkably.In this way,the leakage power level to the later sensitive module is reduced and the receiver is prevented from entering deep saturation.

RF front-end;limiter;PIN diode

U674.7+03.3

A

10.3969/j.issn.1673-3185.2016.04.019

2016-04-07网络出版时间:2016-7-29 9:45

杜平(通信作者),男,1974年生,工程师。研究方向:核生化、电磁防护