基于四值脉冲参数模型的单粒子瞬态传播机理与软错误率分析方法

2016-08-30李天文杨海钢中国科学院电子学研究所北京100190中国科学院大学北京100049

李 悦 蔡 刚 李天文 杨海钢*(中国科学院电子学研究所北京100190)(中国科学院大学北京100049)

基于四值脉冲参数模型的单粒子瞬态传播机理与软错误率分析方法

李悦①②蔡刚①李天文①杨海钢*①①

①(中国科学院电子学研究所北京100190)

②(中国科学院大学北京100049)

随着工艺尺寸的不断缩小,由单粒子瞬态(Single Event Transient,SET)效应引起的软错误已经成为影响宇航用深亚微米VLSI电路可靠性的主要威胁,而SET脉冲的产生和传播也成为电路软错误研究的热点问题。通过研究SET脉冲在逻辑链路中的传播发现:脉冲上升时间和下降时间的差异能够引起输出脉冲宽度的展宽或衰减;脉冲的宽度和幅度可决定其是否会被门的电气效应所屏蔽。该文提出一种四值脉冲参数模型可准确模拟SET脉冲形状,并采用结合查找表和经验公式的方法来模拟SET脉冲在电路中的传播过程。该文提出的四值脉冲参数模型可模拟SET脉冲在传播过程中的展宽和衰减效应,与单参数脉冲模型相比计算精度提高了2.4%。该文应用基于图的故障传播概率算法模拟SET脉冲传播过程中的逻辑屏蔽,可快速计算电路的软错误率。对ISCAS’89及ISCAS’85电路进行分析的实验结果表明:该方法与HSPICE仿真方法的平均偏差为4.12%,计算速度提升10000倍。该文方法可对大规模集成电路的软错误率进行快速分析。

超大规模集成电路;软错误率;单粒子瞬态;四值脉冲参数;故障传播概率

基于仿真的故障注入方法常被用于精确分析SET脉冲的传播[7,8]。然而此法需要进行大量的迭代仿真,非常耗时[9,10]。为了克服基于仿真方法耗时长的问题,学术界提出了基于分析的方法来加速模拟SET的传播过程。伊利诺伊大学的SERA[11]提出基于概率理论、电路仿真、图论和故障仿真等方法阶段性的模拟组合逻辑中的3种屏蔽效应。此法精度较高,但其采用的故障仿真在分析大规模电路时仍然较慢。宾夕法尼亚大学开发的工具SEAT-LA[12]通过仿真工具获得逻辑通路中每一个逻辑门的逻辑状态,并应用查找表及数学公式计算SET脉冲在逻辑通路中的传播。实验结果表明该工具运行速度依然较慢。密歇根大学采用的基于威布尔函数的参数化描述符方法[13]只适合计算当脉冲幅度小于电源电压的情况,且当其采用大量的测试向量时的运行时间依然很高。卡内基-梅隆大学开发的MARS-C[14]和MARS-S[15]工具采用基于决策图的分析技术对3种屏蔽效应进行建模分析,但是基于决策图的分析技术存在内存爆炸的先天性缺陷,不适合对大规模集成电路进行可靠性分析。基于故障传播概率的方法[16]主要应用图论算法建立从逻辑门到可达输出端的逻辑通路,并应用故障传播规则计算沿逻辑路径的故障传播概率。此方法的模拟速度较高,但是其在进行SET脉冲传播分析时采用逻辑门的线性延时模型,降低了模拟的精度。最新的SET脉冲传播研究发现:SET脉冲在组合逻辑电路中传播时存在脉冲展宽及衰减效应,且其受门级晶体管设计、传输路径、输入向量及脉冲极性等多个因素的影响,使得对SET脉冲的建模提出了新的挑战[17,18]。

本文提出一种四值脉冲参数模型用于准确描述SET脉冲形状,并采用结合查找表与经验公式的方式来模拟SET脉冲的传播情况。通过将SET脉冲的四值脉冲参数并入到故障传播概率参数,本文提出的基于图论的静态分析算法可同时模拟SET脉冲传播过程中的3种屏蔽效应。本文方法克服了基于仿真的故障注入方法评估速度慢的缺陷,提高了软错误率的评估速度。同时,本文提出的单粒子瞬态四值脉冲参数模型和考虑扇出重汇聚的图论搜索算法提高了电路软错误率的评估精度。本文方法可以在集成电路的设计阶段对电路的失效率进行有效评估,从而为电路的可靠性设计提供定量分析工具,提高可靠性设计的有效性。

2 单粒子瞬态脉冲的产生与传播

空间粒子与器件发生碰撞的概率依赖于粒子能量、粒子流量、器件敏感面积及和工艺相关的参数;粒子撞击器件后,在电路逻辑门输出端产生的SET脉冲形状依赖于淀积的电荷总量、逻辑门类型及尺寸、逻辑门的输入状态以及逻辑门输出端电容;而SET脉冲在逻辑电路中传播又会受到如下3种屏蔽效应的影响。

(1)逻辑屏蔽:不存在一条从故障点到锁存器或原始输出端的敏化通路,SET脉冲被逻辑屏蔽掉。

(2)电气屏蔽:SET脉冲经过逻辑门传输之后,其宽度和幅度可能会受到逻辑门的电气效应而被削弱。

(3)锁存窗口屏蔽:传播到锁存器输入端的SET脉冲不满足锁存器的采样时序要求而不被锁存。

2.1基于四值脉冲参数的单粒子瞬态脉冲产生模型

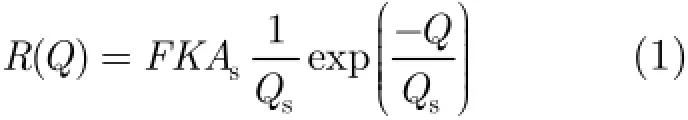

空间粒子与器件发生碰撞的概率可通过辐照实验或使用TCAD工具等方法获得,然而这些方法费用昂贵、工程复杂。因此,本文根据文献[11]提出的解析公式来模拟粒子撞击器件的概率,如式(1)所示。

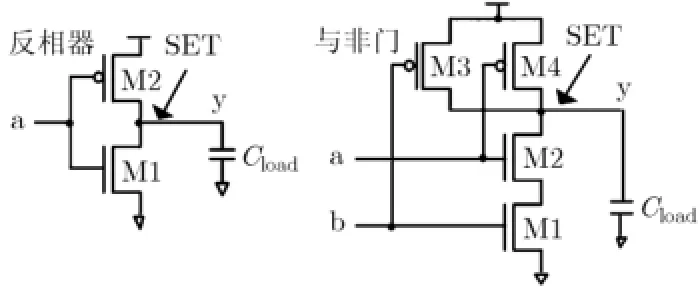

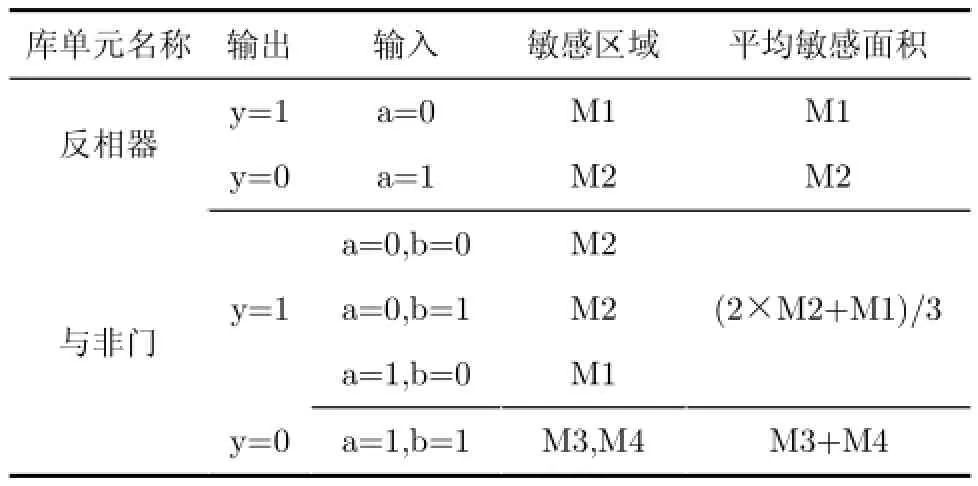

其中,R(Q)表示粒子与器件发生碰撞并淀积电荷量为Q的概率,F为海平面的中子流量,K是一个和工艺相关的适配参数,As是电路逻辑门的敏感面积,Qs是器件电荷收集斜率。文献[11,19]中均假设As等于逻辑门的总漏区面积,这种归纳方式是不准确的,因为As会随输入激励的不同而变化。为了精确模拟逻辑门失效概率,本文分两种情况来计算逻辑门失效概率:(1)逻辑门输出为0时发生0→1→0跳变;(2)逻辑门输出为1时发生1→0→1跳变。图1展示了两个基础库单元的电路结构。表1为根据库单元输出端脉冲极性计算库单元敏感面积。

图1 基础库单元的电路结构

表1 库单元敏感面积的计算

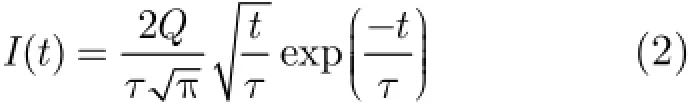

空间粒子撞击器件后,其引起的通道中的电流脉冲通常采用单指数电流源进行描述[13,11],如式(2)所示。

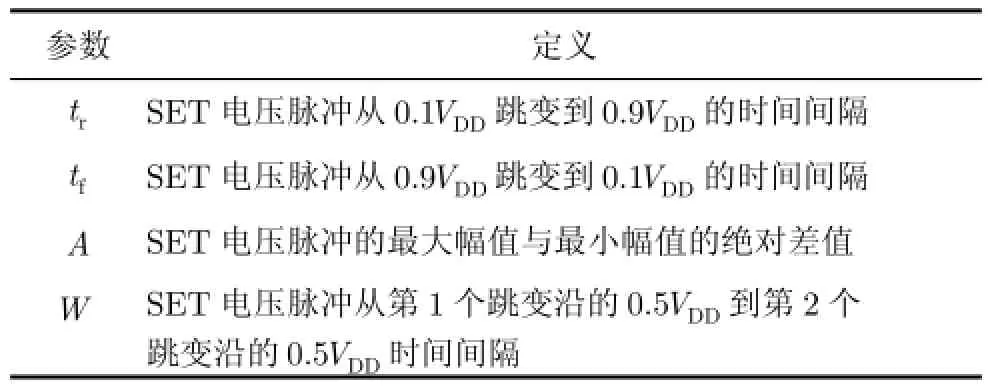

其中,т是一个和工艺相关的脉冲形状参数。不同于前人提出的单参数脉冲模型[20],本文提出一种基于四值脉冲参数的模型用于描述产生的SET电压脉冲形状。表2为四值脉冲参数的定义。

逻辑门输出端产生的SET电压脉冲形状不仅依赖于淀积的电荷总量、逻辑门类型及尺寸、逻辑门输出端电容,还和逻辑门的输入状态相关。和敏感面积的计算方式相同,本文分两种情况来计算产生的电压脉冲形状参数:(1)逻辑门输出为0时发生0→1→0跳变;(2)逻辑门输出为1时发生1→0→1跳变。表3展示了在注入电荷量Q=100 fC,负载电容Cload=1 fF的情况下,计算的与非门输出电压脉冲形状参数。

表2 四值脉冲参数定义

表3 SET电压脉冲形状参数的计算

2.2单粒子瞬态脉冲传播模型

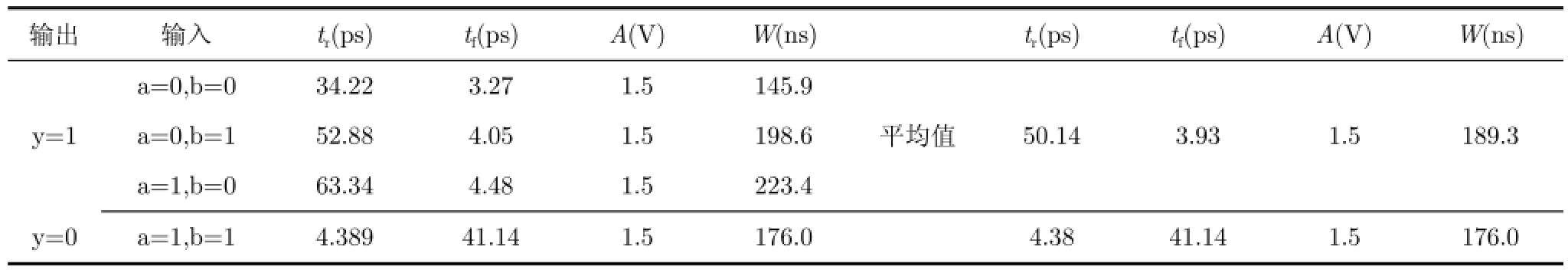

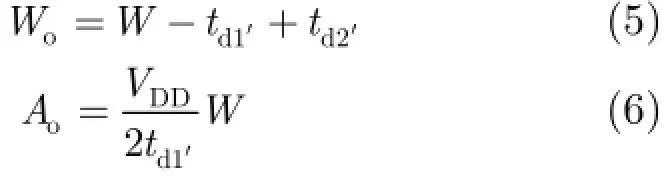

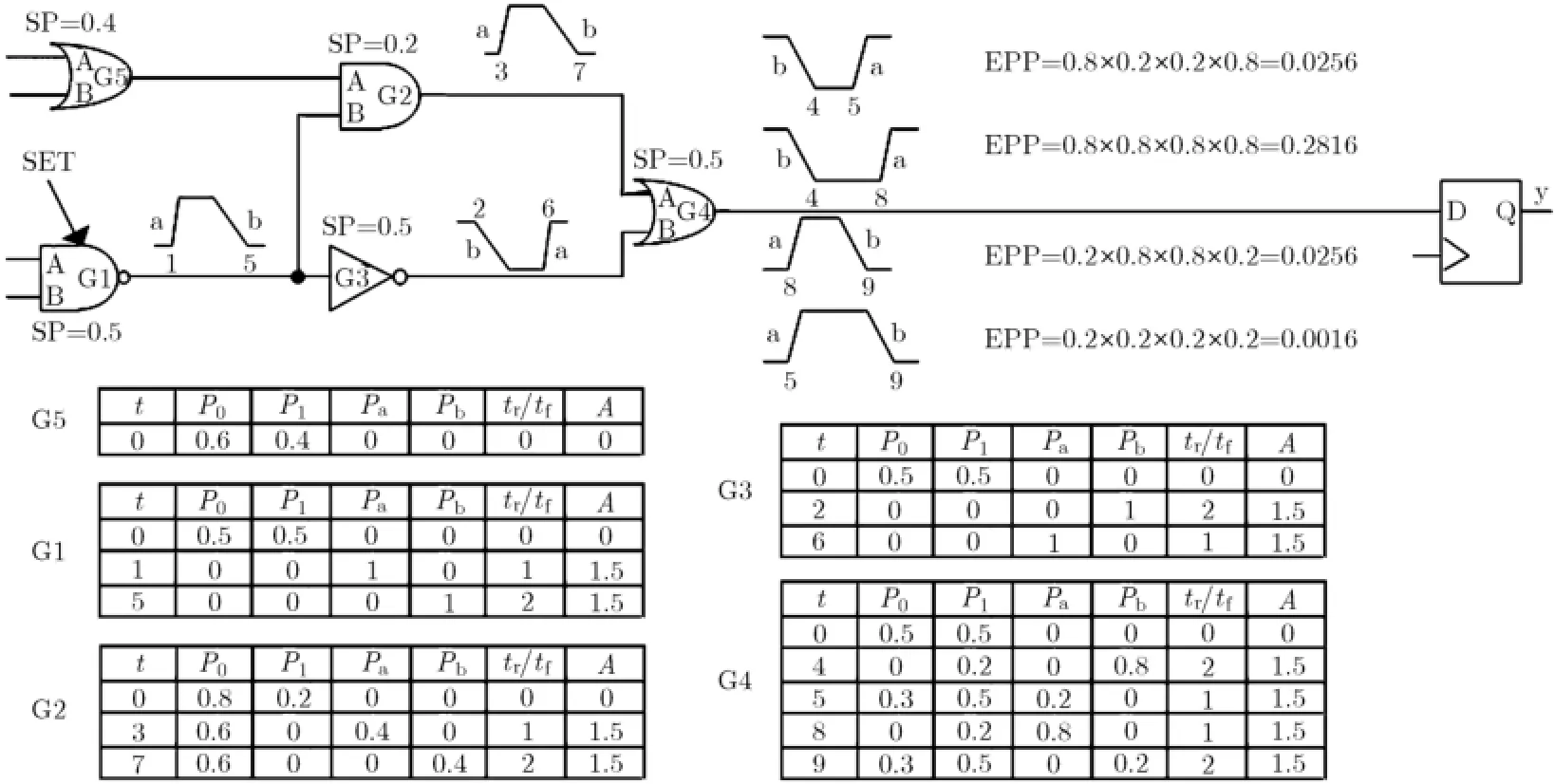

2.2.1逻辑屏蔽当从故障点到输出端仅有一条逻辑通路时,SET脉冲在此单通路中传播时仅依赖于通路中的门类型及通路中无故障输入引脚的信号概率(信号线上出现逻辑状态为1的概率)。然而,当SET脉冲在多条通路中传播并最终汇聚到同一逻辑门的不同输入引脚(重汇聚),还需考虑到达重汇聚门输入引脚的SET脉冲的时间和极性。为了有效处理SET故障脉冲在传播时的重汇聚,本文为电路中的信号定义了4个逻辑状态:0/1状态:信号线上没有故障且信号值为0/1;a/b状态:信号线上有故障且其故障极性和原始故障点处故障极性一致/相反。同时,为上述4个逻辑状态定义了对应的概率参数:信号线上的信号值为0/1的概率;信号线上出现和原始故障极性一致/相反故障的概率。因此,电路中每一个信号的状态可用向量(P0,P1,Pa,Pb)来表示。本文应用基于故障传播概率(Error Propagation Probability,EPP)的方法快速分析SET脉冲在电路中的传播概率。表4列出了本文为每个库单元定义的EPP计算规则。当选定电路中某个逻辑门为故障点,首先应用图论算法建立从该逻辑门到可达输出端的逻辑通路,然后根据通路上无故障输入引脚的信号概率和定义的库单元故障传播概率计算规则便可静态计算沿逻辑通路的传播概率。

2.2.2电气屏蔽SET脉冲在逻辑通路中传播时,其脉冲幅度、宽度会受到逻辑门的电气效应影响而被削弱甚至被屏蔽。逻辑门输出端的SET脉冲形状不仅依赖于逻辑门输入端SET脉冲形状,而且还与脉冲极性、脉冲所在的管脚位置、逻辑门类型及逻辑门负载电容相关。基于SET脉冲宽度的单参数电气屏蔽模型[20]具有简单且易于移植的特点,但是它没有考虑脉冲幅度对逻辑门传输延时造成的影响以及脉冲上升时间和下降时间的差异造成的脉冲宽度的展宽或衰减,同时它还忽略了逻辑门的不同输入引脚到输出端的延时参数的差别。本文在提出的四值脉冲参数模型基础上,提出如下计算过程可全面地考虑各种因素对电气屏蔽效应的影响。

表4 基础库单元EPP计算规则

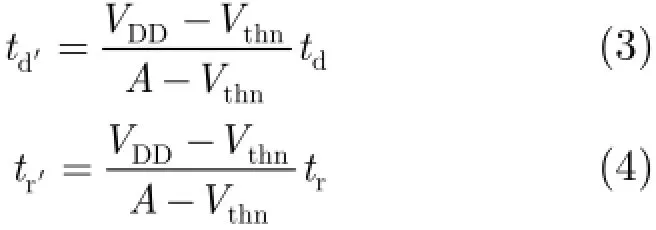

假设一个形状参数为(tr,tf,A,W)的正向SET脉冲出现在反相器的输入端,当脉冲幅度A不等于VDD时会对逻辑门的延时参数造成影响,利用式(3),式(4)[21]可重新计算由脉冲幅度A引起的逻辑门延时参数的变化。

其中,td和tr分别表示当输入SET脉冲幅度等于VDD时逻辑门的固有传输延时和跳变延时。td′和tr′分别表示当输入SET脉冲幅度不等于VDD时重新计算的逻辑门传输延时和跳变延时。Vthn表示NMOS管的翻转阈值。当输入为负向SET脉冲,可将式(3),式(4)中的Vthn替换为Vthp(PMOS管的翻转阈值)。

针对逻辑门输入端的SET脉冲,可根据如下步骤计算其传播到逻辑门输出端的脉冲形状参数。

首先,检查输入SET脉冲的幅度A。当A≤VDD/2,SET脉冲不能进行传播,终止计算;当A>VDD/2,先根据此SET脉冲的跳变延时tr及逻辑门负载电容查找库单元的延时参数表,获得逻辑门的传输延时及跳变延时,再根据式(3),式(4)重新计算当输入SET脉冲幅度不等于VDD时逻辑门的传输延时、跳变延时。

其次,检查输入SET脉冲的宽度W。当W≤td′,SET脉冲不足以引起逻辑门输出状态翻转,终止计算;当SET脉冲可以完全传播到逻辑门输出端,输出脉冲幅度为VDD,输出脉冲宽度可由式(5)计算获得;当脉冲虽然可以传播到逻辑门输出端,但输出脉冲幅度和宽度会受到逻辑门的电气削弱,可由式(5),式(6)计算。其中,td1′和td2′分别表示输入脉冲的第1和第2次跳变延迟时间。

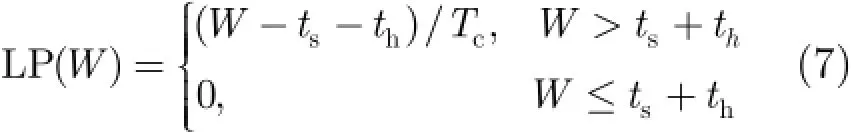

2.2.3锁存窗口屏蔽SET脉冲在经过逻辑屏蔽和电气屏蔽传播之后,其到达锁存器输入端的时间和脉冲宽度必须满足锁存器的采样时序要求才能被锁存:(1)锁存器数据端的SET脉冲必须在时钟沿到来之前的建立时间(ts)内保持不变;(2)锁存器数据端的SET脉冲必须在时钟沿到来之后的保持时间(th)内保持不变。假设SET脉冲到达锁存器的时间在时钟周期(Tc)内均匀分布,则SET故障脉冲被锁存的概率可由式(7)计算。

其中,W表示传播到锁存器数据端的SET脉冲宽度。由式(7)可知,当SET脉冲宽度小于等于时序单元的建立时间和保持时间之和时,它不能被锁存;反之,SET脉冲被锁存的概率和SET脉冲宽度成正比。

2.3单粒子瞬态脉冲传播模拟

为统一模拟3种屏蔽效应对电路失效率造成的影响,本文提出将四值脉冲参数(tr,tf,A,W)嵌入状态概率参数(P0,P1,Pa,Pb)中,即用向量(t,P0,P1,Pa,Pb,tr/tf,A)来表示电路中信号的状态。其中t表示脉冲出现在信号线上的时间,P0,P1,Pa,Pb分别表示脉冲在该信号线上出现的概率,示脉冲上升沿/下降沿的跳变时间,A表示脉冲幅度。当电路中的信号线上不存在脉冲,该信号线的状态可用一个概率事件表示:如果在时刻t电路中信号线上出现一个脉冲形状为(tr,tf,A,W)的正向SET脉冲,则该信号线的状态用两个概率事件表示:根据SET脉冲的极性,第1个概率事件代表脉冲上升沿,第2个概率事件代表脉冲下降沿。

图2详细说明了SET故障脉冲是如何在逻辑通路中传播。假设反相器的传播延时为1,与门和或门的传播延时为2,粒子在1 ns时刻撞击逻辑门G1,并在其输出端产生一个形状参数为(1 ps,2 ps,1.5 V,4 ps)的正向SET脉冲。首先,将代表SET脉冲形状的两个概率事件(1,0,0,1,0,1,1.5)和(5,0,0,0,1,2,1.5)加载到逻辑门G1的输出端。然后,计算脉冲传播到逻辑门G2和G3输出端的情况。以门G2的传播计算为例,SET脉冲传播到逻辑门G2输出端的故障传播概率参数可根据库单元EPP计算规则计算获得,而传播的脉冲形状参数则是根据逻辑门G 2的B输入端脉冲的跳变时间tr/tf及逻辑门G2的负载电容两个参数通过查找库单元延时参数查找表和式(3)~式(6)计算获得。最后,计算脉冲传播到逻辑门G 4输出端的情况。由于不同路径上的SET脉冲到达逻辑门G 4不同输入引脚的时间和脉冲极性不同,在逻辑门G4输出端可能产生多种波形。本文通过先计算输入引脚的每一个概率事件传播到逻辑门输出端的情况,再根据输出端概率事件的时间和极性确定所有可能的输出波形,如图2所示。

图2 SET脉冲在逻辑通路中的传播

3 单粒子效应软错误率分析平台

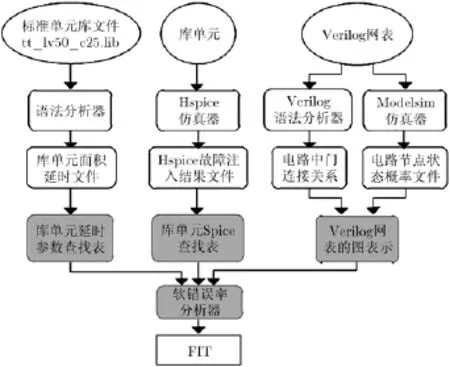

本文开发的软错误率分析平台的整体架构如图3所示,它主要包括4个部分。(1)创建库单元延时参数查找表:开发库文件语法分析器来提取库中各类型逻辑门的面积、延时以及管脚电容等参数信息。(2)创建库单元Spice查找表:利用HSPICE仿真获得库单元在不同的电荷量和负载情况下的四值脉冲参数。(3)创建电路的图表示:开发Verilog语法分析器对待测电路进行解析,得到电路的图表示;然后使用仿真工具得到电路中每个信号线的信号概率,用于构建电路图的边权值。(4)软错误率分析器:根据表5展示的软错误率分析算法进行软错误分析。首先根据逻辑门的负载电容查找库单元的Spice查找表,并将对应的故障概率事件标记到逻辑门的输出端;然后应用广度优先搜索算法提取出由故障点到输出端的逻辑通路;最后,通过逐层向后传播便可获得SET故障脉冲由逻辑门i传播到电路输出端j的故障传播概率:

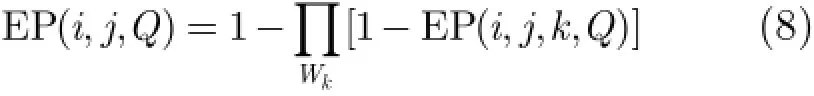

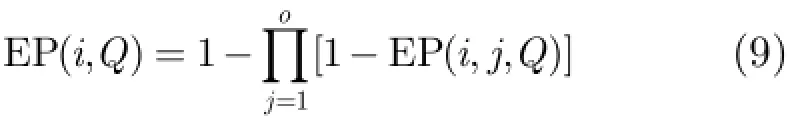

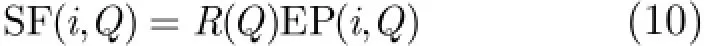

其中,k为由逻辑门i传播到输出端j的波形个数。如果一个SET脉冲传播到多个输出端,本文定义只要有一个输出端失效就认为系统失效。故由第i个逻辑门引起的故障传播概率为

其中,o为由逻辑门i传播到输出端的个数。考虑粒子撞击器件的本征概率,可获得由第i个逻辑门引起的系统失效率为

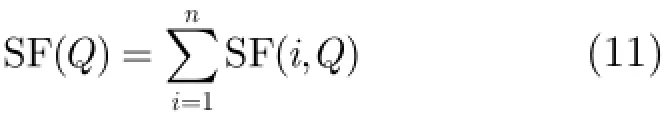

根据逻辑门节点的系统失效概率,可获得以FIT表示的电

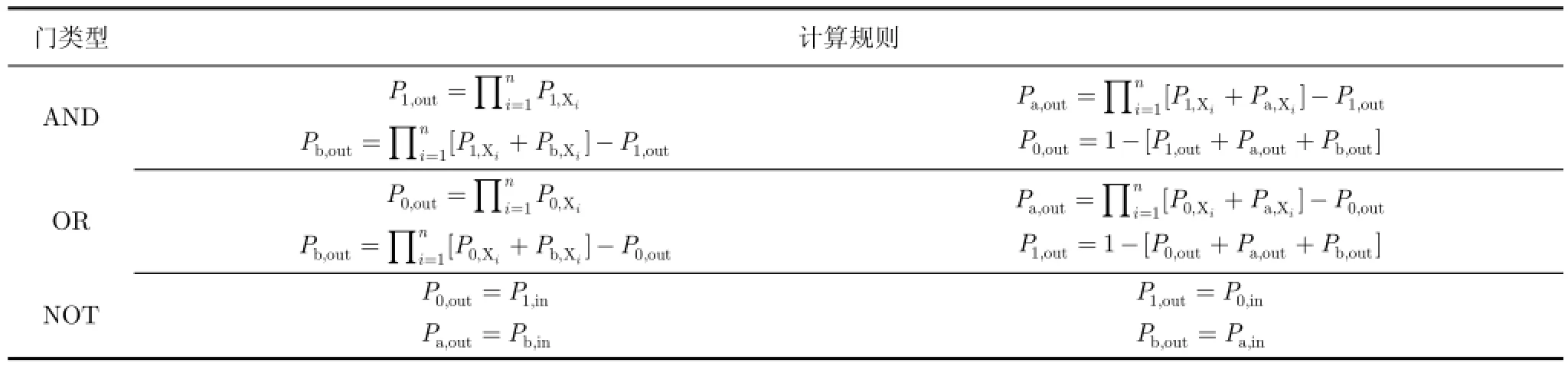

4 试验结果与分析

本文开发的SER分析平台由C++实现。测试电路为ISCAS’89和ISCAS’85基准电路,并应用Design Com piler工具对电路进行综合,工艺库为0.13μm标准单元库。式(1),式(2)中的参数参考文献[13]的取值:F为56.5 particles/(m2s);K为2.2 e-5;т为35 ps;NMOS和PMOS管的sQ分别为17.3 fC,6.5 fC。式(7)中的信号建立时间和保持时间设定为10 ps,时钟周期设定为1 ns。本节首先给出基于四值脉冲参数的电气屏蔽模型计算精度,然后针对选定电路进行软错误率分析并给出实验结果,最后与前人工作进行对比。

图3 软错误率分析平台整体架构图

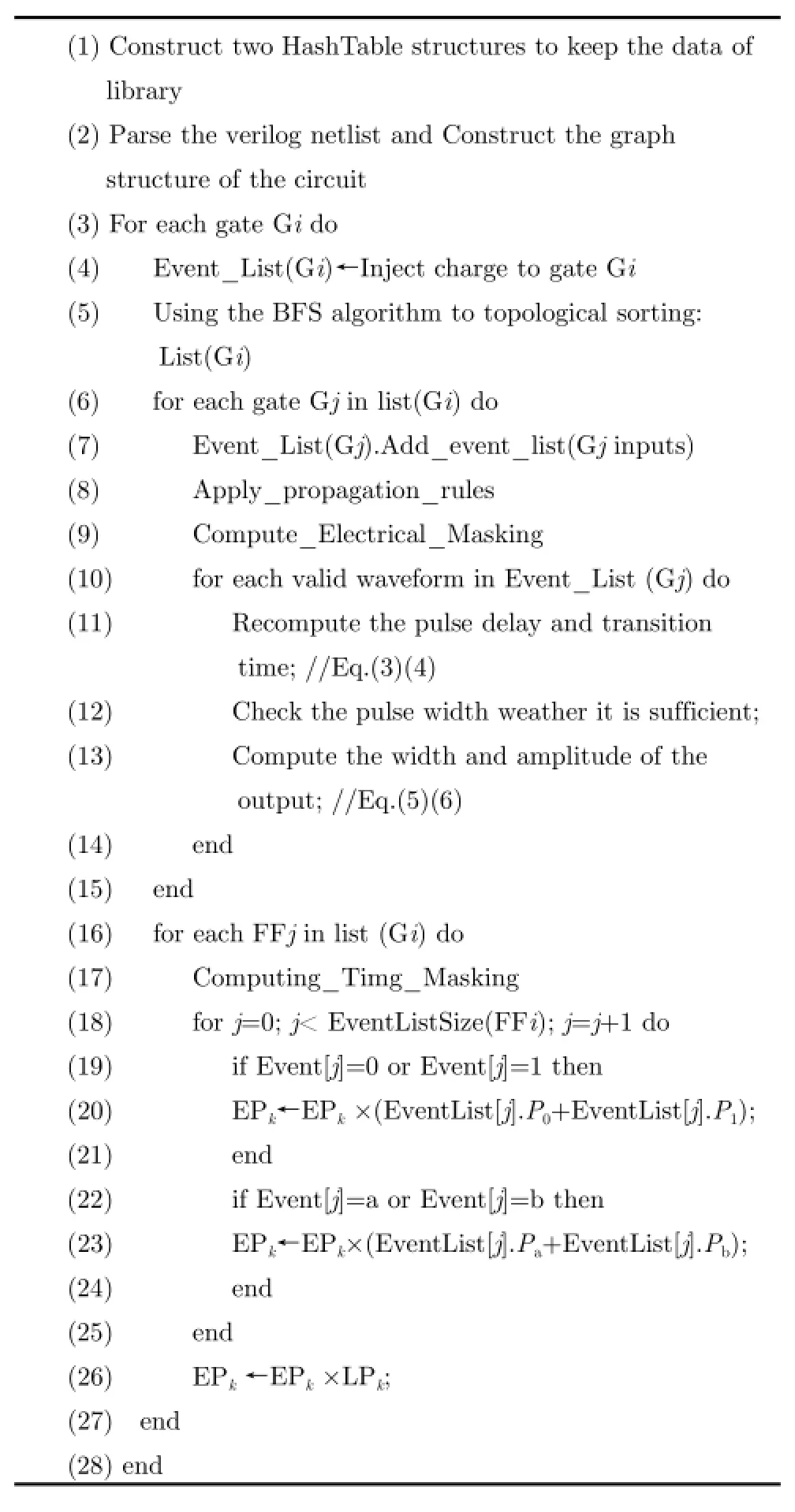

表5 软错误率分析算法流程

4.1四值脉冲参数模型的计算精度

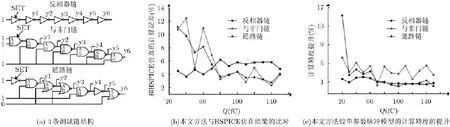

文献[22]指出SET脉冲在电路中传输3~4级逻辑后受电气屏蔽效应的影响将变得很小,故本文设计3条6级测试链来验证提出的基于四值脉冲参数的电气屏蔽模型的计算精度,如图4(a)所示。图4(b)给出了本文方法和HSPICE仿真的比对结果:当注入电荷量较小时,两种方法的偏差略大;随着注入电荷量的增加,两种方法的偏差逐渐减小且趋于稳定。导致这种趋势的原因为:当注入电荷量较小时,其产生的SET脉冲更易受到电气屏蔽的影响而导致计算精度下降。图4(c)给出了本文方法较单参数脉冲模型[20]在计算精度上的提升情况。通过对3条链进行分析可知:由于基于单参数脉冲模型的电气屏蔽模型计算过程简单,在注入电荷量较小的情况下,本文提出的SET脉冲传播模型较单参数脉冲模型计算精度有较大提高;在整个注入电荷量范围内可平均获得:反相器链1.06%,与非门链3.48%,通路链2.4%的计算精度提高。

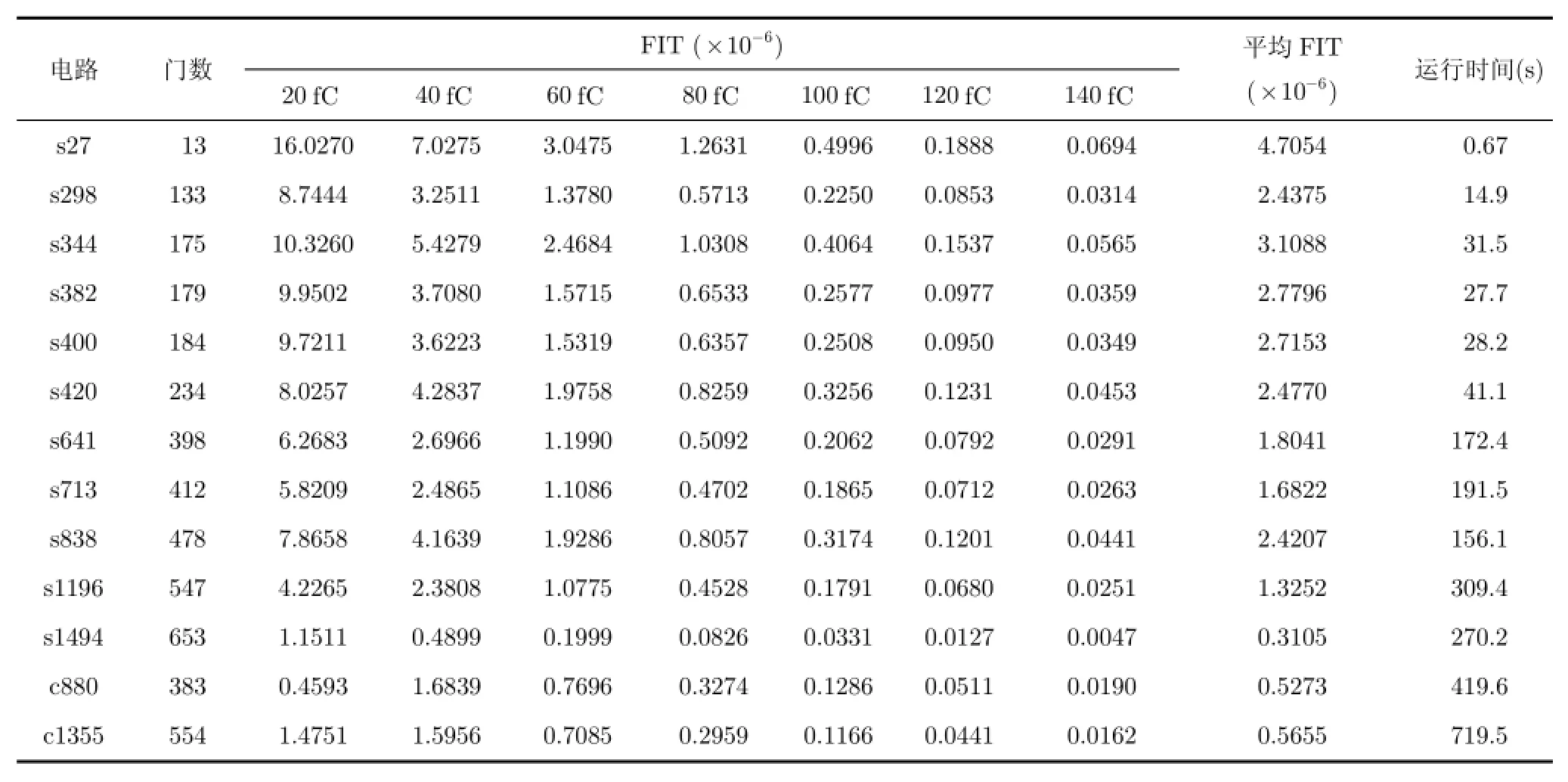

4.2电路软错误试验结果

表6为应用本文算法对ISCAS’89及ISCAS’85基准电路进行软错误分析获得的电路软错误率FIT及相应的算法运行时间。对所有的测试电路,本文采用个随机输入向量计算电路中信号线的信号概率。对于规模较小的电路本文算法可在几秒内完成计算,对规模较大的电路其最长用时也不超过12 m in。本文算法可快速分析大规模集成电路的软错误失效概率。

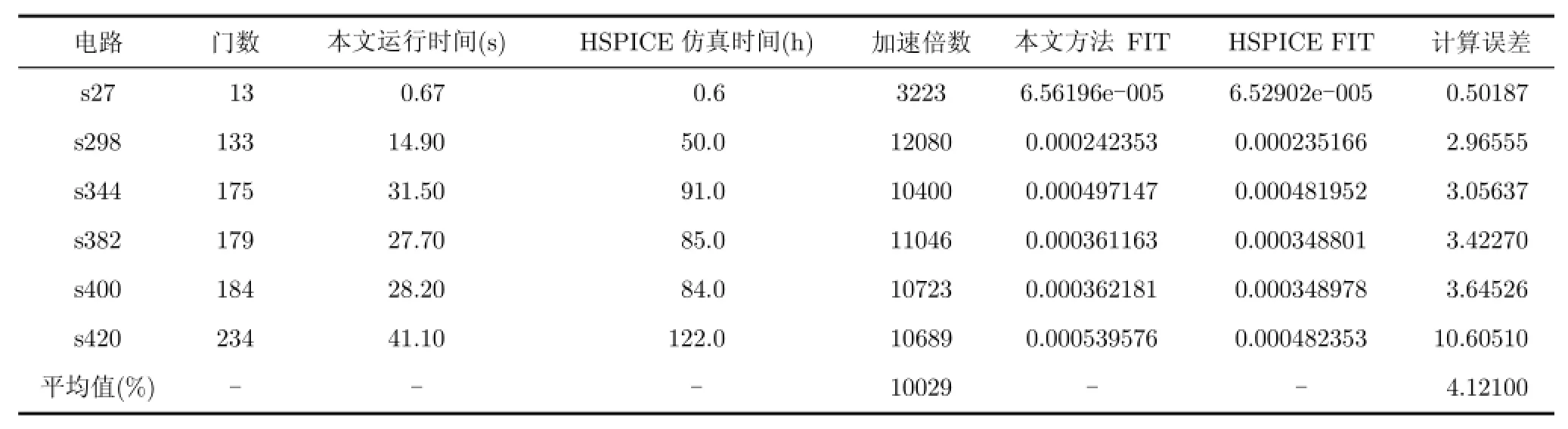

为了验证本文方法的有效性,将本文方法计算获得的软错误率结果和应用HSPICE仿真方法获得的结果进行比较。由于HSPICE仿真故障注入十分耗时(单个电路耗时近3 d时间),本文仅对几个规模较小的电路进行仿真故障注入。表7列出了应用两种方法获得的电路软错误率FIT结果以及两种方法的计算误差。由表7可知:和HSPICE仿真方法相比,本文方法在计算速度上可提升41 10×倍,平均计算误差仅为4.12%。

图4 测试链结构及比对结果

表6 FIT及算法运行时间

表7 本文方法和HSPICE仿真方法的比较

4.3和前人工作的对比

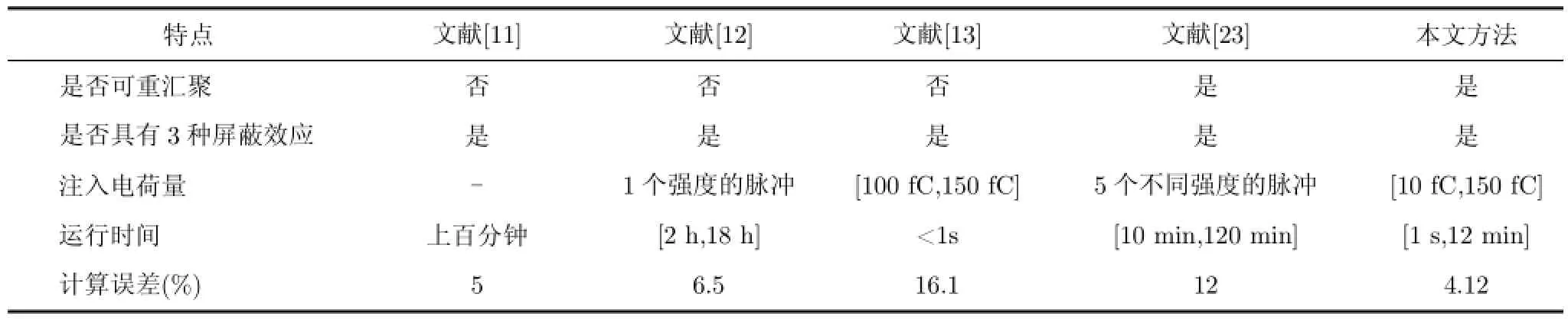

将本文方法与前人工作[11-13,23]进行比对并列于表8中。伊利诺伊大学[11]应用故障仿真来计算每条逻辑通路的敏感概率致使其计算速度较慢。宾夕法尼亚大学[12]阶段性地模拟3种屏蔽效应的主要缺点是没有考虑3种屏蔽效应之间的相关性。密歇根大学[13]采用的参数化描述符方法没有考虑重汇聚,从而造成计算精度较低。德克萨斯大学[23]在进行脉冲传播时仅考虑脉冲宽度,且对重汇聚做了简化处理,其计算精度虽略有提高,但是计算过程依旧很耗时。本文提出的基于四值脉冲参数模型,考虑到不同形状SET脉冲在传播过程中的展宽和衰减效应及脉冲在传播过程中的重汇聚;开发的基于图的分析算法可统一模拟逻辑电路的3种屏蔽效应,可在较短的时间内获得较高的计算精度,实现了计算精度与速度的有效折中。

表8 本文方法与已有方法的对比

5 结束语

本文提出了一个基于图的静态分析算法用于分析组合逻辑中的3种屏蔽效应。首先本文提出一种四值脉冲参数模型用于精确模拟SET脉冲形状。然后采用结合查找表与经验公式的方式来模拟SET脉冲在不同形状参数条件下的传播情况。通过将提出的四值脉冲参数嵌入故障传播概率参数的方式,本文提出的基于图论的分析算法可考虑扇出重汇聚问题并可同时模拟SET脉冲传播时的3种屏蔽效应。本文开发工作针对综合后的门级网表和通用的标准单元库完成,可同时对组合电路和时序电路中的组合逻辑部分进行分析。实验结果显示:本文算法计算速度较HSPICE仿真方法提升近41 10×倍;平均计算误差仅为4.12%。本文方法可自动完成电路的可靠性分析并可有效指导系统可靠性设计和容错机制的研究,使得系统在可靠性、性能和花销之间达到较好的权衡。

[1]王真,李舫,卢芳芳.电路软差错率评估综述[J].上海电力学院学报,2015,31(4):369-375.doi:10.3969/j.issn.1006-4729. 2015.04.013.

WANG Zhen,LI Fang,and LU Fangfang.Su rvey on circu it soft error rate evaluation[J].Journal of Shanghai University of Electric Power,2015,31(4):369-375.doi:10.3969/j.issn. 1006-4729.2015.04.013.

[2]闫爱斌,梁华国,黄正峰,等.基于故障概率的组合电路软错误率分析[J].电子测量与仪器学报,2015,29(3):343-351.doi: 10.13382/j.jem i.2015.03.005.

YAN Aibin,LIANG Huaguo,HUANG Zhengfeng,etal.Fau lt probability based SER analysis for combinational logic circuits[J].Journal of Electronic Measurement and Instrumentation,2015,29(3):343-351.doi:10.13382/j.jem i. 2015.03.005.

[3]HENKEL J,BAUER L,DUTT N,et al.Reliable on-chip systems in the nano-era:Lessons learnt and futu re trends[C]. 50th ACM/EDAC/IEEE Design Automation Con ference,Austin,TX,USA,2013:1-10.doi:10.1145/2463209.2488857.

[4]徐东超,绳伟光,何卫锋.面向System C的软错误敏感度分析方法[J].微电子学与计算机,2015,32(9):60-64.

XU Dongchao,SHENG Weiguang,and HEWeifeng.Method to analyze soft error sensitivity for System C[J]. M icroelectronics&Computer,2015,32(9):60-64.

[5]蔡烁,邝继顺,张亮,等.基于差错传播概率矩阵的时序电路软错误可靠性评估[J].计算机学报,2015,38(5):923-931.doi: 10.3724/SP.J.1016.2015.00923.

CAIShuo,KUANG Jishun,ZHANG Liang,et al.Reliability estim ation for soft error of sequential circu it based on error propagation probability matrix[J].Chinese Journal of Computer,2015,38(5):923-931.doi:10.3724/SP.J.1016. 2015.00923.

[6]MAHATME N N,GASPARD N J,ASSIST,et al.Impact of technology scaling on the combinational logic soft error rate[C].IEEE International Reliability Physics Sym posium,Waikoloa,HI,USA,2014:5F.2.1-5F.2.6.doi:10.1109/IRPS. 2014.6861093.

[7]MOHANRAM K.Simu lation of transients caused by singleevent upsets in combinational logic[C].IEEE International Test Con ference,Austin,TX,USA,2005:973-981.doi: 10.1109/TEST.2005.1584063.

[8]WANG F,XIE Y,RAJARAMANT R,et al.Soft error rate analysis for combinational logic using an accurate electrical masking model[C].20th International Conference on VLSI Design,Bangalore,India,2007:165-170.doi:10.1109/ VLSID.2007.145.

[9]MANSOUR W and VELAZCO R.An autom ated SEU fault-injection method and tool for HDL-based designs[J]. IEEE Transactions on Nuclear Science,2013,60(4): 2728-2733.doi:10.1109/TNS.2013.2267097.

[10]ENTRENA L,VALDERAS M G,CARDENAL R F,et al. Soft error sensitivity evaluation of mi-croprocessors by mu ltilevel em ulation-based fau lt in jection[J].IEEE Transactions on Computers,2012,61(3):313-322.doi: 10.1109/TC.2010.262.

[11]ZHANG M ing and SHANBHAG N R.Soft-error-rateanalysis(SERA)methodology[J].IEEE Transactions on Com puter-Aided Design of In tegrated Circuits and Systems,2006,25(10):2140-2155.doi:10.1109/ICCAD.2004.1382553.[12]RAJARAMANT R,KIM J S,VIJAYKRISHNAN N,et al. SEAT-LA:a soft error analysis tool for combinational logic[C].Proceedings of the 19th International Con ference on VLSIDesign,Hyderabad,India,2006:499-502.doi:10.1109/ VLSID.2006.143.

[13]RAO R R,CHOPRA K,BLAAUW D T,et al.Com puting the soft error rate of a combinational logic circuit using parameterized descrip tors[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2007,26(3):468-479.doi:10.1109/TCAD.2007.891036.

[14]ZIVANOV N M and MARCULESCU D.Circuit reliability analysis using sym bolic techniques[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2006,25(12):2638-2649.doi:10.1109/TCAD.2006.882592.

[15]ZIVANOV N M and MARCULESCU D.M odeling and optim ization for soft-error reliability of sequential circuits[J]. IEEE Transactions on Com puter-Aided Design of Integrated Circuits and System s,2008,27(5):803-816.doi:10.1109/ TCAD.2008.917591.

[16]ASADI H,TAHOORI M B,FAZELI M,et al.Efficient algorithm s to accurately com pute derating factors of digital circuits[J].M icroelectronics Reliability,2012,52:1215-1226.

[17]HAMAD G,HASAN S,MOHAMED O,et al.New insights into the single event transient propagation through static and TSPC logic[J].IEEE Transactions on Nuclear Science,2014,61(4):1618-1627.doi:10.1109/TNS.2014.2305434.

[18]ARTOLA L,GAILLARDIN M,HUBERT G,et al.Modeling single event transients in advanced devices and ICs[J].IEEE Transactions on Nuclear Science,2015,62(4):1528-1539.doi: 10.1109/TNS.2015.2432271.

[19]SHIVAKUMAR P,KISTLER M,KECKLER S W,et al. Modeling the effect of technology trendson the soft error rate of com binational logic[C].International Conference on Dependable System s and Networks,Bethesda,MD,USA,2002:389-398.doi:10.1109/DSN.2002.1028924.

[20]OMANA M,PAPASSO G,ROSSI D,et al.A model for transient fau lt p ropagation in combinational logic[C]. Proceedings of the 9th IEEE International On-Line Testing Sym posium,G reece,2003:111-115.doi:10.1109/ICECS. 2015.7440265.

[21]FIROUZI F,KIAMEHR S,MONSHIZADEH P,et al.A model for transient fault propagation considering glitch am plitude and rise-fall time m ismatch[C].2nd Asia Sym posium on Quality Electronic Design,Penang,Malaysia,2010:89-92.doi:10.1109/ASQED.2010.5548223.

[22]RAO R R,CHOPRA K,BLAAUW D,et al.An efficient static algorithm for com puting the soft error rates of combinational circuits[C].Design,Automation and Test in Europe,Munich,Germany,2006,1:1-6.doi:10.1109/DATE. 2006.244060.

[23]ZHANG B,WANG W S,and ORSHANSKY M.FASER:fast analysis of soft error susceptibility for cell-based designs[C]. Proceedings of the 7th International Symposium on Quality Electronic Design,San Jose,CA,USA,2006:755-760.doi: 10.1109/ISQED.2006.64.

李悦:女,1987年生,博士生,研究方向为数字集成电路软错误分析.

蔡刚:男,1980年生,助理研究员,研究方向为嵌入式IP设计及抗辐照理论.

李天文:男,1987年生,博士生,研究方向为抗辐照的加固寄存器.

杨海钢:男,1960年生,研究员,研究方向为数模混合信函SOC设计和大规模集成电路设计.

Propagation Mechanism of Single Event Transient and Soft Error Rate Analysis M ethod Based on Four-value Pu lse Parameters M odel

LIYue①②CA IGang①LITianwen①YANG Haigang①①

①(Institute ofElectronics,Chinese Academy ofSciences,Beijing 100190,China)

②(University of the Chinese Academy ofSciences,Beijing 100049,China)

W ith the shrinking of feature size,soft errors due to Single Event Transient(SET)effect become the main reliability threat for aerospace deep sub-m icron VLSI circuits,and the generation and propagation of SET pu lse is also a hot issue in the study of soft error.Resu lts of SET pu lse propagation on logic chains show that the difference of rise and fall time of SET pu lse canmake thew idth of output pu lsewidened or lessened.Thew idth and am plitude of SET pulse can determ inewhether it is electrically masked out.A four-value pu lse parametersmodel is proposed to accurately characterize the shape of SET pulse,and then the LUT-based technique is combined w ith experiential equations tomodel the transm ission p rocess of SET.The proposed four-value pu lse parametersmodel can model the effect of b roadening or attenuation of SET pulse,and it has calculation p recision im provem ent of 2.4%com pared w ith single param eter m odel.This paper app lies the graph-based error propagation probability analytic algorithm to estim ate the logicalm asking in pulse p ropagation.The experimental resultson ISCAS’89 and ISCAS’85 circuitsshow that theaverage deviation of thismethod and HSPICE simu lationmethod is4.12%and the calcu lation speed is 10000 times.Thismethod can be used to analyze quickly the soft error rate of large scale integrated circuits.

Very Large Scale Integration(VLSI);Soft error rate;Single Event Transient(SET);Four-value pu lse parameters;Error p ropagation probability

1 引言

当空间环境中的高能粒子击中电子器件中处于敏感状态(OFF状态)晶体管漏区,沿入射通路产生大量的电子、空穴对。在漏极和衬底之间电场的作用下,空穴被压向衬底,电子被漏极吸收,沿着入射通路产生一个由漏极流向衬底的电流脉冲,从而在晶体管的输出端产生一个电压脉冲。在组合逻辑电路中,此电压脉冲是暂时的,输出电压会很快恢复到正常值,此现象称为单粒子瞬态(Single Event Transient,SET)。如果入射粒子击中的是时序单元,或由组合逻辑传播过来的SET脉冲被时序单元捕获,会造成存储信息的改变,此现象称为单粒子翻转(Single Event Upset,SEU)[1]。因为SET和SEU不会直接导致芯片硬件结构的损坏,所以称其所导致的电路工作不正常的现象为软错误。集成电路受软错误影响的严重程度可以用软错误率来表征,单位为FIT(Failure In Time),即器件在10亿小时内发生失效的次数[2]。过去,时序单元被认为是电路中最敏感的部分。然而,随着特征尺寸和电源电压的不断减小,组合逻辑单元的临界电荷越来越小,大量的低能量粒子便可产生足够的淀积电荷,从而引起组合逻辑状态的改变[35]-。此外,时钟频率的提高削弱了锁存窗口对SET脉冲的屏蔽效应;流水线深度的增加减少了脉冲传播的级数,从而削弱了逻辑和电气屏蔽效应。研究表明,在50 nm工艺节点下,由组合逻辑中SET引起的系统失效率已经接近甚至超过时序单元引起的系统失效率[6]。因此,SET将成为未来采用先进工艺集成电路最主要的可靠性威胁。

s:The National Natural Science Foundation of China(61271149),The National Science and Technology M ajor Special Fund(2013ZX 03006004)

TN402

A

1009-5896(2016)08-2113-09

10.11999/JEIT 151254

2015-11-09;改回日期:2016-04-01;网络出版:2016-05-31

杨海钢yanghg@m ail.ie.ac.cn

国家自然科学基金(61271149),国家科技重大专项资助(2013ZX 03006004)