应用于低压锁相环的高性能可编程电荷泵

2016-05-05朱樟明杨银堂

梁 亮,朱樟明,杨银堂

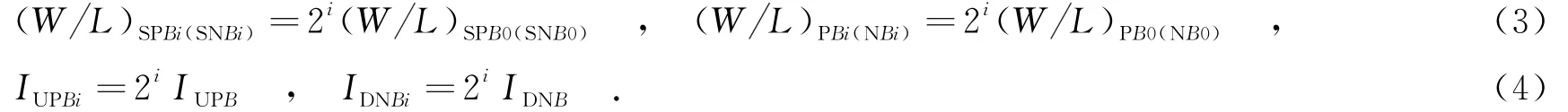

(西安电子科技大学微电子学院,陕西西安 710071)

应用于低压锁相环的高性能可编程电荷泵

梁 亮,朱樟明,杨银堂

(西安电子科技大学微电子学院,陕西西安 710071)

摘要:提出了一种应用于低压锁相环的输出电流可编程电荷泵.该电荷泵由两个子电荷泵电路组成.每个子电荷泵都采用了反馈控制和复制偏置技术来保证输出的充/放电电流有接近理想的匹配性.利用电流求和结构,两子电荷泵在宽输出电压范围内输出电流的变化被相互补偿,从而得到相对恒定的总电流.该电荷泵可以编程输出从50μA到1.55 m A变化的电流,并以50μA为最小步进.在0.1 V到1.05 V的宽输出电压范围内,基于0.13μm CMOS工艺的后仿真结果显示输出电流的失配率和变化率被分别限制在0.15% 和5%以内.精确的匹配特性极大地减小了锁相环的静态相位误差和参考杂散,同时恒定的输出电流有利于稳定锁相环的动态特性,所以该电荷泵能满足低压宽带锁相环的应用要求.

关键词:电荷泵;输出电流匹配;输出电流可编程;锁相环

1 电荷泵及其非理想因素

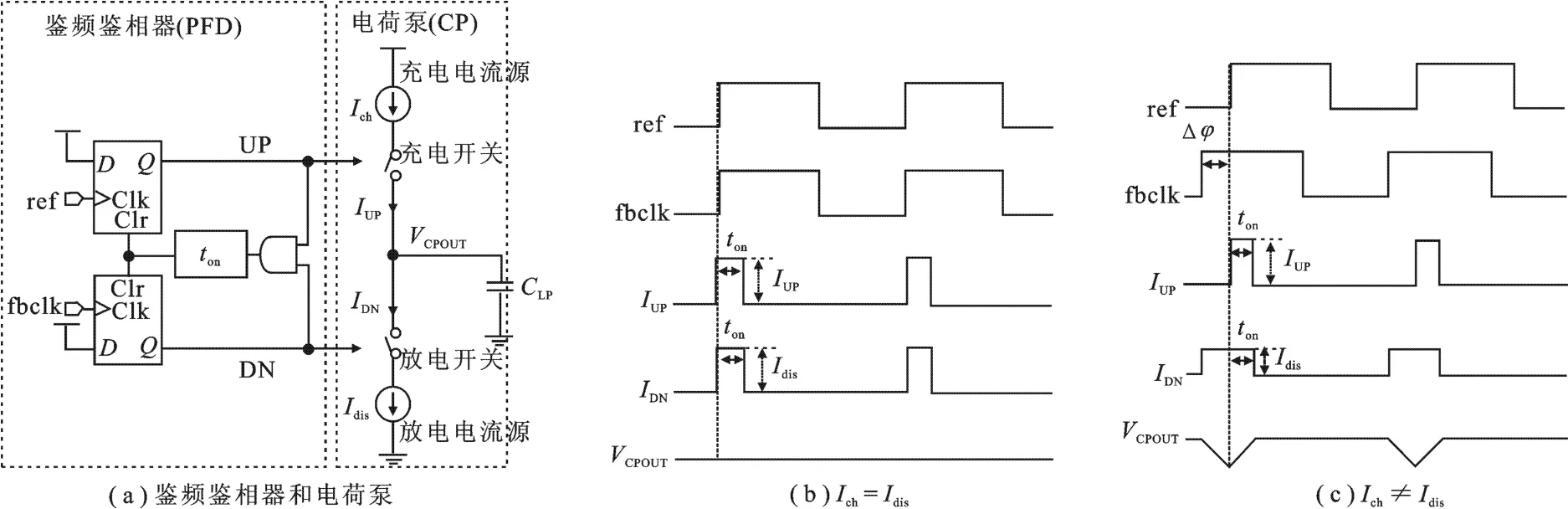

锁相环(Phase-Locked Loop,PLL)是广泛应用于通信和数字系统的基础模块[1-5].电荷泵锁相环因具有宽的频率捕获范围和理想情况下无静态相位误差的优点已成为当前应用的主流.鉴频鉴相器(Phase Frequency Detector,PFD)和电荷泵作为其中的关键部分负责将参考时钟和反馈时钟间的相位差转化为压控振荡器(Voltage Controled Oscillator,VCO)的控制电压,如图1(a)所示.在理想情况下,电荷泵的充电电流源Ich和放电电流源Idis能始终输出匹配的电流IUP和IDN,所以输出电压VCPOUT在环路锁定时保持不变,且PFD的两个输入信号ref和fbclk之间没有相位差.但是实际电荷泵存在许多非理想因素会破坏上述特性.首先要考虑的是输出电流失配.如图1(c)所示,在PFD重置延时ton内,失配电流IUP和IDN会引起VCPOUT的波动,并引起ref和fbclk之间的静态相位误差Δϕ和参考杂散[6-8].而在小数分频频率综合器应用中,电流失配产生的非线性会将ΔΣ调制器整形到高频处的量化噪声混叠回到低频带内,急剧恶化相位噪声[1-2].另一个重要的非理想因素是电荷泵输出电流IUP和IDN会随VCPOUT的变化而改变[5,8].这将导致锁相环的环路带宽和动态性能发生漂移,甚至引发稳定性问题.第3个问题是电荷泵的噪声[9],它直接影响锁相环的相位噪声.此外,充/放电通路上的开关管在转换时产生的电流毛刺和控制信号UP/DN间的不同步也会使电荷泵的工作偏离理想状态[7,10-11].

图1 鉴频鉴相器和电荷泵的原理图以及在输出电流匹配和失配时输入、输出信号的时序图

2 文中提出的可编程电荷泵

文中提出的输出电流可编程电荷泵如图2所示,可编程特性不仅拓宽了它的适用范围,还为锁相环提供了同时优化相位噪声和动态性能的途径[9].总电路由两个子电荷泵A/B、偏置(BIAS)以及两组异或门构成的充/放电开关同步驱动器(DRIVER)组成.其中子电荷泵A/B的输出电流随VCPOUT的变化趋势是相反的,所以通过合理的设计,就使两者的输出电流之和在宽的VCPOUT范围内保持稳定.同时,每个子电荷泵各自包含5个开关电流源支路A0至A4(B0至B4)和一个带运算放大器的偏置电流匹配支路AMAT(BMAT),利用反馈控制和复制偏置技术,各子电荷泵有匹配的充/放电电流.所有电流源支路的开关被设计在电流源管的源极来抑制电流毛刺对电荷泵输出端的影响[7].

在子电荷泵A中,支路A0是单位支路,其他支路是它二进制加权复制的结果.如果A0中充电开关SPA0和电流源PA0的尺寸分别为(WL)SP A0和(WL)PA 0并输出大小为IUP A的充电电流,放电开关SNA0和电流源NA0的尺寸分别为(WL)SN A0和(WL)N A0并输出放电电流IDN A,那么支路Ai中晶体管的尺寸和输出电流为

在理想匹配时,匹配支路AM AT中的偏置电流和支路A0中的输出电流大小相同,即IA ref=IUP A=IDN A,且两者对应位置的晶体管尺寸相同.子电荷泵B的结构与A类似.支路B0是其中的单位支路,支路BMAT的偏置电流IBref和相应晶体管尺寸与支路B0中的完全相同,支路Bi的晶体管尺寸和输出电流则为

因为控制支路Ai/Bi输出电流的开关管仅在信号EN[i]为高时才会同时导通,所以总电荷泵的编程输出电流IUP和IDN可以表示为

图2 文中设计的可编程电荷泵电路图

2.1 输出电流匹配

式(5)和式(6)说明只要每个子电荷泵的输出电流匹配,即IUP A=IDN A和IUP B=IDN B,那么通过合理的电路、版图设计就能使总电荷泵的任意编程输出电流匹配.为了抑制晶体管沟道长度调制效应导致的失配[11],在支路AM AT和BMAT中分别使用放大器OTA1和OTA2来构成负反馈环路,以使VAD和VBD点的电压在要求的输出范围内始终等于VCPOUT.假设两个放大器都是理想的,那么子电荷泵A中所有支路的放电通路电流源管NA0-4的偏置情况始终与NM4相同,因此NM4管和NA0管中电流相同,即IA ref=IDN A.而所有充电通路的电流源管PA0-4和PM1管的栅极电压VPA都受放大器OTA1输出的控制,因此通过调整VPA总能得到IUP A= IA ref.这样就得到都等于IA ref的IUP A和IDN A,使子电荷泵A的输出电流匹配.同理,子电荷泵B的输出电流也能匹配,即IUP B=IDN B=IB ref.此时放大器OTA2的输出控制的是各支路Bi放电通路上的N沟道金属氧化物半导体(N-channel Metal Oxide Semiconductor,NMOS)电流源管的栅极电压VNB.综上所述,只要支路AM AT/BMAT中的放大器OTA1/OTA2有足够高的增益,子电荷泵A/B及其求和得到的总电荷泵的输出电流就能匹配,式(5)和式(6)也就能写为以下表达式:

2.2 宽输出电压范围内相对恒定的输出电流

虽然运用负反馈控制和复制偏置技术能很好地解决失配的问题,但是在宽的VCPOUT范围内单个子电荷泵的输出电流会有很大变化.在图2中,当VCPOUT上升时NM4和PM2管的漏极电压VAD和VBD也会上升,在晶体管沟道长度调制效应作用下IA ref增大而IB ref减小.式(7)说明,若IA ref和IB ref相反的变化趋势能在求和过程中相互补偿,就能得到对VCPOUT变化不敏感的IUP和IDN.以下是由ΔVCPOUT引起的IA ref和IB ref的变化量:的情况下,采用沟长较大的电流源管使λn和λp为较小且近似的值.同时在VCPOUT=VDD2附近,利用复制偏置使IA ref和IB ref都等于同一参考电流Iref.因此,式(8)和式(9)的求和结果为Iref(λn-λp)ΔVCPOUT,若有λn≈λp,则ΔVCPOUT对输出电流的作用就能被极大地抑制,从而使IUP和IDN在宽VCPOUT范围内稳定.

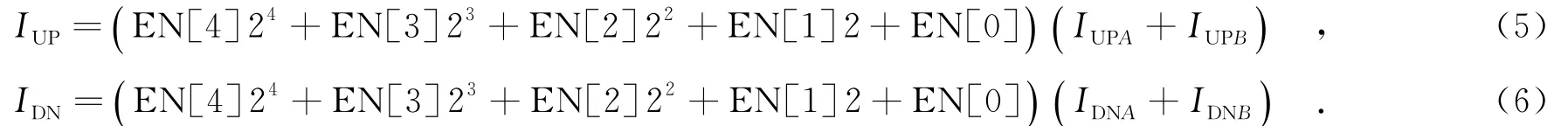

2.3 运算放大器

运算放大器OTA1和OTA2的作用至关重要,它们决定着整个电荷泵的静态和动态性能.考虑到两者的输入共模电平需要从接近地电位变化到接近电源电位,因此,需要轨到轨的输入级.为了获得足够大的增益且易于环路的稳定性设计,采用了如图3所示折叠共源共栅放大器结构.其中图3(a)是两者相同的输入级,图3(b)和图3(c)则分别是OTA1和OTA2的主增益级.输入级和主增益级在对应节点(A至D)相连.

其中,λn和λp分别是NM4管和PM2管的沟道长度调制因子,Vov n和Vov p则是它们的过驱动电压.所以仔细地设计晶体管尺寸和过驱动电压就能使ΔIA ref和ΔIB ref抵消的很好.但在实际电路中,完全消除输出电流的变化几乎不可能.为了减少电路和版图设计的复杂性,采用以下的简单方法.首先在兼顾电荷泵动态响应速度

图3 具有轨到轨输入级的运算放大器OTA1和OTA2

图3(a)描述的输入级在轨到轨的输入范围内能提供相对恒定的跨导.其中P沟道金属氧化物半导体(P-channel Metal Oxide Semiconductor,PMOS)差分对PM1/2和NMOS差分对NM1/2工作在深度相近的亚阈值区.通过复制电路检测和电流镜像技术,这两个差分对中的偏置电流Ib p和Ib n被分别复制到NB7和NB8管的漏极电流.在电流求和节点Sum处,由基尔霍夫电流定律可知总有Ibias=Ib p+Ib n成立.又因为工作在深亚阈值区的晶体管的跨导和偏置电流间存在稳定的正比关系,所以该输入级就能在轨到轨范围内产生恒定的跨导.虽然OTA1和OTA2的输入级相同,两者的主增益级略有不同,如图3(b)和图3(c)所示.这样的设计能有效减小两放大器输入端的直流失调误差.此外,连接在OTA1/OTA2输出端的电阻R2/R3和电容C2/C3能在反馈环路中引入左半平面零点,有利于环路的稳定性和带宽保持.同时,连接在两子电荷泵输出支路和匹配支路间的电容(C1/C4)和电阻(R1/R4)构成的低通滤波器也能有效地抑制充/放电开关转换时VP B和VN A上的电压波动对放大器所在环路的影响.

3 设计结果与讨论

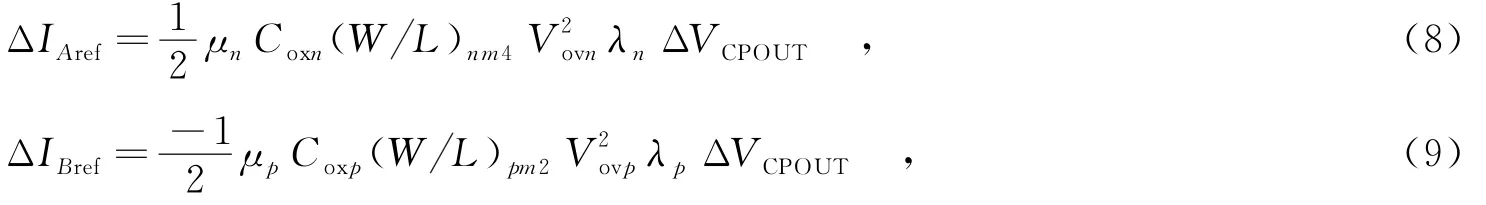

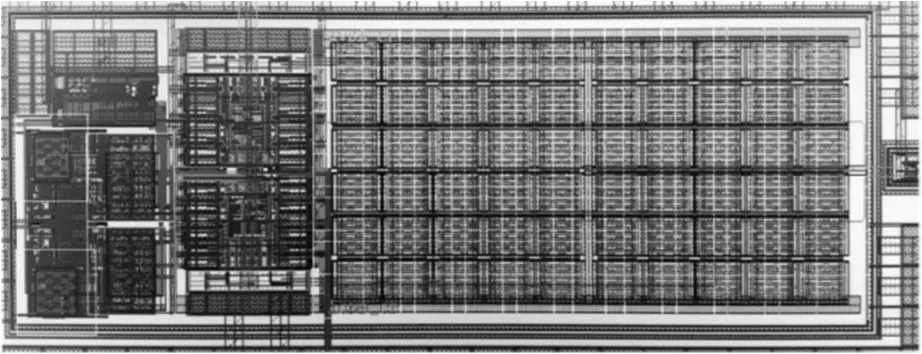

该电荷泵采用0.13μm互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor transistor,CMOS)工艺进行设计,并应用于一款输出频率覆盖4~6 GHz范围的宽带锁相环频率综合器芯片.在1.2 V供电电压下,为了使集成VCO能用尽量少的子带数来获得足够低的VCO增益KVCO,设计指标要求电荷泵能在0.25~0.95 V的输出电压范围内工作.为留有足够的裕度,该电荷泵能在0.1~1.05 V的宽电压范围内有效地输出从50μA~1.55 m A的可编程充/放电电流,并以50μA为最小步进.图4是文中设计的电荷泵版图,面积为430μm×160μm.

图4 文中设计的可编程电荷泵版图

图5(a)和图5(b)分别给出了0~1.2 V输出电压VCPOUT范围内子电荷泵A和B各支路输出电流(IUP Ai/IDN Ai和IUP Bi/IDN Bi)的仿真结果.可见在VCPOUT= 0.6 V附近,支路Ai和Bi都能输出约2i×25μA的充/放电电流,并且能在很宽的电压范围内实现精确匹配.当输出接近0 V或1.2 V时,两子电荷泵电流发生明显失配,因为此时输出支路上栅极连接放大器输出的电流源管工作在深三极管区,所以必须确保电荷泵所有支路上的电流源管工作在饱和区.总电荷泵中受信号EN[i]控制的各支路的输出电流和的仿真结果如图6(a)所示.图6(b)考察了对应支路的失配情况,其中支路i的电流失配率定义为

图5 子电荷泵A和B中各支路输出电流与输出电压的关系

图6 总电荷泵各支路的输出电流、电流失配率与输出电压的关系

由图6可知,当VCPOUT在0.1~1.05 V范围内,总电荷泵所有支路输出电流的失配率和变化率都被控制在0.15%和5%以内.考虑到实际应用中,总电荷泵的输出电流是各支路输出电流的编程和,所以在50μA~1.55 m A的编程范围内,总电流的失配率和变化率也不会超过0.15%和5%.

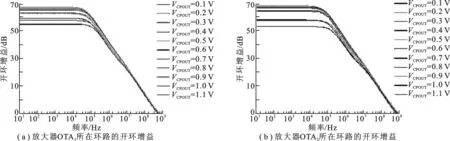

为保证电荷泵的动态性能,笔者对放大器OTA1和OTA2所在环路进行交流仿真.因为连接在这两个放大器输出端的电容和电阻能产生有频率补偿作用的左半平面零点,所以在要求的输出电流和电压范围内,两个环路都有稳定的频率响应.当电荷泵输出电流设定为100μA时,图7(a)和图7(b)给出了两个环路交流仿真的典型结果.可见,在要求的宽输出电压范围内,每个环路都有大于50 dB的开环增益和约200 MHz的稳定单位增益带宽,可以很好地满足电荷泵低失配、高速和宽输出范围的要求.

最后,笔者采用瞬态仿真对电荷泵的输出特性进行更直观的验证.在26 MHz参考时钟频率、100μA电荷泵输出电流和10 p F环路滤波电容的典型应用条件下,涵盖整个VCPOUT范围的持续充电和放电过程的瞬态仿真结果分别显示在图8(a)和图8(b)中.两图中VCPOUT所表现出的线性上升和下降特性说明电荷泵输出电流十分稳定,几乎不受VCPOUT影响.仿真细节显示VAD和VBD能快速且稳定地跟随VCPOUT的上升和下降,这保证了电荷泵的输出电流在动态时也能良好匹配.综上所述,文中设计的电荷泵具有接近理想的性能.

图7 放大器OTA1和OTA2所在反馈环路的开环增益仿真结果

图8 电荷泵对环路滤波电容CLP持续充电和放电时VCPOUT、VAD和VBD的瞬态仿真结果

4 结 论

文中提出了一种适合低压锁相环应用的高性能电荷泵,并采用0.13μm CMOS工艺进行了电路和版图设计.在1.2 V供电电压下,该电荷泵能编程输出从50μA到1.55 m A变化的充/放电电流,以50μA为最小步进.在0.1 V到1.05 V的宽输出电压范围内电荷泵输出电流的失配率和变化率被分别控制在0.15%和5%以内.此外该电荷泵的可编程特点还能用于锁相环相位噪声和动态性能的同时优化.

参考文献:

[1]LEVANTINO S,MARZIN G,SAMORI C,et al.A Wideband Fractional-N PLL with Suppressed Charge-pump Noise and Automatic Loop Filter Calibration[J].IEEE Journal of Solid-State Circuits,2013,48(10):2419-2429.

[2]GAIED D,HEGAZI E.Charge-pump Folded Noise Cancelation in Fractional-N Phase-Locked Loop[J].IEEE Transactions on Circuits and System II:Express Briefs,2014,61(6):378-382.

[3]MOON J W,CHOI K CI,CHOI W Y.A 0.4 V,90~350-MHz PLL with an Active Loop-filter Charge Pump[J].IEEE Transactions on Circuits and System II:Express Briefs,2014,61(5):319-323.

[4]YOSHIMURA T,IWADE S,MAKINO H,et al.Analysis of Pull-in Range Limit by Charge Pump Mismatch in a Linear Phase-locked Loop[J].IEEE Transactions on Circuits and System I:Regular Papers,2013,60(4):896-907.

[5]冯焱,罗阳,陈贵灿.具有稳定环路带宽功能的多模分数频率综合器[J].西安电子科技大学学报,2013,40(5):119-123.FENG Yan,LUO Yang,CHEN Guican.Multi-mode Fractional-N Frequency Synthesizer with a stabilized loopbandwidth[J].Journal of Xidian University,2013,40(5):119-123.

[6]KAMAL N,AL-SARAWI S F,ABBOTT D.Reference Spur Suppression Technique using Ratioed Current Charge Pump[J].Electronics Letters,2013,49(12):746-747.

[7]ZHOU J Z,WANG Z G.A High-performance CMOS Charge-pump for Phase-locked Loops[C]//Proceedings of the International Conference on Microwave and Millimeter Wave Technology:2.Piscataway:IEEE,2008:839-842.

[8]JORAM N,WOLF R,ELLINGER F.High Swing PLL Charge Pump with Current Mismatch Reduction[J].Electronics Letters,2014,50(9):661-663.

[9]YAN H,QIN P,CHEN D P.A New Phase Noise Cancelling Technique for Fractional-N PLL[C]//IEEE International Conference on Solid-State and Integrated Circuit Technology.Piscataway:IEEE,2014:1-3.

[10]HATI M K,BHATTACHARY T K.A PFD and Charge Pump Switching Circuit to Optimize the Output Phase Noise of the PLL in 0.13-μm CMOS [C]//International Conference on VLSI Systems,Architecture,Technology and Applications.Piscataway:IEEE,2015:1-6.

[11]TSITUORAS A,PLESSAS F,BIRBAS M,et al.A 1V CMOS Programmable Accurate Charge Pump With Wide Output Voltage Range[J].Microelectronics Journal,2011,42(9):1082-1089.

(编辑:李恩科)

High-performance programmable charge pump for low voltage PLLs

LIANG Liang,ZHU Zhangming,YANG Yintang

(School of Microelectronics,Xidian Univ.,Xi’an 710071,China)

Abstract:This paper proposes a charge pump with a programmable output current for low voltage phaselocked loops(PLLs).It consists of two sub-units both of which leverage replica bias and feedback control techniques to achieve perfect match between charging and discharging currents.With the help of the current summing structure,the output current variation in each sub charge pump can be compensated by the other.Thus,their sum current remains relatively constant in a wide output voltage range.The charge pump can be programmed to output a 50μA~1.55 m A current,with a 50μA minimum step.It is designed in a 0.13μm CMOS process and the post-layout simulation demonstrates the total current mismatch and variation rates are limited in 0.15%and 5%,over the output voltage range of 0.1~1.05 V.Such precise matching greatly suppresses the reference spur and static phase error,and the good current constancy is favorable for dynamic design.Both features render our design suitable for low voltage PLLs.

Key Words:charge pump;output current matching;programmable output current;phase-locked loop

作者简介:梁 亮(1984-),男,西安电子科技大学博士研究生,E-mail:leo_1116@126.com.

基金项目:国家863计划资助项目(2013AA014103);国家自然科学基金资助项目(61234002,61322405,61306044,61376033);电子元器件可靠性物理及其应用技术重点实验室开放基金资助项目(ZHD201302)

收稿日期:2015-05-14

doi:10.3969/j.issn.1001-2400.2016.02.032

中图分类号:TN911.8

文献标识码:A

文章编号:1001-2400(2016)02-0186-07