基于FPGA的二维OS-CFAR设计与实现

2016-01-12刘中祥,宋志勇,付强

基于FPGA的二维OS-CFAR设计与实现

刘中祥,宋志勇,付强

(国防科学技术大学电子科学与工程学院,长沙 410073)

摘要:二维OS-CFAR检测器在雷达目标检测中具有较好的检测性能,特别是在多目标以及动态杂波环境中,具有较强的抗干扰目标的能力。本文基于FPGA设计和实现了二维OS-CFAR检测器,采用并行寻址以及二元积累判决等结构解决了FPGA实现中二维空间上参考单元寻址困难以及排序运算计算量大、耗时长、实时性不高的问题,实现了对距离-多普勒平面内所有检测点的流水作业,提高了二维有序恒虚警检测的实时性,满足了工程应用的要求。通过将FPGA实现结果与理论检测结果进行比较,验证了本文方法的有效性。

关键词:二维OS-CFAR;FPGA;数据流;二元积累

doi:10.13442/j.gnss.1008-9268.2015.05.014

中图分类号:TN957

文献标志码:A

文章编号:1008-9268(2015)05-0076-05

收稿日期:2015-05-25

作者简介

Abstract:Two-dimensional(2D) Ordered Statistics Constant False Alarm Rate(OS-CFAR) detector usually exhibits good performance in radar target detection. It has good anti-jamming capacity especially in the non-homogeneous environment caused by strong interfering targets and dynamic clutter. In this paper, a 2D OS-CFAR detector is designed and implemented based on FPGA. The structures, including parallel addressing and binary integration decision, are exploited to resolve the problems such as difficulty in reference cell addressing, large computation amount, time consuming and low real-time poverty in the ordering process, which often occur in the implementation process with FPGA. All the points in the Range-Doppler plane are detected in data flow processing and the real-time poverty of the 2D OS-CFAR is improved, which meets the requirements in engineering. A comparison of the experimental results based on FPGA and the theoretical analysis is conducted and demonstrates the effectiveness of the proposed method.

0引言

雷达恒虚警检测器的实际检测性能与其参考背景单元的分布有很大关系,当参考背景是均匀分布时,均值类CFAR具有较好的检测性能[1]。但是在多目标以及动态杂波环境下,CA-CFAR的检测性能会随干扰目标点的增加而迅速下降[2],而OS-CFAR具有较好的抗多目标干扰的能力,在均匀杂波背景和杂波边缘环境中的性能下降也是可以接受的[3]。

由于一维CFAR检测器的参考窗在同一维度上,即在距离维或多普勒维上,这样获取的背景信息比较单一,得出的检测门限精确度较差。因此,为了获取更多的背景信息,把一维参考窗扩展到二维,即同时选取距离维和多普勒维上的背景信息来做估计,这样,总体检测性能有更大的提高。

对于有序类CFAR的工程化实现[4],当前大多采用DSP来完成,即采用通用DSP芯片构造硬件处理平台来实现CFAR算法[5]。但对于实时性要求较高的窄脉冲雷达,由于系统采样率很高,数据吞吐量大,要求处理机硬件平台提供较高的运算速度和运算效率,FPGA以其较高的处理速度以及并行化能力成为实现OS类CFAR算法的一种选择[6]。

本文提出了一种基于FPGA的二维OS-CFAR高效实现方法,通过采用并行寻址解决FPGA实现中二维空间上参考单元寻址困难的问题,通过采用二元积累判决解决了排序运算计算量大、耗时长、实时性不高的问题,实现了检测处理的数据流水作业,提高了实时性,达到了实际应用的要求。

1二维OS-CFAR算法模型

二维OS-CFAR检测器的参考窗选取方式有多种形式,比较常见的有矩形窗,米字窗,十字窗等。参考窗的选取方式决定了FPGA的参考单元寻址模式,本文以十字参考窗为例,开展二维OS-CFAR算法基于FPGA的设计和实现,相关的结论可直接推广应用于其它参考窗。

1.1 基于排序算法实现OS-CFAR算法模型

传统二维OS-CFAR算法如图1所示,其中,D为检测单元,防止目标能量泄露到相邻参考单元而影响对杂波背景的估计,将与检测单元邻近的两个阴影部分作为保护单元,保护单元外侧为参考窗,设定前沿、后沿、上沿和下沿四个参考窗的长度均为16,保护单元数为2,杂波功率水平估计由这四个参考窗得出。

一般的计算步骤是先把这四个参考窗的数据取出,然后使用某种方法进行排序算法,选出第K个最小单元值X(K),再将其乘以门限系数T,得出判决门限。如果检测单元大于判决门限,则说明该单元是目标,否则该单元是杂波。

联系人: 刘中祥 E-mail: liuzhongxiang15@163.com

图1 传统二维OS-CFAR检测器方框图

OS-CFAR主要进行排序计算,找出排序后的第K个值。由于内部排序后数据原始的次序信息会丢失,不能满足数据流处理的要求,因此不能直接采用内部排序法,必须将数据复制并记住采样点X(n)的原始位置再进行排序处理,所以即使采用冒泡法等内部排序法,算法的空间复杂度仍是R+O(1)。此外,排序算法的时间复杂度也很高,并且很难并行处理。

1.2 基于二元积累实现二维OS-CFAR算法模型

由图1的算法模型可知,OS-CFAR的实质是将参考单元的数据进行排序,找出第K个杂波值X(k),将其乘以虚警门限系数T,得出杂波的均值估计Z,如果检测单元T大于Z,则说明该单元是目标,否则是杂波。

从另一个角度考虑这个检测问题,其过程等价于将参考单元所有值先乘以虚警门限系数T,然后将这些值和检测单元D进行比较,如果有K个值都小于检测单元D的值,说明检测单元D大于X(k) ·T,检测单元为目标,否则为杂波。此时,OS-CFAR算法就转换成检测单元D是否大于参考单元X(n)·T中K个任意值的问题,该问题恰好可以使用二元积累检测的思想解决。

基于二元积累检测实现二维OS-CFAR检测器的模型如图2所示。基本处理流程为:首先同时取出检测单元D周围的参考单元值X(n),将这些值乘以虚警门限系数T,然后将检测单元D与相乘之后的所有值X(n)·T进行比较,如果D大于X(n)·T,得出比较结果为1,否则为0。最后将所有比较结果进行相加,判断相加结果是否大于K,如果大于K,说明该检测单元为目标,否则为杂波。

图2 基于二元积累的二维OS-CFAR方框图

此种方法大大降低了OS-CFAR算法上的时间复杂度,可以进行并行检测,只用O(1)的时间实现算法。同时,该模型没有破坏原始数据的先后顺序,非常适合数据流运算。

2基于FPGA的设计与实现

二维OS-CFAR的FPGA设计与实现的关键点主要有两个方面:一方面是参考窗中所有参考单元的读取方法,在DSP中,通过控制存储地址可以将参考窗中的数值同时取出,而在FPGA中读取RAM中的值,一次只能读取一个地址上的值,由于参考窗中参考单元的数量较多,将参考窗中的值取出需要很多延迟,同时也不能保证数据流处理,实时性大大降低。本文通过使用移位寄存器组,根据参考单元的相对位置关系,实现了将参考窗中所有参考单元的值在一拍时间内取出,保证了数据流水处理。另一方面是参考单元排序算法,当参考窗选取数据较多时,排序的计算量很大,如果用DSP芯片实现,由于是串行处理,得出比较结果需要的时间比较长。本文利用FPGA并行处理的优势,运用二元积累的思想实现排序判决,同时设计数据流水化处理形式,提高了实时性。

2.1 参考单元读取设计

雷达回波经过AD采样、下变频、脉冲压缩和相参积累等预处理,得到二维距离-多普勒矩阵。在FPGA中,将距离-多普勒矩阵缓存在Block RAM中,以便于后续进行检测处理。本文以512×64大小的距离-多普勒矩阵为例研究参考单元读取的设计方法。设二维OS-CFAR检测器的保护单元选取为2个采样点,上下左右参考窗中,每个参考窗选取16个参考单元。检测数据从Block RAM中按照距离单元依次进入移位寄存器组,根据参考窗中参考单元相对位置的关系,则可同时从寄存器组中取出检测单元和参考单元。检测单元和参考单元的并行寻址设计如图3所示。

图3 参考单元并行寻址方框图

从如3看出,在同一个参考窗中相邻的上下参考单元时间差是64,即一个多普勒维上距离单元数。因为在同一距离维上,则相邻的左右参考单元时间差是1.所以,下窗参考单元从reg0开始,到reg960结束,每隔64个寄存器取一次数据(data_in、reg64、reg128…reg960);上窗参考单元从reg1344开始,到reg2304结束,每隔64个寄存器取一次数据(reg1344、reg1408…reg2304);检测单元为reg1152;右窗参考单元从寄存器reg1134到reg1149中得出,左窗参考单元从寄存器reg1155到reg1170中得出。

当寄存器reg1152中数据有效时,检测单元是距离-多普勒矩阵中第一个地址的数,检测器开始检测,此时使用下窗和右窗这两个窗的数据作为参考单元。同理,当检测单元位于距离-多普勒矩阵边角位置时,选取其中有效的两个或三个参考窗作为参考背景。而检测单元位于距离-多普勒矩阵中间位置时,即四个参考窗中数据都有效时,使用这四个窗作为参考背景。

这种设计依据参考单元相对位置的特性和FPGA寄存器资源多的优势来设计的,可以使检测单元和对应的所有参考单元的数值一起取出,同时进入检测器,达到流水作业和并行计算的效果,大大提高了时间效率。

2.2 OS-CFAR算法的流水化设计

本文基于二元积累思想实现了二维OS-CFAR算法模型,如图2所示,是一种基于FPGA的并行流水处理的实现方法,极大地提高了实时性。

以参考窗中有8个数据为例,阐述二维OS-CFAR检测雷达信号流水处理的设计。假定参考单元的值分别为2、10、8、6、12、9、15、3,检测单元值为26,虚警门限系数取2,把参考窗中排在第6小的参考单元作为比较单元,其流水处理实现恒虚警检测的设计思路如图4所示。

图4 OS-CFAR并行流水处理示意图

从图4可以看出,基于二元积累思想实现OS-CFAR算法,在FPGA芯片中并行流水处理数据,其结构主要由乘法器、比较器和加法器组成。整个检测过程经过4级流水后得出结果,在第3级数据流中得到二元积累数为7,说明检测单元大于由参考窗中排在第7小的参考单元(12)得出的参考门限,即26>12×2,所以该检测单元为目标,同时也证明基于二元积累算法实现OS-CFAR检测的正确性。如果参考窗中共有M个数据,也是经过4级流水得出结果,这种算法充分利用FPGA的并行计算的特点,大大较少了延迟周期,提高了检测的实时性。由示意图可以看出,资源利用也较少,仅需要M个乘法器、M个比较器、M个加法器和2M+1个寄存器。

3FPGA实现结果

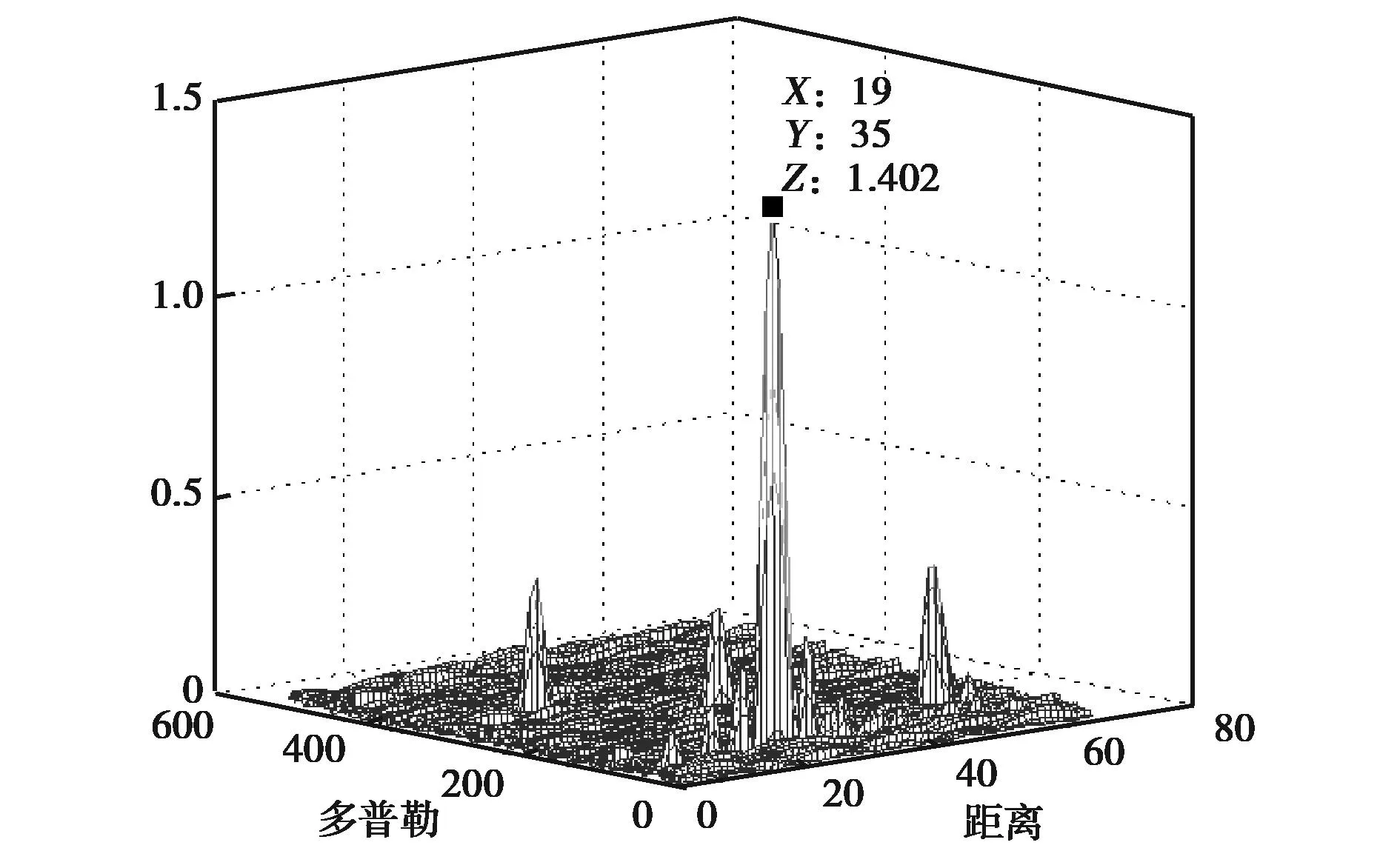

首先采用matlab模拟雷达回波信号,经过采样、下变频、速度补偿、脉冲压缩和相参积累等相关处理,得到512×64的二维距离-多普勒矩阵,如图5所示。从图5可以看出,目标位于距离维第19号单元,多普勒维第35号单元处,并且在目标周围有多个突起的杂波。

图5 R-D矩阵幅值分布

在Matlab中,采用十字参考窗OS-CFAR检测器,取虚警率为10-6,排序后第3/4个参考作为门限,其检测结果如图6所示。从图6可以看出,目标被有效检测出,而杂波干扰则没有被检测到,表明二维OS-CFAR检测器有较好的抗目标杂波干扰的能力。

图6 Matlab中二维OS-CFAR检测结果

在ISE14.7软件中,基于本文提出的二维OS-CFAR架构,编程VHDL代码,并将图5所示的距离-多普勒矩阵导入到FPGA的RAM-based Shift Register内部存储器中作为待检测信号,综合仿真结果如图7所示。由于RAM地址是从0开始,则图7检测到目标点的地址加1就是实际在距离-多普勒矩阵的位置,从图中可以看出,检测点位于多普勒维第35单元,距离维第19、20单元处,和在Matlab中理论仿真结果相同。同时,从仿真图也可以看出,基于FPGA的二维OS-CFAR检测器实现了流水作业,从而提高了检测的实时性。

图7 FPGA中二维OS-CFAR检测结果

4结束语

针对二维OS-CFAR基于FPGA实现在二维空间上参考单元寻址困难和基于DSP实现排序运算量大、耗时长和实时性不高的问题,本文基于二元积累思想,实现了二维OS-CFAR基于FPGA的设计与实现,根据二维CFAR检测器参考单元相对位置的特性,解决了二维参考单元寻址问题,并且能达到并行取值的效果。同时,解决了排序运算量大的问题,实现了检测流水作业的功能,提高了实时性,达到了工程实用的要求。

参考文献

[1]何友,关键,彭应宁.雷达自动检测与恒虚警处理[M].北京:清华大学出版社,1999.

[2]LONGO M,LOPS M. OS-CFAR thresholding in decentralized radar systems[C].//IEEE Transaction on Aerospace and Electronics Systems, 2006,32(4):1257-1267.

[3]ROHLING H. Radar CFAR thresholding in clutter and multiple target situations[J].IEEE Transaction on Aerospace and Electronics System, 1983,AES-19(4):608-620.

[4]郭鹏程,陈矛,罗丁利,等.基于FPGA的OS-CFAR设计与实现[J].火控雷达技术,2010,39(3):50-53.

[5]MAGAZ B, BENCHEIKH M L. An efficient FPGA implementation of the OS-CFAR processor[C].//International Radar Symposium, 2008.

[6]CUMPLIDO R,TORRES C.On the implementation of an efficient FPGA-based CFAR processor for target detection[C].//2004 1st International Conference on Electrical and Electronics Engineering,2004:214-218.

刘中祥(1989-),男,硕士,主要研究方向为雷达信息处理与目标识别技术。

宋志勇(1983-),男,讲师,主要研究方向为雷达信息处理与目标检测跟踪技术。

付强(1962-),男,教授,主要研究方向为精确制导自动目标识别。

Design and Implementation of Two-Dimensional

OS-CFAR Based on FPGA

LIU Zhongxiang,SONG Zhiyong,FU Qiang

(ATRLab,SchoolofElectronicScienceandEngineering,NationalUniversityof

DefenseTechnology,Changsha410073,China)

Key words: Two-dimensional OS-CFAR; FPGA; data flow; binary integration