参数灵活配置的通用雷达捷变频源设计

2016-01-10付钱华

付钱华,易 淼

(1.西华大学电气与电子信息学院,四川成都610039;2.电子科技大学信息与软件工程学院,四川成都610054;3.宜春学院物理科学与工程技术学院,江西宜春336000)

0 引言

在现代雷达应用中,由于工作空间和时间的限制,加之快速反应能力和系统综合性的要求,雷达必须具备多功能和综合应用的能力[1]。雷达及其目标模拟器系统的激励信号、各种定时信号和具有复杂调制波形的信号均由雷达系统的频率源来完成[2],所以频率源已成为雷达系统十分关键的技术之一,其是一种复杂的多功能组件。常见的方法[3-4]根据雷达的线性调频工作模式和捷变频参数等用途要求进行频率源定制,往往设计周期长、扩展性和移植性差。本文利用直接数字频率合成器(Direct Digital Synthesis,DDS)的高分辨率、捷变频、控制灵活、可调相调幅和线性调频等特点,通过合理的频率规划,利用现场可编程门阵列(Field Programmable Gate Array,FPGA)控制,一个DDS产生捷变频信号,一个DDS产生线性调频信号,与系统时钟有效混频,实现了一种跳频带宽在725~775MHz,能同时支持捷变频、点频和线性调频等模式的通用型参数可大范围小步进灵活配置的雷达通用频率源,可扩展成工作在不同频段的雷达上。

1 DDS结构原理及其输出频谱分析

1.1 DDS结构原理

DDS是从相位出发,由不同的相位给出不同的电压幅度,即相位到正弦幅度变换,最后滤波,平滑输出所需要的频率。典型的DDS结构框图如图1所示。

图1 DDS结构框图

DDS是一个开环无反馈系统,具有极短的频率切换时间。其工作实质就是在每个系统周期Δt=1/fs下,输出相位增量Δϕ=K·(2π/2N),则输出信号频率为

式中,K为频率控制字,N为相位累加器的位数。从式(1)可以看出,DDS的输出频率最小为系统时钟的1/2N,具有极高的频率分辨率。根据奈奎斯特定理,DDS的输出频率范围[5]一般是0~0.4fs,所以输出频率相对带宽很宽,但工作频带受限。

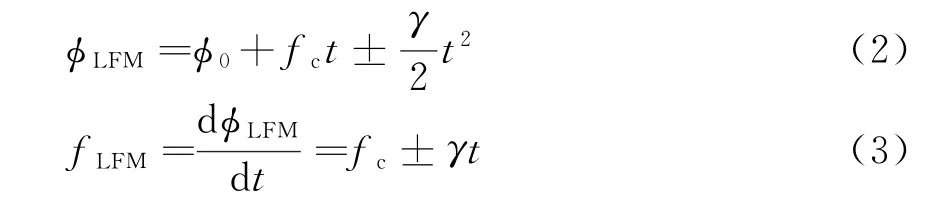

DDS利用两个累加器(频率和相位累加器)构成的线性调频发生器能够产生高速二次时基信号:

通过改变频率累加器的调频斜率γ进行频率调制,改变相位累加器的初始相位φ0进行相位调制,控制加在相位幅度变换器和D/A变换器之间的乘法器乘数因子A进行幅度调制。

1.2 DDS输出频谱分析

根据式(1),DDS相当于一个分频器。故从理论上讲,DDS输出信号相位噪声为

式中,L fs为输入系统时钟的相噪。由于其他因素的影响,故DDS实际上输出相噪会比理论略差一点。

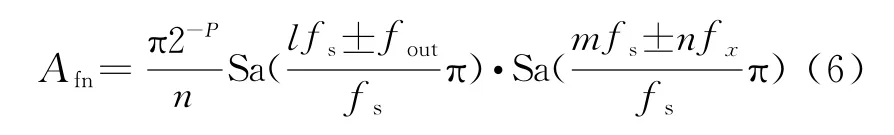

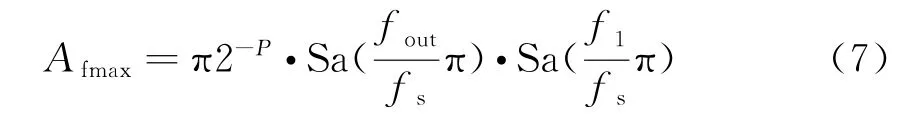

实际的DDS通常取较大的相位累加器位数N值以获得极高的频率分辨率,而仅用高P位来寻址正弦查找表ROM,舍去了低B位,这样便引入了相位截断误差。由相位截断引入的杂散分量位于:

对应的幅度为

式中,t=l+m,l∈(-∞,∞),m∈(-∞,∞),n∈[1,∞),f x=〈K〉2B·fs/2B。幅度最强的杂散位于处,其幅度为

所以相位截断时DDS的无杂散动态范围[6]为

就现有技术而言,不可能制作任意分辨率的DAC,往往在正弦查找表ROM中存储的波形样点的幅度编码由有限位二进制数表示,这样就引入了幅度量化误差。其信噪比为

式中,W为DAC的量化位数。这就说明W越大,幅度量化的信噪比越高,其对应杂散就越低。

DAC的非线性主要由制造方面的不精确和环境的影响,包括差分非线性和积分非线性等。其引起的杂散位置为

而杂散电平由DAC的性能决定。

综上分析,DDS输出信号具有良好的相噪特性,但杂散谱线较多。主要来源有相位截断效应、幅度量化误差和DAC的非线性。从式(8)~(10)可以看出,只要合理地选择DDS输出频率及其器件型号(包括DAC的位数和性能),即可使得输出频谱指标满足系统设计需求。

2 通用捷变频源设计与实现

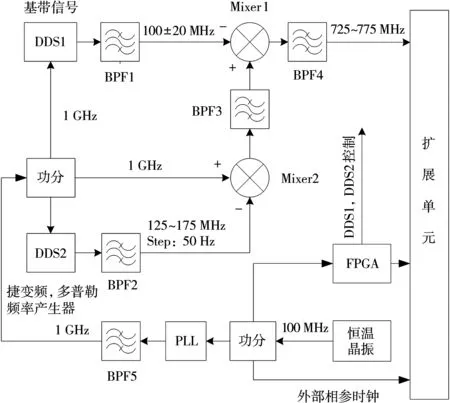

根据前文的分析,DDS虽然具有很多优势,但也固有一些局限性。本文通过采用具有良好频谱纯度的100MHz恒温晶振作为DDS系统时钟电路的参考信号,将系统时钟与捷变信号混频产生捷变的本振信号825~875MHz,克服DDS输出频率不高的瓶颈。最后将线性调频基带信号调制到高频信号725~775MHz。具体方案框图如图2所示。通过这种变频的方式有利于DDS选择具有良好频谱特性的输出频段,也有利于将线性调频信号扩展到高频频段,通过高速FPGA控制,使得能够同时产生捷变的线性调频的信号,整个系统采用单一晶振,并预留了扩展外部相参时钟,保证了系统的相参性。

2.1 设计方案选择

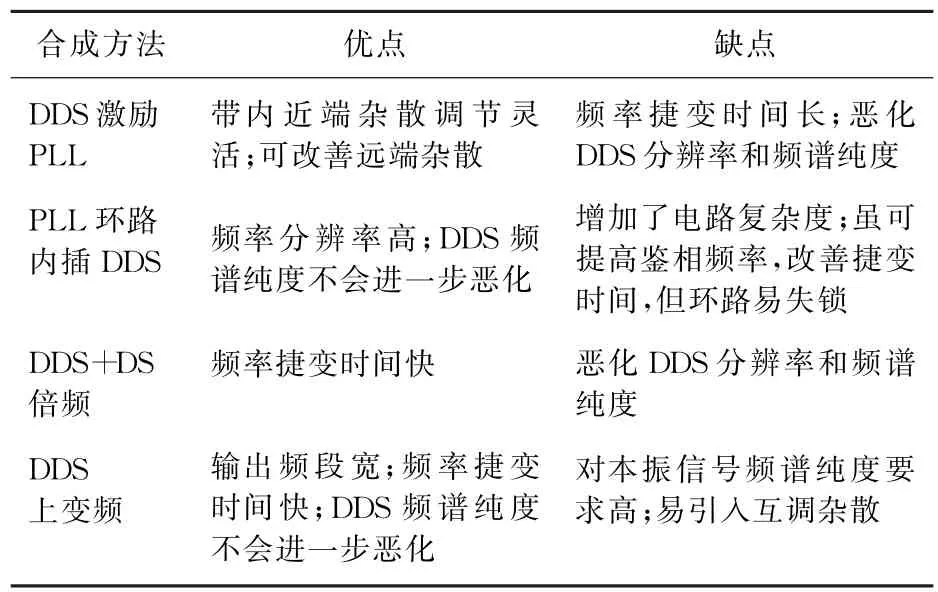

文献[7]给出了宽带微波雷达信号的合成方法主要有DDS激励锁相环(Phase-Locked Loop,PLL)方法、PLL环路内插DDS方法、DDS+DS直接倍频方法和DDS上变频方法。表1为这4种常用基于DDS的雷达波形合成技术的性能对比。

图2 通用捷变频源方案框图

表1 基于DDS的雷达波形合成技术对比

根据理论分析和工程经验,锁相环的锁定时间至少在微秒量级。若采用表1中的DDS激励PLL,PLL均会恶化DDS的频率捷变时间,使得指标无法达到系统要求。而对DDS输出倍频时若倍频次数太高,恶化相位噪声和杂散指标越严重,所以在低频段尽量避免倍频。综合考虑实现的复杂度,故采用DDS上变频的方案实现低频段通用捷变频源方案[8]。

2.2 器件选型和关键电路设计

从图2可以看出,通用捷变频源主要由恒温晶振、PLL、基带扫频DDS、捷变跳频DDS、混频器、带通滤波器、FPGA控制接口和扩展单元等组成。

恒温晶振采用NV45G1480,输出频率100MHz,经过实测相噪为-152 dBc/Hz@1 k Hz,在中心频率偏移±20MHz范围内杂散低于-130 d Bc,作为DDS系统时钟的参考时基,FPGA的时钟和外部相参时钟。

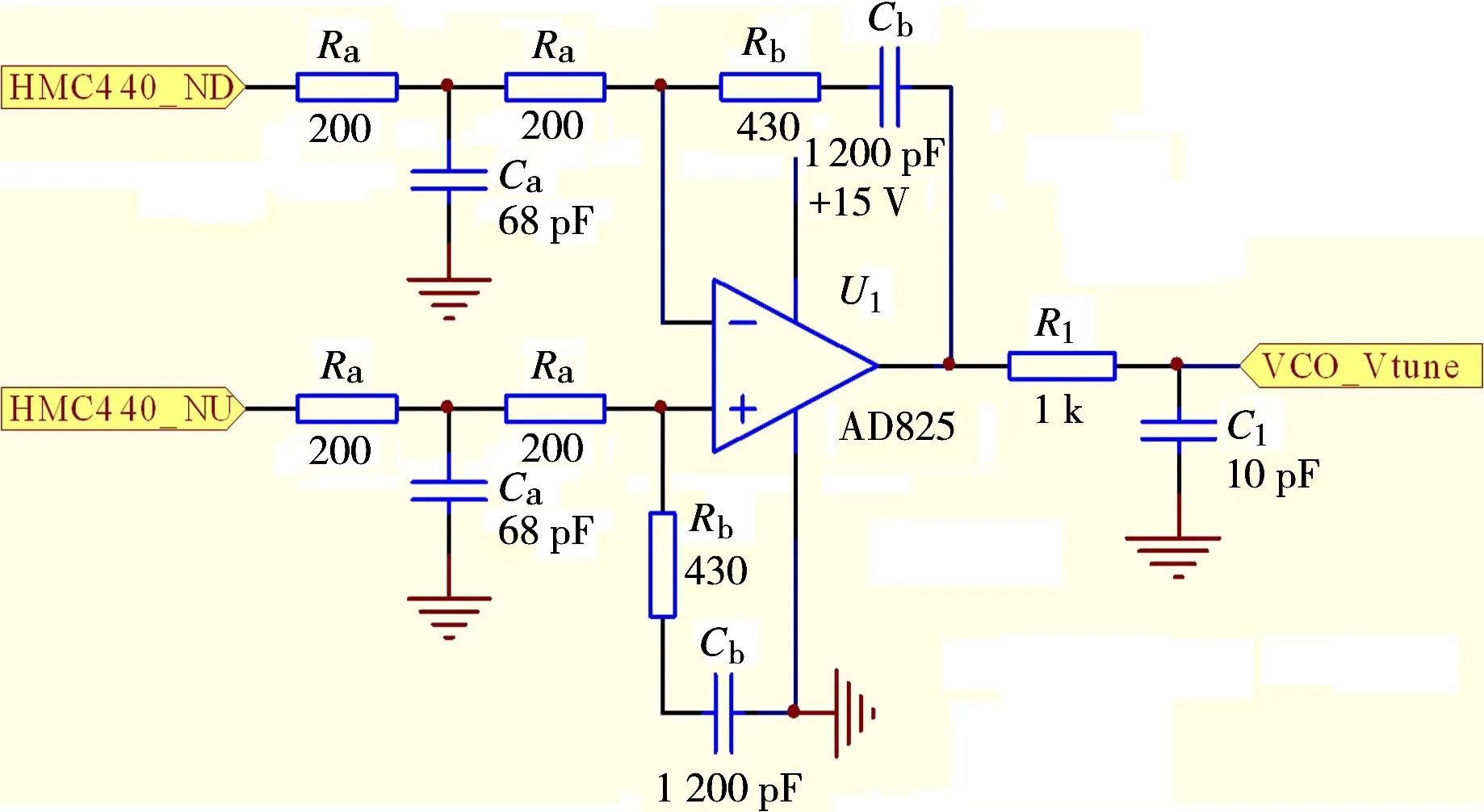

DDS系统时钟产生有两种方法,一种是利用梳状谱发生器产生100MHz信号的谐波信号,再由带通滤波器抑制无用的谐波信号,选择出系统时钟。但采用这种方法体积过大,故采用第二种方法,就是间接锁相式频率合成方法。采用的PLL芯片为HITTITE公司的整数分频锁相环芯片HMC440,该芯片拥有一个数字鉴相器和一个分频比为2~32的分频器,其噪底在输入参考频率100MHz时为-153 dBc/Hz@10 k Hz,接近于100MHz晶振相位噪声,所以其非常适合于宽环路带宽和低环路分频比的频率合成器。环路滤波器采用低成本、通用高速结型场效应管放大器AD825,构成的环路滤波器如图3所示。压控振荡器(VCO)采用UMC公司的UMS-2150-R16,输出功率一般为12 dBm,单边带相位噪声-75 dBc/Hz@1 k Hz。

图3 PLL环路滤波器结构

捷变跳频DDS采用具有并口配置的AD9858,其频率调整字的变化到DAC输出信号的变化仅需要83个系统时钟周期,频率分辨率达到0.233 Hz。其外围电路如图4所示。

图4 捷变跳频DDS外围电路图

基带扫频DDS采用AD9910,其内置了14位的DAC,有利于降低幅度量化杂散。可支持频率、相位和幅度调制的多种组合,既可实现线性调频又可实现非线性调频,非常有利于产生各种雷达波形和进一步的扩展。

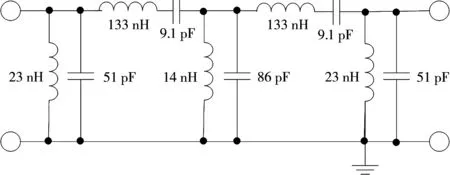

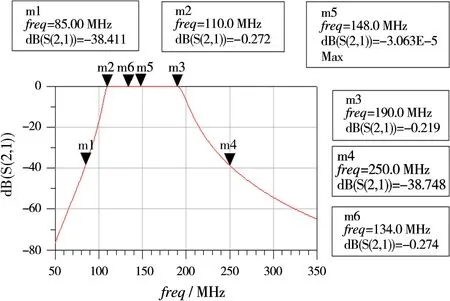

为了有效地抑制DDS输出信号远端杂散和混频器等的非线性带来的交调杂散,可以在DDS输出端增加一个带通滤波器。125~175MHz带通滤波器电路及其S21参数仿真图如图5和图6所示。

图5 125~175MHz带通滤波器电路图

图6 125~175MHz S21参数仿真图

2.3 关键指标和性能分析

DDS输出信号频率低于其系统时钟的1/8,故DDS的输出信号相位噪声(-140 d Bc/Hz@1 k Hz)远优于系统时钟1 GHz的相位噪声,故整个通用捷变频源的相位噪声主要取决于1 GHz锁相环。而1 GHz PLL经过实测,输出信号相位可以达到-121 d Bc/Hz@1 k Hz。

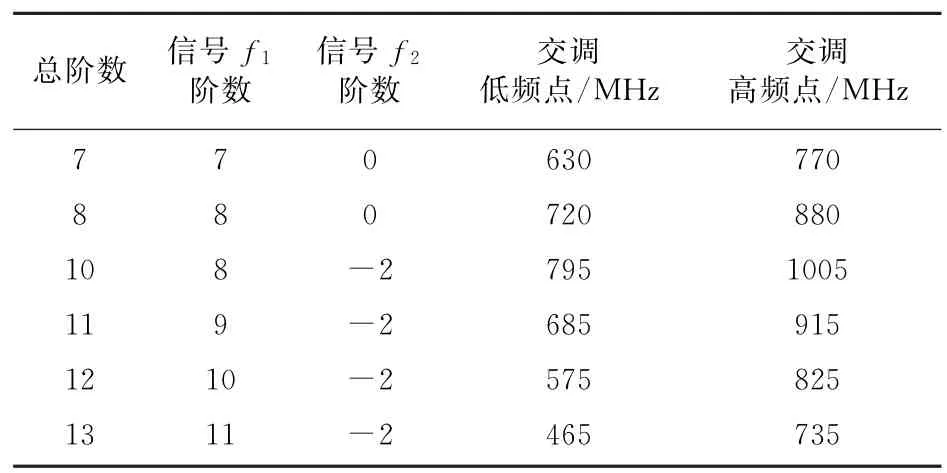

AD9858和AD9910分别在选择的输出频段范围内的宽带无杂散动态范围为63 d Bc和67 dBc,为保证整个系统的输出杂散优于60 dBc,则要求混频器不允许低阶交调落入通频带或者过渡带。混频器1和2的交调频点计算如表2和表3所示。从表中可以看出,通过合理的频率规划,落入通频带和过渡带的交调阶数均在五阶以上,通过硬件的调试可以确保杂散指标满足系统要求,有效地避免两个DDS输出频点相互干扰的问题。

表2 混频器1(f1=80~120MHz,f2=825~875MHz)的交调计算

表3 混频器2(f1=125~175MHz,f2=1 GHz)的交调计算

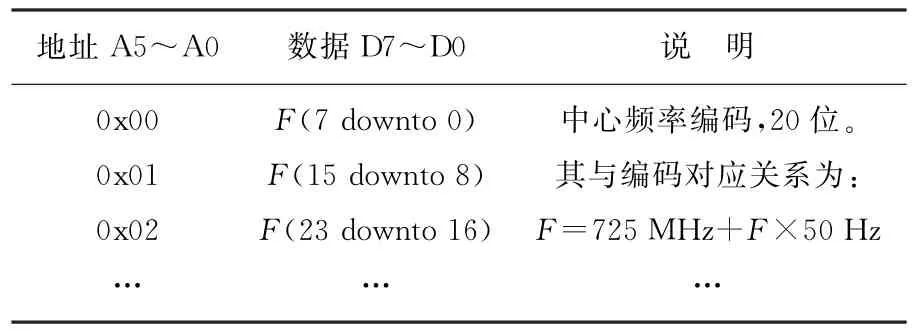

2.4 控制接口设计

由于该通用捷变频率源覆盖的模式众多,跳频点数就达100万个,还有不同时间和带宽的线性调频组合,故其接口电路需要对命令字按地址进行编码。以跳频中心频点为例进行说明,首先跳频命令字就至少需要20位数据进行区分这106个跳频点。为节省数据接口线位数,可以每次送8位数据给高速FPGA进行锁存,这样就需要送3次数据,通过命令字地址进行区分。接口指令编码格式如表4所示。

表4 接口指令编码表

若后面的扩展单元利用点频源扩展了工作频带,则中心频率控制字的高4位可以用来控制点频源,整个系统就可扩展到工作带宽为50MHz的16倍(即800MHz)。

高速FPGA在接收完成对应的指令字后进行运算转换得出DDS的频率调整字、数字斜坡限制、数字斜坡步长、数字斜坡速率等,然后通过串口(AD9910)或者并口(AD9858)对DDS编程控制。

2.5 系统扩展方案

通过开关切换的方法选择点频源可以让通用捷变频源扩展到更高的不同频段和更宽的工作频带。图7为一种毫米波雷达频率源扩展方案,首先通过频标发射器1和混频器1将工作频带扩展到100MHz,然后通过二次变频和倍频可以将工作频带扩展到几个GHz。

图7 毫米波雷达频率源扩展方案

3 通用捷变频源实测结果

采用罗德与施瓦茨公司的信号源分析仪FSUP对通用捷变频源的相位噪声杂散、线性调频和跳频时间的部分测试图如图8~10所示。

经过实测,系统输出的各频点相位噪声优于-115 d Bc/Hz@1 k Hz,典型的杂散值优于-70 d Bc,输出频率在775MHz附近最差,但也优于-63 d Bc。线性调频时间和带宽可按照4 ns和5 Hz步进在4~4 000μs和100 k Hz~40MHz范围内任意设置。跳频和多普勒频移分辨率为1 Hz,捷变调频时间达到886 ns。

图8 带内相噪杂散实测结果

图9 线性调频信号时频域实测结果

图10 跳频时间实测结果

4 结束语

设计通用型雷达频率源,不仅需要兼顾各种雷达工作的模式和产生不同斜率的调频信号波形,还需要考虑其是否易扩展性,输出的信号频谱指标有足够的裕量进行扩展,这对方案的选择和频率规划提出了更高的要求。本文首先通过分析DDS的内部结构和输出频谱特性,对比了4种方案,结合目前器件工艺水平,设计的通用型雷达捷变频源指标经过实测,符合系统设计要求,为快速研制各类型和频段的雷达频率源提供了重要的参考价值。

[1]向敬成,张明友.雷达系统[M].北京:电子工业出版社,2001:2.

[2]张鑫,李彩华,黄仰博,等.基于混合时钟三阶DDS的信号多普勒模拟方法[J].国防科技大学学报,2014:36(2):134-139.

[3]XU Xin,TANG Xiaohong,WU Tao.A DDS-Based C-Band Wideband Agile Frequency Synthesizer[C]∥2013 International Workshop on Microwave and Millimeter Wave Circuits and System Technology,Chengdu:IEEE,2013:324-327.

[4]CUI Weibo,ZHANG Xiao,LU Xiao,et al.The Design of High Performance X-Band Frequency Synthesizer Based on DDS and PLL[C]∥2013 Cross Strait Quad-Regional Radio Science and Wireless Technology Conference,Chengdu:IEEE,2013:97-100.

[5]MA Haihong,TANG Xiaohong.Design of 3 mm Band Hopping Frequency Synthesizer[J].International Journal of Infrared and Millimeter Waves,2008,29(7):704-711.

[6]胡仕兵,汪学刚,姒强.直接数字频率合成技术杂散信号频谱性能分析[J].电路与系统学报,2009,14(5):87-91.

[7]费元春,苏广川,米红,等.宽带雷达信号产生技术[M].北京:国防工业出版社,2002:1-49,63-95.

[8]陈菡,谭剑美.DDS线性调频信号时钟抖动误差分析[J].雷达科学与技术,2012,10(3):328-331.CHEN Han,TAN Jianmei.Analysis of Clock Jitter Error in LFM Waveforms Based on DDS[J].Radar Science and Technology,2012,10(3):328-331.(in Chinese)