基于VHDL的乘法器的设计与对比

2015-12-16赵杰

赵杰

(商洛学院电子信息与电气工程学院,陕西商洛726000)

基于VHDL的乘法器的设计与对比

赵杰

(商洛学院电子信息与电气工程学院,陕西商洛726000)

在数字系统中,乘法器是进行数字信号运算的核心运算单元,同时也是微处理器中进行数据处理的关键部分。以8位乘法器为例,根据简单并行乘法器、加法器树乘法器和移位相加乘法器的基本原理,利用VHDL分别进行描述和实现。对三种乘法器分别通过QuartusⅡ软件平台进行仿真,再做进一步比较和讨论。结果表明,三种乘法器在运行速度和资源占用上各有利弊,实践中可根据设计要求和硬件条件选择使用。

乘法器;移位相加;加法器树;仿真

乘法器在数字信号处理过程中发挥着重要的作用,在语音、图像处理、通信等领域中扮演着举足轻重的角色,它的运算速度与信号处理和整体效率的性能直接相关,并且在很大程度上左右着系统功能[1-3]。基于FPGA/CPLD的EDA技术在现在数字系统中的应用越来越广泛[4-7],利用硬件描述语言设计乘法器是其重要任务之一。VHDL具有复杂的程序架构和超强的表述能力,因此它可以对模块较大的分层,再针对已有的设计进行重复再利用。VHDL语法严格、语言标准、规范、有利于沟通和反复利用[8-10]。由于每种乘法器在资源占用和运算速度上的不同,使得用户在使用乘法器时需要进行选择。本文以8位位宽的乘法器为例,通过对比几种用VHDL描述的常见乘法器在运算速度和占用资源等方面的不同,为使用者在选择时提供一定的参考。

1 简单并行乘法器

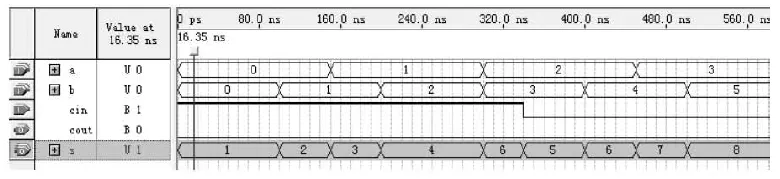

简单并行乘法器有两个输入端口a和b,一个输出product,进行直接乘法运算。本文介绍的是一个纯组合逻辑电路,不需要时钟信号。其仿真波形如图1所示。

2 移位相加乘法器

当两个8位数做乘法运算时,一共需实现8次加法运算和8次移位运算。根据乘数末位的值来判断被乘数是否与原来的部分积相加,运算从乘数的最低位开始,如果乘数=1,则需要加上被乘数右移一位,然后形成新的部分积,同时把乘数右移一位;如果乘数=0,则需要加上零值后右移一位,然后形成新的部分积,同时将乘数右移一位,等到运算到乘数的最高位结束,得到最终的乘积结果。

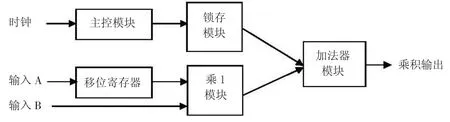

为方便实现,将8位移位相加乘法器分为五个功能模块,如图2所示。

图1 简单并行乘法器仿真结果

图2 8位移位相加乘法器原理框图

每个模块分别用VHDL描述,而顶层设计实体则用元件例化方式来完成。

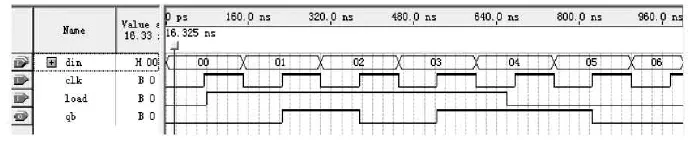

主控模块:根据输入时钟控制各模块运行。其仿真波形如图3所示。

锁存器:在时钟信号的作用下,移位锁存输入的值。其仿真波形如图4所示。

图4 锁存器模块仿真图

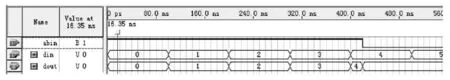

移位寄存器:将乘法运算中的被乘数加载于移位寄存器当中,在同一时间进行乘法的移位操作运算。其仿真波形如图5所示。

乘1模块:实现8位与1位的乘法运算。其仿真波形如图6所示。

加法器模块:进行操作数的加法运算。其仿真波形如图7所示,顶层设计仿真结果如图8所示。

图5 移位寄存器模块仿真图

图6 乘法器仿真图

图7 8位加法器仿真图

图8 8位移位相加乘法器仿真图

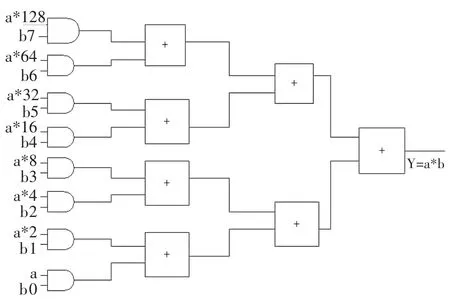

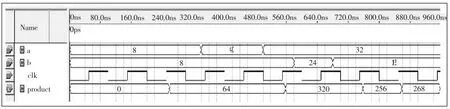

3 加法器树乘法器

移位相加乘法器所需的硬件资源较少,但是运行速度较慢。相比较于移位相加乘法器,加法器树乘法器运算速度较快。它使用的加法器数目等于操作数位数减1,加法器精度为操作数位数的2倍,需要的与门数等于操作数的平方。因此8位移位相加乘法器需要7个16位加法器和64个与门。加法器树乘法器的原理如图9所示、仿真结果如图10所示。

图9 加法器树乘法器原理示意图

4 综合比较

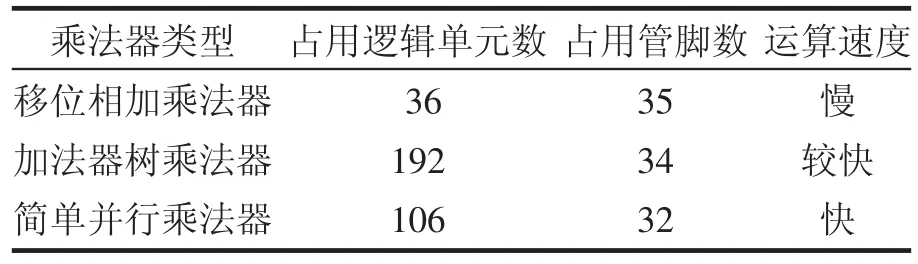

本次设计中三个乘法器在建立工程时均选用Altera公司生产的EP1C6Q240C8芯片,比较三个不同乘法器在占用逻辑单元,占用管脚和运算速度上的不同,结果如表1所示。简单的并行乘法器运算速度快,实现代码简单明了。移位相加乘法器所耗资源相对较少但运算速度比较慢,加法器树乘法器汲取了移位相加与简单并行乘法器的优点,运算速度快,但是却增加了芯片资源耗用。

图10 加法器树仿真结果

表1 乘法器比较

5 结语

乘法器是现代数字系统中的重要逻辑器件,在很多应用中都会出现,例如低通滤波器的设计、大概率的运算等。本设计主要介绍三种乘法器,其中移位相加乘法器和加法器树乘法器由八位加法器构成,并按照时序逻辑的方式设计完成,简单的并行乘法器运用乘法运算符实现,通过比较三种的运算速度,占用资源不同得出在工程实践中如何选择相应的乘法器。随着人类生活水平的提高和科研生产对运算速度要求的提升,人们也在追求性能高度集中的多功能乘法器。例如:在最新研究的处理器中乘法器除了直接作为运算部件之外,还具有加速地址转换、数组寻址和执行其他整数操作等功能。

[1]朱霞,柴志雷,须文波.基于FPGA的数字滤波器乘法模块改进[J].计算机仿真,2009,26(1):335-338.

[2]任思颖.JPEG2000中5/3离散小波多层变换FPGA实现研究[J].现代电子技术,2011,34(12):75-77.

[3]温锋,李锦明.基于FPGA的激光陀螺信号高速解调滤波设计[J].电子技术应用,2014,40(1):90-92.

[4]蒋昊,李哲英.基于多种EDA工具的FPGA设计流程[J].微计算机信息,2007,23(32):201-203.

[5]闫春娟,陈琦.面向数字通信系统的EDA实验教学改革与实践[J].微计算机应用,2011,32(4):66-70.

[6]赵辉.基于EDA技术的数字系统设计[J].电子设计工程,2012,20(2):34-37.

[7]魏娜,王慧莹.EDA技术在电子设计中的应用[J].黑龙江科学,2014,5(3):267.

[8]谭会生,张昌凡.EDA技术及应用[M].3版.西安:西安电子科技大学出版社,2011:112-114.

[9]齐京礼,宋毅芳,陈建泗.VHDL语言在FPGA中的应用[J].微计算机信息,2006,22(35):149-151.

[10]王彩凤,李卫兵,卞丽.VHDL语言在电子设计中的应用[J].实验科学与技术,2014,12(4):65-67.

(责任编辑:李堆淑)

Design and Comparison of Multiplier Based on VHDL

ZHAO Jie

(CollegeofElectronic Informationand ElectricalEngineering,ShangluoUniversity,Shangluo 726000,Shaanxi)

Multiplier is the core of digital signal calculation.It is also the key component of data processing and microprocessor.8-bits multiplier is taken as the example.The simple parallel multiplier,the shift summation multiplier and the addition tree multiplier were introduced.They were described using VHDL.The three kinds of multipliers are simulated respectively through the Quartus II platform.Their simulation results were given.At the end of paper,the three multipliers were compared and discussed in the resource occupancy and operation speed.

multiplier;shift summation;addition tree;simulation

TP332.22

A

1674-0033(2015)06-0003-04

10.13440/j.slxy.1674-0033.2015.06.001

2015-10-12

商洛学院教育教学改革研究项目(13JYJX139)

赵杰,男,陕西汉中人,硕士,讲师