通用加法器的逻辑实现与分析

2018-01-26武汉市第二中学叶浩然

武汉市第二中学 叶浩然

1.介绍

通用加法器是计算机逻辑的基本元件,是计算机运算的基础:通过加法运算可以实现计算机大规模复杂运算。所以通用加法器的设计是计算机逻辑基础的重要内容。

本论文给出了通用加法器的实现方式,主要贡献包括以下三个方面:(1)给出了1、2、4、8比特加法器的电路实现并分析了其电路复杂性;(2)给出了从n比特加法器到2n比特加法器的迭代实现方式并给出了通用模型;(3)给出了2n比特加法器的通用实现方式并分析了其电路复杂性。

2.通用加法器实现

本章主要介绍用与、或、非和异或等四个基本逻辑单元设计通用加法器的逻辑实现方法,主要包括(1)1、2、4、8比特加法器的实现方法;(2)用n比特加法器实现2n比特加法器的通用方法;(3)2n比特加法器的实现方法。

2.1 1比特加法器

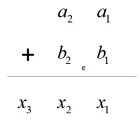

1比特加法器是通用加法器的基础,我们首先介绍1比特加法器的逻辑实现。设两个输入比特为a1和b1,则输出位2比特的真值表如下:

a1 b1 x2 x1 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0

由表可得其逻辑实现如下:

由逻辑实现可得,1比特加法器需要1个与门和1个异或门。

2.2 2比特加法器

可将2比特加法器拆分为两个1比特加法器,a1b1和a2b2。其实现

如下图所示:

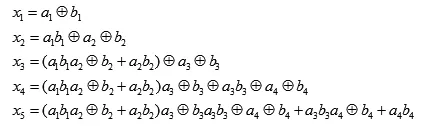

其中图中的e表示低位加法产生的进位。因为a2b2加法器所得结果为高位和低位,不影响低位结果,所以不变。而a1b1加法器所得的进位值与a2b2加法器的结果相组合,可以得到一个2比特与1比特相加的加法器。由此可得2比特加法器公式:

由逻辑实现可得,2比特加法器需要4个与门,1个或门,4个异或门。

2.3 4比特加法器

同理可将4比特加法器拆分为两个2比特加法器,将较小加法器进位与较大加法器组成一个新的加法器,求得结果即4比特加法器公式,其实现逻辑如下图所示:

由逻辑实现可得,4比特加法器需要18个与门,5个或门,16个异或门。

2.4 8比特加法器

由逻辑实现可得,8比特加法器需要28个与门,6个或门,20个异或门。

2.5 2n比特加法器

由逻辑实现可得,2n比特加法器需要28·3n-3个与门,6·3n-3个或门,20·3n-3个异或门。

3.结论

本文分析研究了通用加法器的设计方式,实现了2n比特加法器逻辑实现方式并分析了逻辑实现所需要的逻辑门。