PEM/OBIRCH 用于集成电路漏电流失效定位

2015-11-28陈选龙刘丽媛蔡金宝

陈选龙,陈 航,刘丽媛,蔡金宝

(工业和信息化部电子第五研究所 分析中心,广州 510610)

0 引言

漏电流增大是集成电路失效的主要电学表现形式之一。不同电路的失效会产生各种各样的漏电流表现模式,这是因为失效点本身可以产生漏电流,与失效点相连的电路也可以产生电流。由于集成电路结构和工艺的复杂性,引起集成电路漏电流增大的原因有很多,见表1[1-2]。在失效样品中,PN结击穿、氧化层击穿的失效仍占据较高的比例。

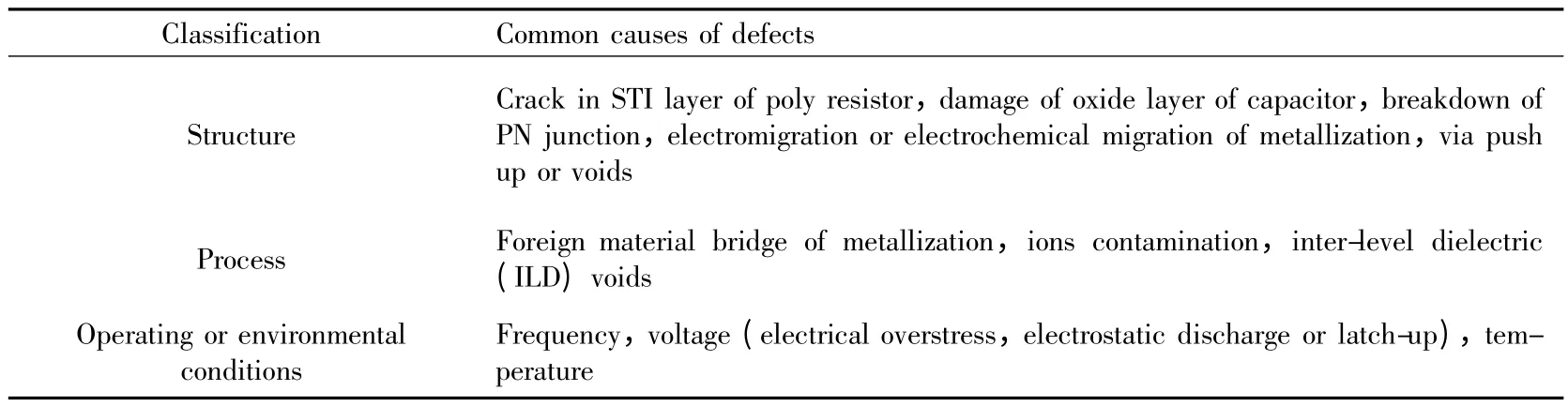

表1 集成电路漏电流增大失效原因Table 1 Failure causes for increasing leakage current of IC

光发射显微镜(Photon Emission Microscopy,PEM)[3]和光束感生电阻变化(Optical Beam Induced Current Changed,OBIRCH)技术是用于漏电流失效定位的两种主要方法。两者在漏电流缺陷特征的失效定位上有相似的也有明显的不同,既互通又互补。有些缺陷只能使用一种定位方法,而有些缺陷必须结合使用两种定位方法。例如,OBIRCH 仅用于大部分阻性互连缺陷分析,阻性缺陷一般不会产生光发射,则无法用PEM 捕捉发光缺陷点;PEM 检测结区或者载流子跃迁发光,结区发光包含的意义有多种,OBIRCH 则无法探测。实际上,集成电路除了金属化互连缺陷外,最为主要的缺陷就是PN 结异常。因此,由于两种方法侧重不同,对不同集成电路漏电流失效需要采用不同方法定位,需要尝试两种方法来分析。本研究采用PEM、OBIRCH 技术对集成电路漏电流增大失效进行失效定位,通过对失效分析案例的研究,提出几种失效分析技巧。

1 失效定位原理与方法

集成电路有源区导电时,结区载流子跃迁形成光发射,辐射特定波长的光子,光谱包括可见光到近红外光。跃迁有两种形式:电子-空穴对的再复合和场加速载流子辐射。第一种机理主要存在于正偏PN 结、饱和态的双极型晶体管(例如闩锁状态),产生的光波长约为1 100 nm。第二种机理主要存在于反偏PN 结、饱和态的金属-氧化物-半导体晶体管(热载流子效应)和栅氧化层缺陷,产生的光波长范围为400~1 900 nm[4]。光子需要经PEM 的硅探测器或者InGaAs 探测器接收成像,2 种探测波长范围分别集中于400~1 100 nm、900~1 600 nm。随着电压和漏电流的降低,集成电路的缺陷点主要辐射近红外光。因此,较高探测效率且探测波长集中于近红外光的InGaAs 探测器显得更为重要。根据集成电路的发光机理,可以确定PEM 中光发射的区域可能是直接失效位置(一般光发射不均匀),也可能是由于失效导致偏置异常引起的间接发光(结区发光均匀);这就要结合版图分析以及光发射的形貌来进行判断[5],必要时还需要用聚焦离子束对电路进行切割、微探针进行电测来确定[1]。

OBIRCH 近年来成为主要的集成电路漏电失效定位手段,特别是对于阻性缺陷造成的漏电,定位到的往往是原始缺陷[6]。OBIRCH 需要外部激励来产生信号,除了电应力外,还需要激光热激发或者光激发。漏电点在外部直流偏置下产生一定电流,1 340 nm 或者1 064 nm 的激光会逐个像素点地对集成电路进行加热,热量改变漏电回路的电阻特性,导致源端电流发生变化,进而探测到漏电回路或者漏电点。根据PEM 和OBIRCH 中的红外光能够部分穿透硅材料的特点,可以无损地从正面和背面对样品进行失效定位[7-8]。对于多层布线和倒装芯片封装的样品,背面光发射或OBIRCH 都是很好的定位方法,但对于重掺杂和非倒装芯片,需经过背面减薄、抛光等方法制样后方能进行成像定位。

2 试验结果与讨论

以下试验均是在工业和信息化部电子元器件失效分析中心完成,包括PN 结初始漏电位置定位、氧化层漏电定位、PEM 间接发光定位、芯片背面定位和金属桥连定位。采用DCG systems 公司同时装载PEM 和OBIRCH 技术的Trivision 激光扫描显微镜进行漏电流失效定位,主要配备In-GaAs 探测器、1 340 nm 激光源和1 064 nm 激光源。

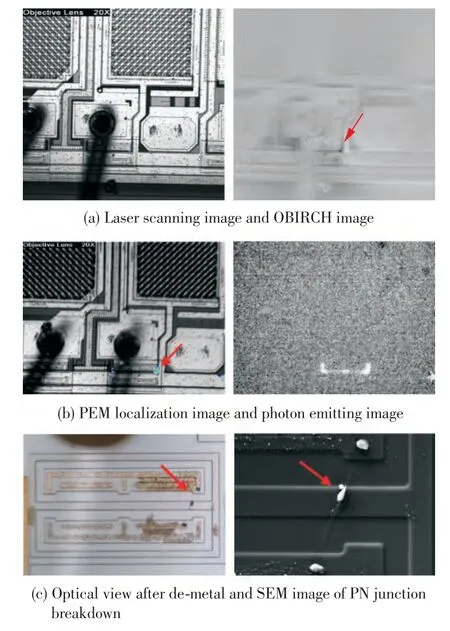

2.1 PN 结初始漏电位置定位

集成电路硅表面主要由PN 结构成,存在于主要结构如二极管、三极管、扩散电阻中。图1 失效电路PN 结为集成电路端口保护网络,结压在大于0.5 V 以后出现漏电,开封后芯片表面无法观察到明显的损伤。由于漏电并不是直接的阻性特性,采用PEM 和OBIRCH 结合的方式对漏电位置进行分析。分别对信号端加电0.6 V/200 μA 偏置进行OBIRCH 定位、施加0.7 V/650 μA 偏置进行PEM 定位。OBIRCH 定位的特点是精确定位到原始的漏电位置,并且能检测电流路径和铝空洞(图1a)。PEM 发光点不均匀(图1b),很可能是一个漏电缺陷点。经过去层处理,在扫描电镜下放大观察,可见PN 结存在击穿和局部开裂(图1c)。

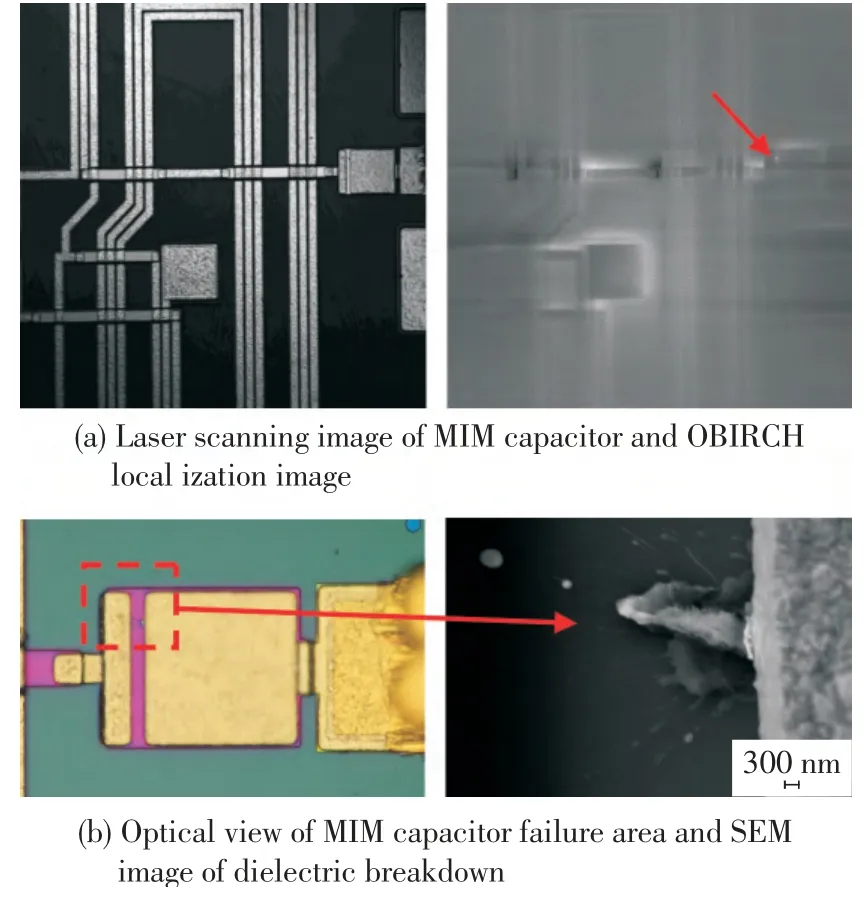

2.2 氧化层漏电定位

单片微波集成电路工作于射频波段,一般不设计ESD 保护电路,内部的电容氧化层就容易受到破坏,为静电敏感器件。然而,因氧化层金属电极阻档,无法直接观察确定漏电位置,也会因金属阻挡光发射而无法进行PEM 定位,一般采用OBIRCH 技术。混频器电路双中频正交输出端的功率不相等、镜频抑制能力失效,经测试,RF 输入端口的金属-绝缘层-金属(MIM)电容绝缘性下降,经OBIRCH 定位,失效点位于电容边缘(图2a)。在扫描电镜下可以清晰地看到电容边缘介质区域已经击穿(图2b)。

图1 PEM/OBIRCH 应用于PN 结失效定位Fig.1 Fault localization of PN junction using PEM/OBIRCH

图2 OBIRCH 应用于氧化层失效定位Fig.2 Fault localization of oxide using OBIRCH

2.3 PEM 间接发光定位

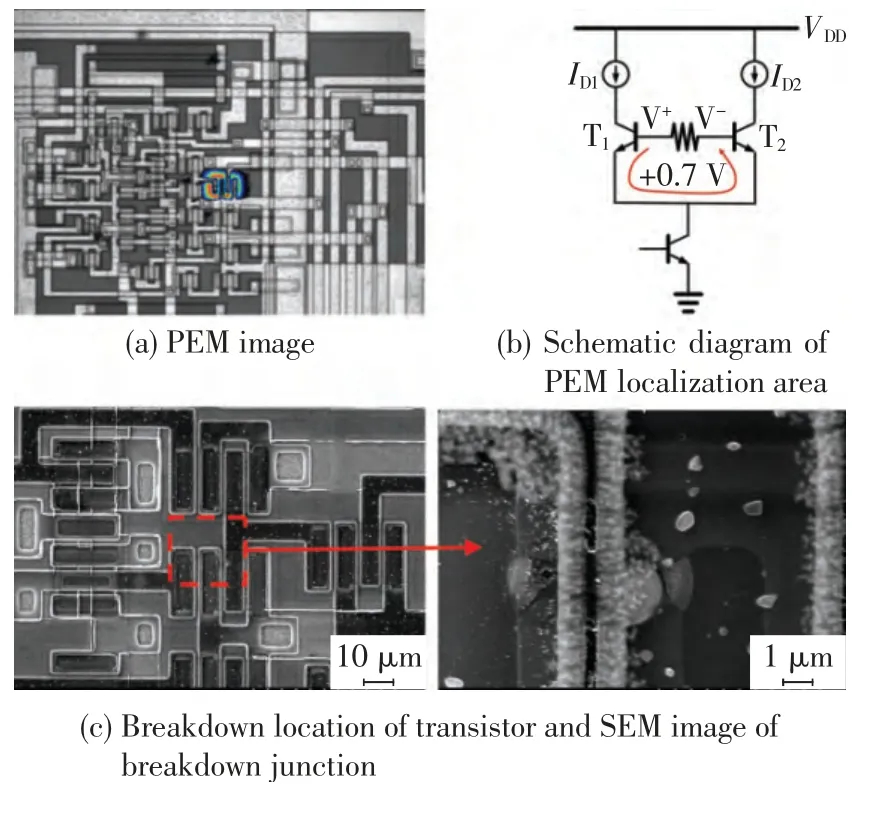

存在PEM 间接发光的缺陷是比较难定位的,主要是因为产生光发射的区域并不是原始漏电位置,可能仅仅是外部电路失效后产生的结果,如由于互连金属化或通孔开路或短路导致结发光变弱或者变强甚至进入饱和态等异常,需要结合电路原理图和版图进行分析,进而确定产生光发射的原因。样品为双模预置分频器,是典型的双极型集成电路,具备2 层金属化布线,功能已失效。静态参数测试时,V-端口输出电压与V+端口输出电压相比偏低,在V-与地之间施加电压时,漏电流偏大,推测此回路内部有明显失效。在V-与地之间加电700 mV/412 μA 并在PEM 下观察发现,T1晶体管均匀发光,T2晶体管未产生均匀发光(图3a),而均匀发光属于正常现象。从电路原理看(图3b),正常情况下T2晶体管应与T1晶体管均发生光发射,从PEM 发光情况可以推知T2晶体管已经损坏,经过反应离子刻蚀方法去层处理,再在扫描电镜下放大观察,可以明显看到T2晶体管的BE 结发生击穿(图3c)。

图3 间接的漏电流造成光发射Fig.3 Consequential leakage current photon emission

2.4 芯片背面定位

集成电路的发展趋势之一是金属化层增加、特征尺寸降低。多层布线的集成电路对正面定位是一个挑战。原因是:一方面由于层数增加,激光无法加热到底层金属位置的失效点,光子无法传播至芯片表面;另一方面是金属层增加时,热辐射区域面积比较大,OBIRCH 定位到的点会增大、模糊。因此,现在一个趋势是用背面定位来取代正面定位。

以一个0.18 μm 尺寸、7 层金属化的CMOS复杂可编程逻辑器件为例。经历传输线脉冲试验后,器件电源端口的漏电流明显增加,由于电源端口有退耦电容和栅极接地的ESD 保护结构,无法确定失效点,需要进行失效分析。用化学方法分别采用背面开封和正面开封,并进行OBIRCH 分析。两种方法均能明显找到失效点,但背面方法能够清晰看到失效区域形貌(图4a),而正面成像定位区域较为模糊(图4b),且真正短路点成为一个一个区域,尽管缩小了观察范围,其效果也不如背面成像精确。经过去层处理,可见内部PMOS电容边缘击穿(图4c)。

图4 正面定位与背面定位对比Fig.4 Comparison of frontside localization and backside localization

2.5 金属桥连定位

因工艺中多余物的存在或者介质破裂导致金属化桥连是另一类常见的漏电失效。此类缺陷若可以经由端口测试到则易于定位,如果是功能性失效,但无法通过电学测试进行电学定位,则需要集成电路在工作状态下进行动态下探测光发射逐步缩小范围定位,由于OBIRCH 可以明显记录电流的通过路径,可以定位到金属化桥连位置。失效样品为可变增益放大器,信号输入端为短路特性,在两端口之间施加200 μA 之间电流进行OBIRCH 定位。图5a 为激光扫描成像,图5b 为OBIRCH 图像,OBIRCH 技术记录了电流通路的图像,短路位置特征更为明显。金属化桥连的观察需要剖面得到,因此利用聚焦离子束(Focus Ion Beam,FIB)对桥连位置进行剖切,可以看出金属化通过破裂的介质层而桥连在一起(图5c)。

3 结论

1)从PN 结击穿的PEM 间接光发射和直接光发射定位、发光点的形状和位置分析出发光是漏电的原始位置还是作为结果性的漏电,结合集成电路版图分析和电路原理图分析有助于快速判断原始失效位置;

2)介质层绝缘性降低和金属化桥连案例表明OBIRCH 对原始漏电位置和阻性失效的定位更为准确;

图5 金属化桥连失效Fig.5 Metal bridge failures

3)OBIRCH 的背面定位失效分析应用于多层布线定位更为精确。

[1]Wu C L,Yao S Y,Corinne B.Leakage current study and relevant defect localization in integrated circuit failure analysis[J].Microelectronics Reliability,2015,55(3-4):463-469.

[2]恩云飞,罗宏伟,来萍.电子元器件失效分析及技术发展[J].失效分析与预防,2006,1(1):40-42.

[3]Shade G.光辐射显微镜分析技术的原理[J].来萍,译.电子产品可靠性与环境试验,1998(4):30-35.

[4]Ross R J,Boit C,Staab D.Microelectronic failure analysis,desk reference[M].USA:ASM International,2011:279-291.

[5]Hartmann C,Wieberneit M.Layout analysis as supporting tool for failure localization:Basic principles and case studies[J].Microelectronics Reliability,2008,48(8-9):1343-1348.

[6]陈选龙,刘丽媛,邝贤军,等.基于热激光激发OBIRCH 技术的失效分析[J].半导体技术,2015,40(1):73-78.

[7]Liebert S.Failure analysis from the backside of a die[J].Microelectronics Reliability,2001,41(8):1193-1201.

[8]陈选龙,刘丽媛,孙哲,等.OBIRCH 用于集成电路短路的失效定位[J].半导体技术,2015,40(11):856-860.