一种应用于K 波段的宽锁定范围的CMOS注入锁定三倍频器

2015-11-19王炜,李巍

王 炜,李 巍

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

22~29GHz波段是美国联邦通信委员会(FCC)制定的应用于汽车雷达的波段,随着近几年汽车电子的发展,K 波段的无线通信系统得到了越来越多的关注.作为无线通信系统中的重要组成部分,锁相环(PLL)需要给其提供高性能的本振信号.但是在高频下,由于MOS管以及电感、电容性能的恶化,很难设计一个满足通信系统要求的高性能压控振荡器(VCO);另一方面,紧跟VCO 的第一级分频器由于工作在高频下,会消耗很大的功耗.所以一个更好的方案是设计一个低频的VCO,后接一个三倍频器来产生所需要的频率信号.

三倍频器从原理上可以分为3类:第一类为基于器件非线性的三倍频器[1],这种结构由于涉及到阻抗匹配,电路结构比较复杂,而且对工艺偏差很敏感;第二类为基于混频器结构的三倍频器[2],这种结构的倍频频率较宽,但是这种结构会在输出端产生较大的直流失调,使混频器的晶体管进入饱和区,从而限制了转换增益;第三类为基于注入锁定结构的三倍频器[3],这种电路结构简单,功耗也比较小,但是传统结构锁定范围比较窄,一般在8%左右,致使其应用范围很有限.

本文针对注入锁定三倍频器锁定范围窄的问题进行研究,提出了一种基于电流旁路和双注入技术的注入锁定三倍频器.采用TSMC 130nm 工艺进行设计,版图后仿结果表明,在输入信号功率为2dBm 的情况下,锁定范围达到了21%,可以应用到诸如K 波段那样需要宽带应用的系统中.下面先分析传统注入锁定三倍频器的原理以及存在的问题,并提出相应的解决方法,最后给出仿真结果以验证所提出的解决方案.

1 传统注入锁定三倍频器原理

传统结构的注入锁定三倍频器(Injection-Locked Frequency Tripler,ILFT)的电路结构图如图1所示[3],主要由两部分组成:谐波发生器(Harmonic Generator)和注入锁定振荡器(ILO).利用MOS管的非线性特性,谐波发生器(M1和M2)能够产生输入频率的各次谐波信号;然后这些各次谐波注入振荡器,当振荡器的谐振频率在输入信号频率的三倍左右时,三次谐波相对于其他各次谐波获得了更大的环路增益,也就是说振荡器的谐振腔能够放大三次谐波,同时抑制其他各次谐波,从而该电路实现了三倍频的功能.

图1 传统注入锁定三倍频器的结构图Fig.1 The diagram of conventional ILFT

图2 注入锁定三倍频器的模型Fig.2 The model of ILFT

2 注入锁定三倍频器的模型和锁定范围分析

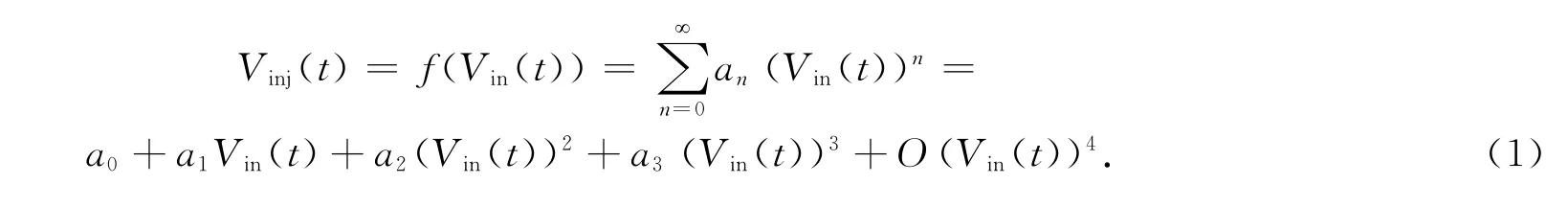

基于简单的注入锁定振荡器的模型[4],注入锁定三倍频器的模型如图2所示.产生各次谐波的谐波发生器可以用一个多项式函数f(Vin(t))表示.H(jω)代表ILO 中LC谐振腔的传输函数.则谐波发生器的输出可表示为

LC谐振腔的传输函数可表示为

其中Q 表示谐振腔的Q 值,H0是一个与谐振腔并联电阻成正比的量.在ILFT 锁定的前提下,输入信号和输出信号可以表示为

依据文献[4],注入锁定振荡器的锁定范围可以表示为

其中Vinj和V0分别表示振荡器的输入和输出电压的大小.将式(5)应用到ILFT,因此可得ILFT 的锁定范围可以表示为

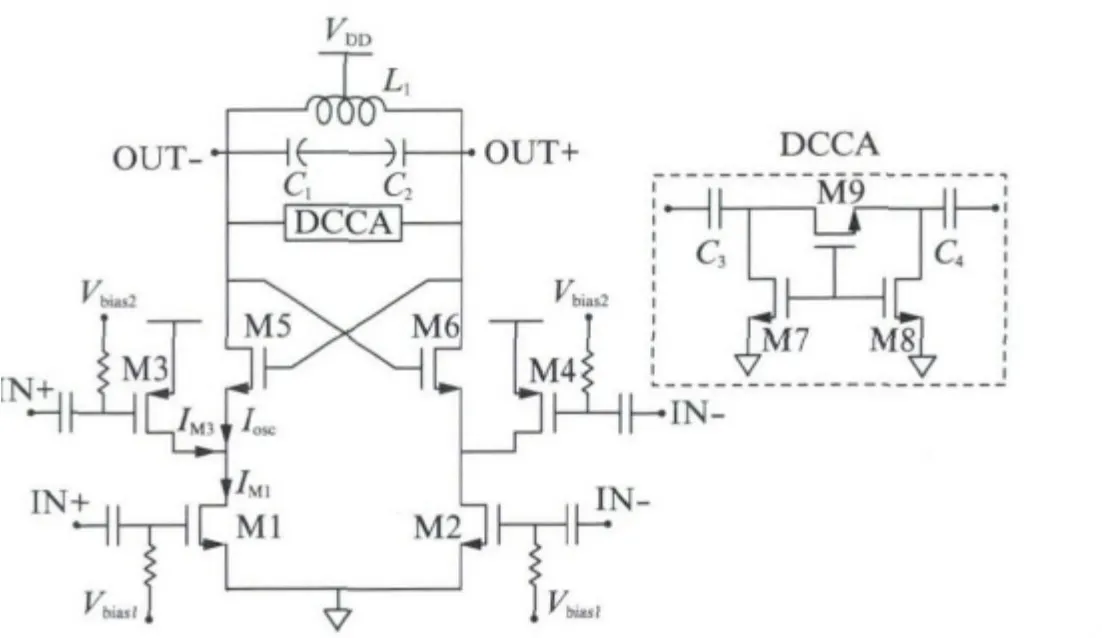

3 本文提出的注入锁定三倍频器电路设计

根据上文的分析,通过降低Q 值来获得宽锁定范围以牺牲功耗为代价不合理,所以要想设计一个具有宽锁定范围的注入锁定三倍频器需要采用其他技术来提高有效的三次谐波注入比率.本文提出的ILFT 的结构如图3所示.该结构与传统的ILFT 的不同之处是在于交叉耦合管的旁边并联两个旁路电流源(M3 和M4).一方面M3和M4的栅端偏置在合适的电压下,此时可以把M3和M4当做直流电流源,M3和M4对交叉耦合管进行分流,减小了流入谐振腔的电流,此时流入谐振腔的电流Iosc可以表示为

图3 本文提出的注入锁定三倍频器结构Fig.3 Structure of the proposed ILFT

另一方面,M3和M4的栅端也输入基波信号,同样利用MOS管的非线性,产生各次谐波信号注入ILO 中,为了避免PMOS管和NMOS管产生的各次谐波信号相互抵消,同侧的PMOS管和NMOS管的输入信号相位相同,此时流入谐振腔的三次谐波信号Iosc,3ω可以表示为

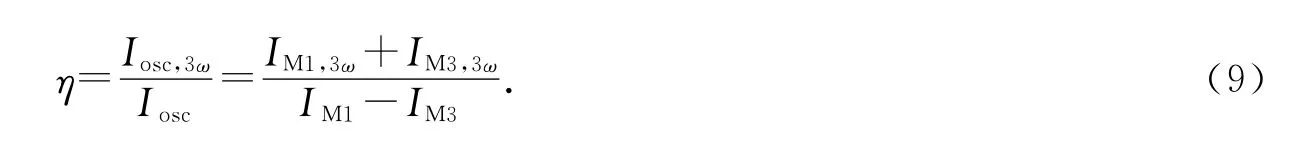

则采用本文提出的注入锁定三倍频器结构的三次谐波的注入效率η(电流形式)表达式为

而传统结构的三次谐波注入效率η(电流形式)表达式为

对比式(9)和式(10),本文提出的注入锁定三倍频器的三次谐波的注入效率η的分子变大了,同时分母变小了,所以该结构相对于传统结构三次谐波的注入效率η 大大增加,从而极大地扩展了三倍频器的锁定范围.下面对所提出的ILFT 的细节进行详细的分析.

3.1 谐波发生器的偏置

对于一个MOS管,其导通角φ 与MOS管阈值电压Vth,栅偏压Vbias和输入幅度Vi的关系表达式[5]为

将MOS管的漏电流ID近似为周期余弦函数,并用傅里叶级数展开.三次谐波注入效率η与导通角φ之间的关系如下:

其中I3是输出电流三次谐波分量幅度值,Imax是漏电流最大峰峰值,将式(12)作图如图4所示,MOS管的三次谐波注入效率η共有两个峰值,一个是在导通角为70°左右时,另一个是在导通角为220°左右.

为了使得该结构的注入锁定三倍频器的三次谐波注入效率最高,就需要使得谐波发生器的三次谐波注入效率最优,根据式(11)和式(12)需要给谐波发生器选择合适的偏置电压.该结构中,谐波发生器有两组:NMOS管组成的谐波发生器(M1 和M2)和PMOS管组成的谐波发生器(M3和M4),但是它们选择的依据是不同的.NMOS管组成的谐波发生器的偏置电压的选择就要使NMOS管的导通角在70°左右,这是为了使得三次谐波注入效率最高,同时为了使ILO 能够正常起振,要稍微增大M1和M2的尺寸以提供足够的振荡电流.但是PMOS管组成的谐波发生器的偏置电压的选择是要使PMOS 管的导通角为220°,因为如果PMOS管的导通角为70°时,流过的偏置电流很小,对ILO 的分流效果不明显,因此对三次谐波注入效率的提高也不明显.同时,M3和M4的偏置电压也不能过低,偏置电压越低,流过M3和M4的偏置电流就越大,对ILO 的分流效果就越明显,三次谐波的注入效率也就越大,但是流过ILO 电流的减小会导致输出电压摆幅的变小,摆幅太小无法满足电路性能指标要求,即使锁定范围再大也是没有意义的,所以PMOS管组成的谐波发生器的偏置电压的选择就要使PMOS 管的导通角在220°左右.

图4 MOS管三次谐波注入效率与导通角的关系Fig.4 The third harmonic injection ratio of MOS vs conduction angle

3.2 注入锁定振荡器

注入锁定振荡器由一对交叉耦合管(M5和M6)和LC谐振腔组成,在ILFT 中的主要作用是放大三次谐波和滤除其他各次谐波,为了获得更好的谐波抑制性能就需要一个高Q 值的LC 谐振腔,因此本文采用的是两个固定电容而不是可变电容,因为可变电容的Q 值在如此高频率下的衰减很大.同时,为了扩展振荡器的谐振频率,从而扩展锁定频率范围,本结构还采用了固定电容阵列(DCCA).

4 版图实现和仿真结果

本文中提出的注入锁定三倍频器采用TSMC 130 nm 工艺进行设计,版图如图5 所示.核心电路面积为0.35mm×0.3mm.电路设计采用的是1.2 V 电源电压,核心电路的最大直流功耗为7.8mW.

向注入锁定三倍频器注入一个功率为2dBm,频率为8GHz的正弦信号时,ILFT 可以稳定输出一个单端功率为-14.56dBm、摆幅为383.3 mV 的24 GHz的信号.图6(a)和(b)分别是输出信号的频谱和时域波形.

理论上讲,注入锁定三倍频器的相位噪声相对于信号源要恶化9.54dB(20lg3)[6].实际上,仿真结果表明本文提出的ILFT 在整个锁定频率范围内的相位噪声@1 MHz频偏相对于信号源恶化(10.2±0.3)dB,这与理论值9.54dB差距很小,在不同工艺角下相噪恶化程度如图7所示.这表明本文提出的ILFT 本身引入的相位噪声的恶化很小.

本文提出的ILFT 在不同工艺角下锁定范围随着输入频率的变化关系如图8所示,不同工艺角下的锁定范围有稍许差别,在FF corner下的锁定范围最大.从图中可以看出在TT corner下,在输入信号功率为2dBm 时,锁定范围为5.1GHz,工作范围是21.0~26.1GHz.在1.2V 电源电压下的最大功耗为7.8mW.

图5 本文提出的注入锁定三倍频器版图Fig.5 Layout of the proposed ILFT

图6 在8GHz信号输入时注入锁定三倍频器的输出信号Fig.6 Output of the proposed ILFT with 8GHz input signal

图7 本文提出的ILFT 在锁定频率范围内相对于信号源的相位噪声恶化Fig.7 Simulated phase noise degradation vs output frequency of the proposed ILFT

图8 锁定频率范围随输入功率变化的关系Fig.8 The injection locking range vsinput injection power

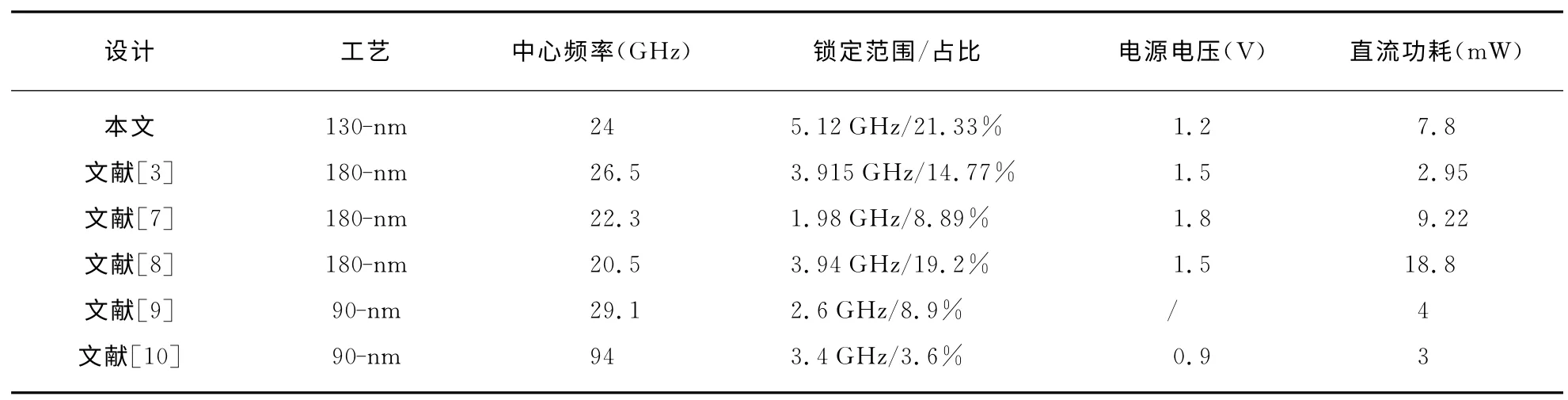

表1是本文所提出的ILFT 与其他参考文献的性能比较,和文献[3,9-10]相比,本文结构的功耗虽然有点大,但是锁定范围要更宽,和文献[7-8]相比,本文结构功耗更小,锁定范围也更宽.可见在130nm CMOS工艺下,本文提出的ILFT 在基本不增加功耗的前提下,实现了一个很宽的锁定范围.

表1 本文提出的注入锁定三倍频器与其他文献的性能对比Tab.1 Proposed ILFT performance comparison with other works

5 结论

本文针对传统注入锁定三倍频器锁定范围窄的问题,提出了一种基于电流旁路和双注入技术的注入锁定三倍频器,该三倍频器在不增加功耗的前提下,极大地提高了三次谐波的注入效率,从而扩展了锁定范围,通过TSMC 130nm CMOS工艺完成了该注入锁定三倍频器的电路和版图.仿真结果表明,在输入信号功率为2dBm 时,锁定范围为5.1GHz,工作范围是21.0~26.1GHz,最大功耗为7.8mW.这种方法是对提高传统结构锁定范围较为有益的一种尝试,可以应用到诸如K 波段那样需要宽带应用的系统中.

[1]KOU N C,KAO J C,TSAI Z M,et al.A 60 GHz frequency tripler with gain and dynamic range enhancement[J].IEEE Transactions on Microwave Theory and Techniques,2011,59(3):660-671.

[2]GHOUCHANI S S,PARAMESH J.A wideband millimeter-wave frequency doubler-tripler in 0.13-μm CMOS[C]∥Radio Frequency Integrated Circuits Symposium(RFIC).Anaheim,CA,USA:IEEE Press,2010:65-68.

[3]CHEN M C,WU C Y.Design and analysis of CMOS subharmonic injection-locked frequency triplers[J].IEEE Transactions on Microwave Theory and Techniques,2008,56(8):1869-1878.

[4]RAZAVI B.A study of injection locking and pulling in oscillators[J].IEEE Journal of Solid-State Circuits,2004,39(9):1415-1424.

[5]MAAS S A,Nonlinear microwave and RF circuits,2nd edition[M].Norwood,MA:Artech House,2003.

[6]Puglia K V.Phase noise analysis of component cascaded[J].IEEE Microw Mag,2002,3(4):71-75.

[7]CHEN C C,WU J W,CHIAO T F.Dual-injection sub-harmonic injection-locked frequency tripler[C]∥IEEE Microwave Conference Proceedings(APMC).Kaohsiung,China Taiwan:IEEE Press,2012:1214-1216.

[8]LO Y T,KIANG J F.A 0.18-μm CMOS self-mixing frequency tripler[J].IEEE Microwave and Wireless Components Letters,2012,22(2):79-81.

[9]TAM S W,SOCHER E,WONG A,et al.Simultaneous sub-harmonic injection-locked mm-wave frequency generators for multi-band communications in CMOS[C]∥Radio Frequency Integrated Circuits Symposium(RFIC).Anaheim,CA,USA:IEEE Press,2008:131-134.

[10]YEH Y L,CHANG H Y.A W-band wide locking range and low DC power injection-locked frequency tripler using transformer coupled technique[J].IEEE Transactions on Microwave Theory and Techniques,2013,61(2):860-870.