印制电路板及电子封装今后的技术发展

2015-09-12田民波清华大学北京100084

田民波(清华大学,北京 100084)

印制电路板及电子封装今后的技术发展

田民波

(清华大学,北京100084)

ITRS2012路线图表明半导体芯片继续向微细化、多端子、高速化方向发展,与此同时,电子封装正从2维向3维转变。无论对于封装基板、插入板、母板还是背板来说在形式、结构、制作方法、加工工艺、特别是材料方面都要适应这种发展和转变。文章介绍了印制线路板及电子封装今后的技术发展。

ITRS 2012路线图;组抗匹配;封装基板;插入板;3D封装;无孔盘PCB

1 引言

各种各样的电子设备都毫无例外地利用作为连接、控制电路的电子回路。这些电子回路使用以半导体元件为首的各种各样的电子元器件自不待言,也离不开将它们组合、搭载、连接在一起,以发挥整体功能的印制电路板。印制电路板依使用其机器的用途而异,不仅数量大,规格多,而且要求的功能和技术水平各不相同,将它们网罗于一篇文章中并不现实。为此,本文仅考虑应用于高速、大量信息处理设备用的印制电路板(PCB)。而且所用的绝缘材料主要涉及有机树脂绝缘体的PCB。

2 发展路线图?——高速化、高密度化的倾向

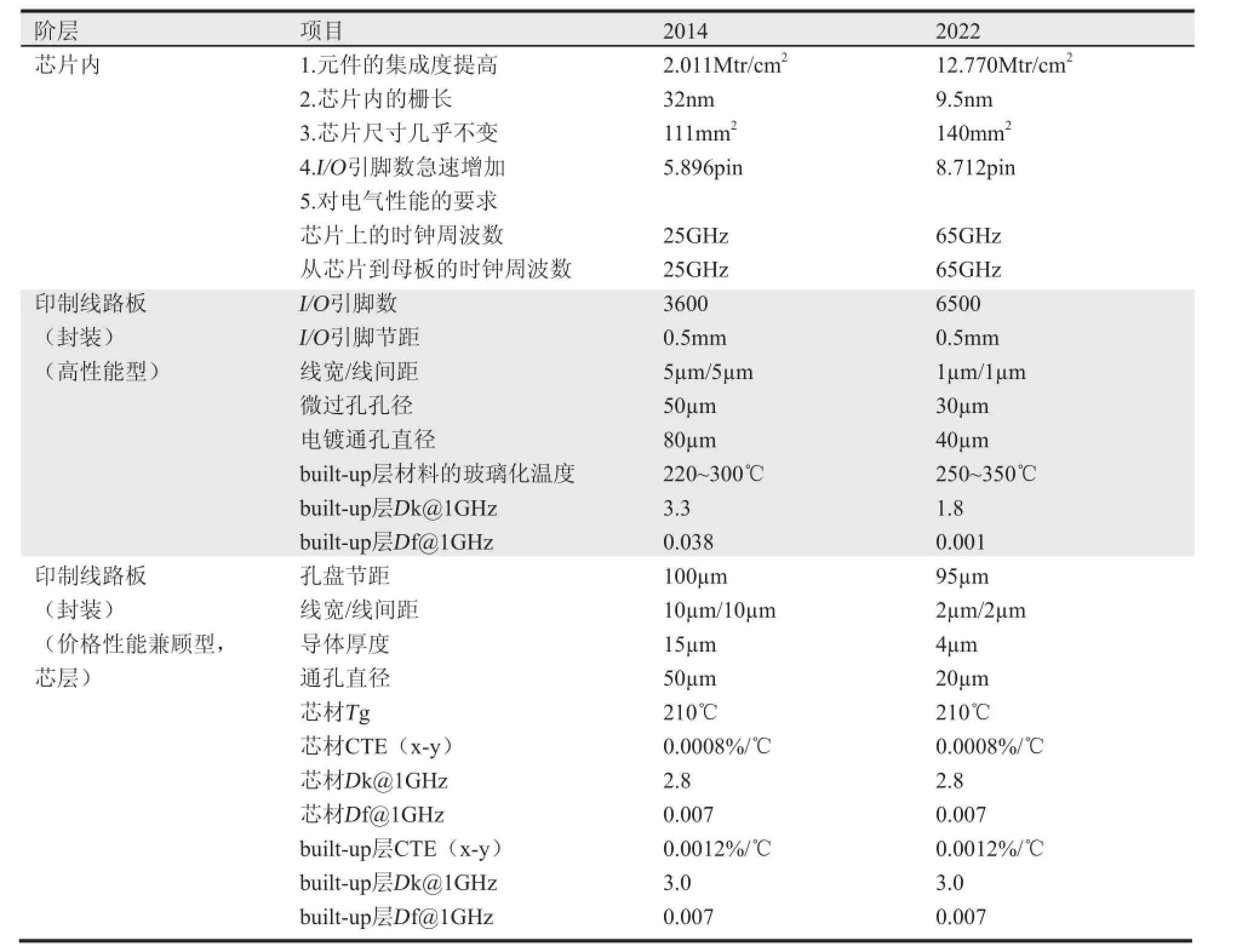

表1列出ITRS(国际半导体技术规划组织)2012发展路线图梗概。半导体芯片进一步向高速化、高集成化方向发展,芯片面积从111 mm2向140 mm2进展,尽管增加并不大,但I/O端子数从5800 pin向8700 pin大幅度增加。因此,芯片表面的电极凸点(bump),承载芯片的封装基板的焊盘(pad)都会向窄节距、小尺寸方向发展,而且都需要一定程度的扇出(fanout)。

而且,芯片内的时钟频率从25 GHz提高至65 GHz,进一步高速化。对此,预计母板上的时钟周波数也会达到65 GHz。

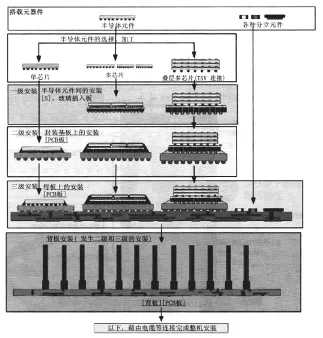

3 安装级数和布线密度

电子通信设备是以半导体芯片为首的许多元器件的集合体,并非单独由半导体芯片构成。全部电子元器件都是搭载在印制电路板上,藉由相互连接构成统一的整体。这种连接如图1所示,是由几个阶段构成的,称其为安装的“级”,而每个阶段的连接都与形式不同的PCB密切相关。

要构成这些“级”,进而成为电子设备,直接使用具有纳米量级尺度的半导体超微细回路是不可能的,需要构成不同的封装阶段,将半导体芯片内的连接经几次扇出来完成。

在图1中,PCB可分为封装载板、母板、背板(Back Panel)等几大类,但基本上都由有机树脂板构成。在这些安装阶段,发生最大影响的PCB是连接半导体裸芯片的封装载板。

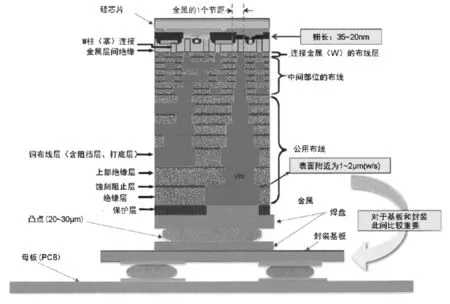

半导体元件的断面模式图在图2中示出。图中还进一步表示封装载板与母板的接续关系。在半导体元件的发展初期,一块封装载板搭载一个芯片,而随着微细化及性能的提高,通过分割搭载或将功能不同的元件混合搭载等,以实现功能密集、功能强化,并逐渐发展成所谓3D芯片搭载。

表1 从ITRS2012路线图看半导体芯片和PCB的发展趋势

图1 IT设备的安装阶段(封装分级)

图2 半导体芯片的断面和向封装载板、母板的连接

如此,随着半导体元件的高密度化,I/O端子数增加、节距微细化、高密度布线势趋必然。按Rent经验规则,有式(1)所表述的关系。

P=kGγ(1)

式中,P为输入输出端子数;G为集成的门数;k、γ为常数。

现在,高集成化不断发展,上式中γ取正值。因此,伴随着G的增加,P不断增加。

功能元件在硅芯片的底部形成,其布线(布线规则)逐年向微细化方向发展,最近达到17nm(12 nm)的水平。但是,为了与其外部连接,半导体芯片内的引线端子需要进行扇出,在与外部连接处,采用(2~4)μm,或略大一些布线规则,经由凸点,与封装基板实现互连。

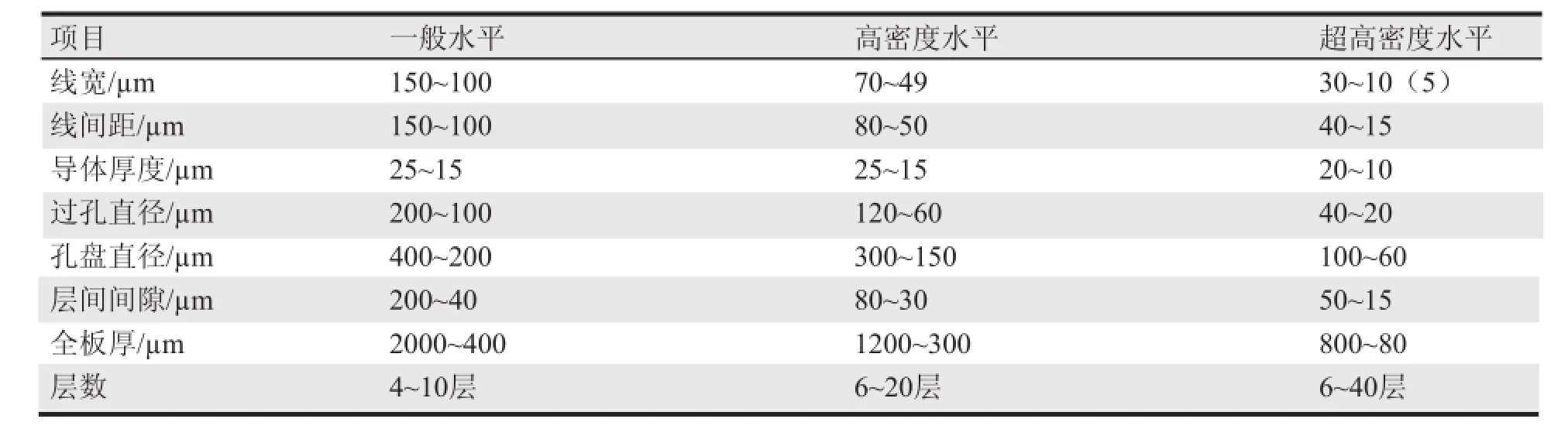

现在,即使最小的凸点,其直径也在20 μm。因此,作为封装载板的现实的布线规则,一般认为可实现的为5 μm线宽,而(2~3)μm图形宽度的封装载板的开发也在进行之中。关于5 μm的可能性是在2007年提出的,最近的集中倾向示于表2。需要指出的是,芯片凸点(bump)与同布线相连接的焊盘(pad)的大小,以及连接方法等是需要进一步开发的大课题。

4 半导体芯片的集成度与封装的发展动向

表2 印制线路板的布线规则(从现在至将来)

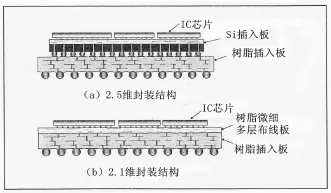

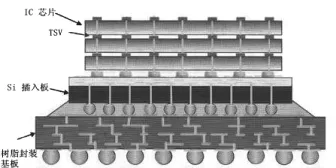

为了接近半导体芯片集成度的界限,并将不同的多个芯片收纳于同一封装内,已提出多种方案。最近,针对平面阵列结构中布线距离太长,外形也太大的现状,提出立体结构布置的多种方案。正从所谓2维向3维发生结构转换。提出的方案示于图3,在2维、3维之间还有2.1维、2.5维封装等。图3(a)是在树脂插入板(interposer)上进一步重叠硅插入板,它属于3维封装,但在封装阶层上只增加了一个封装阶层。另外,图3(b)是在树脂插入板的单面特别设置微细布线而构成的2维封装形式。但是,图4所示的半导体芯片的3维结构等,预计今后会有大的变化,比较一致的看法是,该结构内的阶层数会进一步增加。如此看来,半导体元件的3维封装结构今后会更加复杂化,对封装构成也提出了多种多样的各种方案。

图3 正在推广的2.1维、2.5维封装的结构实例

图4 芯片3维封装的例

5 印制电路板的电气特性

针对以封装载板为中心的PCB,人们对其高密度化提出更高要求。与此同时,对高速信号的处理也变得越来越重要。

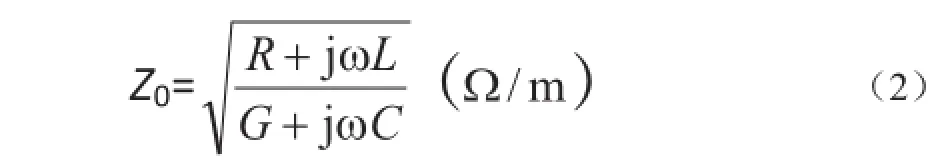

为了适应数字信号处理的高速化、大容量,要求对下式表示的特性阻抗(Z0)应有高精度的匹配。特性阻抗由(2)式表示。

式中,ω(=2πf)为周波数;R为电阻;G为电导;L为电感;C为电容。

为了实现所要求的阻抗匹配,信号导体与接地线要以成对的图形构成,导体宽度、高度,信号线与接地线间的距离需要很高的精度,为此,对制作技术以及绝缘层的介电常数、介电损耗等必须严格管理与控制。如表1所示,由于将来“芯片到板”(Chip to Board)的时钟周波数也要求达到65 GHz,因此,针对匹配,今后会要求更严格的公差。

由于对微细化、高密度化的要求越来越高,因此,对导体间高绝缘化的要求越来越严格。

6 面向高密度化、高速化的制造技术

作为多层PCB的制作方法,预计采用电镀法的工艺今后会以电镀通孔法和积层法(built-up)为中心展开,下面讨论在这两种制作工艺中,与高密度化、高速化相关的技术关键。

6.1高密度布线技术

多层PCB的导体图形都采用铜金属。在对覆铜合板铜箔的刻蚀中,要保证侧蚀(Side Etching)很小是相当难的。为减少侧蚀,需要减少刻蚀量。为此,广泛采用使用超薄铜箔的图形电镀法;但为了实现更高密度布线,推荐采用不使用铜箔的半加成法。这种方法存在的问题是,与树脂层平滑面的结合(密着)性差,以及为了去除打底层(seed),会对导体底部发生侧蚀等。现已开发出防止侧蚀发生的刻蚀液,但如后面所述,对于提高树脂平滑面电镀层附着性的工艺,还未达到实用化。

另外,由于普通积层式PCB中芯板的通孔会降低信号的传送性,因此,正在大力开发无芯板的built-up PCB。

6.2适应高速信号传送的技术

综上所述,为适应高速信号的传送,藉由特性阻抗的匹配,采用低介电常数、低介电损耗的材料,以及利用填孔实现叠层以使电感减少等这些有效的方法已达到实用化。但是,对于高周波信号的传送来说,集肤效应越来越显著。在信号传送中,随着高周波化,信号越来越靠近导体表面传送,称此为集肤效应。称电流密度降低到表面1/e的厚度为集肤深度δ,δ由(3)式给出:

式中,σ为电导率;ω(=2πf)为角频率;m为磁导率。

因此,导体与树脂间结合面的平滑性极为重要。通过在与铜图形表面相结合的树脂表面形成微小凸凹以增强锚连(anchor),藉由特殊的锡系化合物的耦合(coupler),或者采用特殊的底涂料(primer)等方法都可以提高与平滑铜箔间的结合力。但是,对于适合于微细化布线的半加成法来说,要求化学镀铜层与树脂面间有强固的结合,针对这一技术已提出许多解决方案,开发也活跃地进行中,但仍未找到适于工程应用且适应范围广的工艺技术。

另外,对于built-up PCB来说,通常采用的芯板的传送特性因微通孔而变差,希望采用无芯板式built-up PCB。但是,构成通常的built-up层的树脂层的强度太低,直接采用难以构成满足性能要求的PCB。通过使芯板变薄,built-up层中也采用薄玻璃布半固化片(prepreg)进行补强,或者在built-up层中增加加固层(stiffener)进行补强等方法,目前已达到实用化。

6.3适应高速信号传送的技术

由于高密度布线,导体宽度、导体间距必然变小。其结果,导体电阻必然增大、绝缘电阻必然变小。而且,在微细导体布线中,对于因导体及绝缘层的热膨胀系数的差异导致热应力所造成的破断,或者因电流密度增加而导致的显著的电迁移,必须严加注意,需要尽可能增加导体层的厚度。当然,提高铜箔、化学镀铜、电镀铜的物性也极为重要。对于微细节距来说,需要认真对待电化学迁移问题。应对导体间距的微细化,对于绝缘树脂的高绝缘化,玻璃布、填料等与树脂间的结合(密着)性的提高,PCB制作中基板的污染防止管理等也很重要。同时,对高密度PCB的使用条件,环境的严密管理等也提出更高的要求。

7高密度印制电路板的发展趋势——无孔盘印制电路板

作为采用有机树脂的高密度PCB的封装载板。从现在的开发动向看,其布线密度的最小线宽/间距为5mm/5mm。其中半导体芯片与封装载板连接相对双方的孔盘(land)和其间的凸点(bump)的大小会成为问题。如图2所示的那样,与芯片内布线及封装载板上的布线相比,凸点尺寸是异常大的,显然它会妨碍封装的高密度化。为此,对导体线宽/间距提出2 mm/2 mm这样更微细的要求,但从可靠性观点又会产生问题。如果无孔盘布线成为可能,即使线宽/间距为5 mm/5 mm,也可获得相当的高密度化。

图5 无孔盘PCB的模式图

藉由无孔盘印制布线实现的多层PCB的模式图示于图5。布线z方向过孔的连接也是无孔盘的。

但是,要实现无孔盘化有许多问题需要克服,下面列出其中的几个要解决问题都有相当的难度。

(1)与微细布线直接连接的连接部位的可靠性。

(2)微细布线与过孔间的无孔盘连接的可靠性。

(3)导体与绝缘材料的结合(密着)性。

(4)绝缘材料的尺寸稳定性(xy面,翘曲,扭曲等)。

(5)绝缘材料、导体材料的热特性的提高

(6)高精度制作工艺的构筑。

(7)多层印制线路板中位置对准的高精度化。

(8)制作环境的优化。

(9)元器件搭载的高精度化。

除此之外,需要解决的问题还有很多。

通过采用以上所述的作为具有微细图形PCB的封装载板,与硅基板、玻璃基板不同,通过使因热膨胀系数之差所造成的应力降低,且加工性优良,可期待可靠性进一步提高。

Technologies for PCB and electronic package in the future

TIAN Min-bo

The ITRS 2012 ROAD MAP describes that IC chip will develop of IC chip to fne pitch, more I/O pinns, high speed continuously, as well as that the electronic packages are transforming from 2 maintain to 3 maintain. No matter for package substrate, inter poser, mother board, or for backplane board, the forms, structures,manufacture processes and technologies must suit the development and transformation. This paper introduces technologies for PCB and electronic package in the future.

ITRS 2012ROAD MAP; Impedance Matching; Package Substrate; Interposer; 3D Package; Landless PCB

TN41

A

1009-0096(2015)09-0046-05