一种抗单粒子翻转的D触发器

2015-08-07杨玉飞

杨玉飞

(中国电子科技集团公司第四十七研究所,沈阳110032)

一种抗单粒子翻转的D触发器

杨玉飞

(中国电子科技集团公司第四十七研究所,沈阳110032)

以互锁存储单元(DICE)结构为基础,采用0.35μm CMOS工艺,设计了一种具有抗单粒子翻转的带置位端的D触发器。通过将数据存放在不同节点以及电路的恢复机制,使单个存储节点具有抗单粒子翻转的能力。通过Spectre仿真,测试了触发器的抗单粒子翻转能力。在版图设计中采用增大敏感节点距离和MOS管尺寸的方法进一步提高了D触发器抗单粒子翻转的能力。

集成电路设计;单粒子翻转;双互锁存储单元;D触发器

1 引 言

数字电路芯片在辐射环境中,周围的能量粒子会渗透到芯片内部,并发生电离辐射,在能量粒子的运动轨迹上产生一定数目的电子和空穴对。这些由于单个能量粒子电离辐射而产生的电子和空穴有可能在电场的作用下被电路的内部节点吸收,吸收了电子或者空穴的节点有可能改变原有电平。上述效应称为单粒子翻转效应。

随着集成电路工艺技术的发展,晶体管特征尺寸越来越小,电路中表征电平的电量也随之减小,导致数字集成电路越来越容易发生单粒子翻转效应。在辐射环境中工作的集成电路,容易受到单粒子翻转的威胁。1975年,美国通信卫星所用数字电路中的JK触发器,由于重核粒子的作用被触发,发生误翻转,这是第一次有记录的单粒子翻转现象。即便在不认为有辐射的环境中,也有发生单粒子翻转的可能性。D触发器是数字电路中使用最多的时序器件,所以本文设计了一种抗单粒子翻转的带置位端的D触发器。

2 DICE技术设计的D触发器

2.1 抗单粒子翻转技术

D触发器一般由两个相同的锁存器构成,所以对触发器抗单粒子翻转的设计就是对锁存器的加固设计。目前国内外抗单粒子翻转锁存器的设计已经很成熟,常用的加固技术有:空间冗余技术、时间滤波技术、电荷补充技术、编码技术和双重互锁存储单元技术(Dual Interlocked Storage Cell,DICE)等[1]。相比与其它的加固方式,DICE在面积、速度和功耗方面比较有优势,所以我们使用DICE技术来设计D触发器。

2.2 DICE单元原理

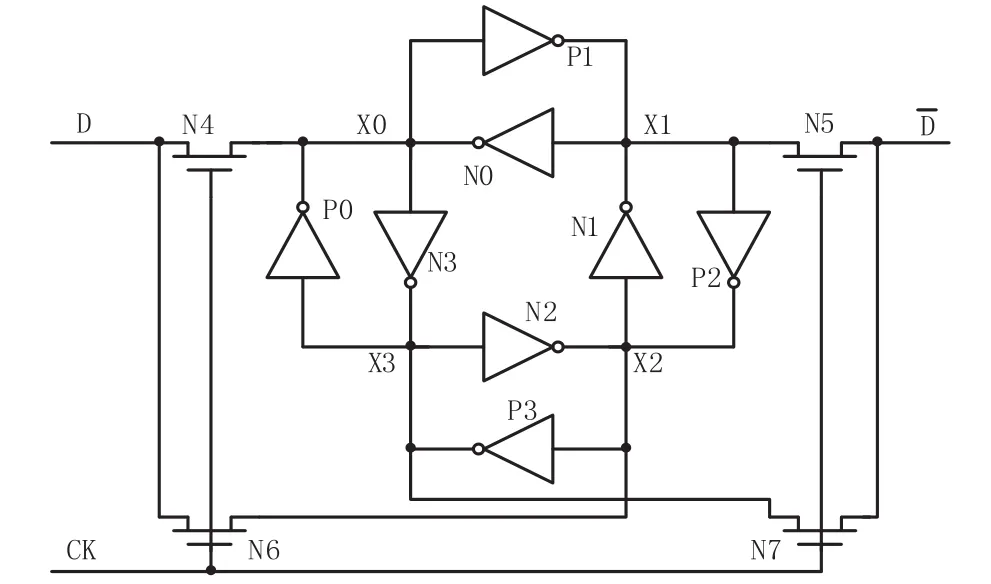

DICE采用新颖的四节点冗余锁存结构。其基本设计思想是采用冗余结构备份存储的数据,当存储单元中单个节点由于单粒子轰击发生翻转时,备份的数据能通过反馈及时恢复翻转的数据。图1所示为DICE单元原理,单元中有4个逻辑状态分别存储在4个节点中,其中每个节点的状态都由相邻的节点控制,而对角的节点并不相互联系。节点Xi(i=0-3)通过晶体管Ni-1和Pi+1控制相邻的两个节点Xi-1和Xi+1(i为以4为模的1位整数)。

图1 DICE原理图

事实上,由于反相器中有一个MOS管并不起作用,因而图1中反相器可用P型晶体管或N型晶体管替换,替换的原则是Pi都替换为PMOS,而Ni都替换为NMOS。它们形成两个相对的反馈环:一个是顺时针的P型晶体管环,即P0-P3;另一个是逆时针的N型晶体管环,即N3-N0。如果把节点X0-X3=0101作为逻辑状态“0”,由晶体管N0-P1和N2-P3形成的横向反相器环将导通,形成两个锁存器,且节点X0-X1和X2-X3上存储了同样的数据。此时,竖直方向上的反相器环N1-P2和N3-P0处于关闭状态,隔离两个横向锁存器。对于逻辑状态位为“1”的情况,X0-X3=1010,竖直方向的反相器对N1-P2和N3-P0导通,起锁存作用,同样地,横向晶体管对N0-P1和N2-P3关闭,隔离两个竖直方向的锁存器。

当一个负的翻转脉冲出现在任意一个当前状态为“1”的节点Xi(i=0-3)时,都会通过P型反馈晶体管Pi+1在节点Xi+1上产生一个正的脉冲扰动,但不会影响到存储在节点Xi-1上与Xi+1相同的存储状态。因为负的翻转脉冲不会通过反馈晶体管Ni-1(NMOS)传递,而传递到节点Xi+1的正脉冲扰动不会通过晶体管Pi+2进一步传递到节点Xi+2。因此,节点Xi-1和Xi+2被隔离,保持着它们的逻辑状态不受影响。由此可见,单粒子对节点的轰击仅仅是在节点Xi和Xi+1上引起暂时扰动。这种扰动在单粒子事件之后很快就会消除,因为其他两个节点Xi-l和Xi+2的状态将通过晶体管Pi和Ni+1的反馈作用强迫翻转节点恢复到之前的状态。对于正瞬态扰动脉冲,也可以做类似分析。

2.3 基于DICE结构的触发器设计

基于DICE结构,采用0.35μmCMOS工艺,设计了带置位端的抗单粒子翻转的D触发器,电路结构如图2所示。

图2 带置位端的DICE结构D触发器电路

DICE单元抗SEU的基本原理在于其内部存在4个相互耦合的存储节点。假如由于某种原因其中一个存储节点发生了翻转,其余存储节点便会将此错误翻转的数据纠正过来,使得电路输出仍然保持正确。本文所设计的抗单粒子翻转的D触发器是针对4个存储节点同时进行的,N1、N2和P1是为了满足置位功能而设计的,它们受信号C和C1控制,其中C1表示置位信号C的相反值。节点n1和n2相同,n3和n4相同。当C为1,C1为0时,电路为一个正常工作的锁存器单元,输出端Q的存储状态受输入端D和时钟CK控制。数据D传输时,若节点n1信号发生单粒子翻转,节点n3可以将错误数据纠正并反馈到n1;若节点n2信号发生单粒子翻转,节点n4可以将错误数据纠正并反馈到n2,保持电路输出结果正确。

3 单粒子效应仿真

目前,单粒子效应的电路级仿真一般采用经验公式,其方法是以Messenger等人提出的描述单粒子入射瞬时电流脉冲的双指数函数模型作为基础[2]。该模型的表达式如下:

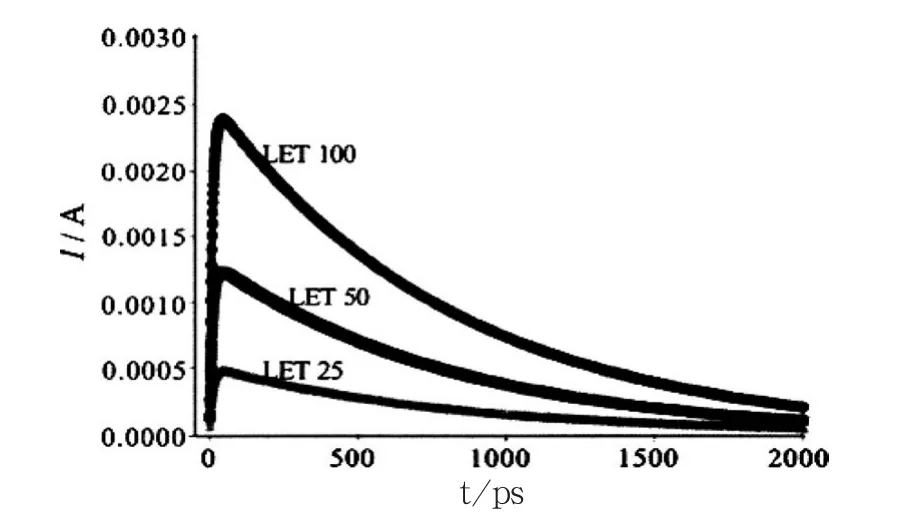

式中,α为电荷收集的时间常数,β为建立粒子轨迹的时间常数。根据表达式,并结合不同单粒子入射的经验数据,可得到单粒子瞬时脉冲的波形,如图3所示。通过改变电流峰值,可得到不同LET的单粒子脉冲。Gadlage的试验表明,该模拟方法与测试数据能很好地吻合。

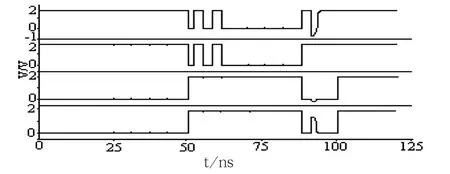

在电路仿真中,通过将双指数函数电流源接入敏感节点,可以模拟单粒子入射造成的瞬态效应。敏感点处的电压将被降到0V以下,或者推高至电源电压以上,这是一种较坏情况的单粒子翻转收集电荷模型[3]。触发器在单个数据存储节点加入脉冲电流源模拟单粒子入射(LET=100MeV×cm2/mg)的仿真波形如图4所示。

图3 Spectre仿真得到的单粒子瞬时脉冲波形

图4 DICE触发器一个节点受单粒子轰击的响应

可以看到,某个敏感节点在受到单粒子轰击后发生了翻转,但干扰脉冲在经过大约1.1ns后即被冗余结构的反馈消除,原来的存储状态能及时恢复而不发生改变。可认为电路的单个节点具有抗SEU的能力。

4 版图设计

在DICE结构中,如果相邻的两个节点同时发生翻转,那么输出也会发生翻转,因此在版图设计中,我们将相邻的两个敏感节点尽量远离,把MOS管的尺寸设计的比较大,以增大敏感节点的寄生电容,从而实现电荷补充,达到进一步提高抗单粒子翻转能力的作用。同时,在版图中采用了其它技术增加了单元抗单粒子锁定的能力。DICE结构的D触发器版图设计如图5所示。

图5 DICE结构的D触发器版图

5 结束语

设计基于DICE结构,采用0.35μm的CMOS工艺,设计了一个带置位端的抗单粒子翻转的D触发器。理论分析及单粒子效应仿真表明,该触发器具有单个节点抗单粒子翻转的能力。并且在版图设计中采用增大敏感节点距离和MOS管尺寸的方法进一步提高了D触发器抗单粒子翻转的能力。

[1] 陈盘训.半导体器件和集成电路的辐射效应[M].北京:国防工业出版社,2005:230-231.

[2] GADLAGE M J,SCHRIMPF R D,EATON P H,et al.Single event transient pulse widths in digitalmicrocircuits[J].IEEE Trans Nuel Sei,2004,51(6):3285-3290.

[3] 李玉红,赵元富,岳素格,等.0.18μm工艺下单粒子加固锁存器的设计与仿真[J].微电子学与计算机,2007,24(12):66-69.

Study on A SEU-Hardened D Flip-Flop

Yang Yufei

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

:Based on dual interlocked storage cell(DICE)architecture,0.35μm CMOS process is used to design a D flip-flop which is immune to single-EVENT upset with set control.Through recovery mechanism of the circuit single eventeffect,the single event upset(SEU)immunity is achieved by storing data on different nodes.SEU of the circuit is simulated by Spectre.In the layout design,the methodology such as increasing distance between sensitive nodes and size of MOS transistors,is used to further improve ability immune to single-EVENT upset.

Integrated circuit design;SEU;DICE;D flip-flop

10.3969/j.issn.1002-2279.2015.01.004

TN402

A

1002-2279(2015)01-0010-03

杨玉飞(1982-),女,辽宁台安人,硕士研究生,工程师,主研方向:集成电路设计。

2014-04-18