集成电路工艺外延图形漂移剖析

2015-08-07宋玲玲王利斌

宋玲玲,李 浩,王利斌

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.93271部队,沈阳110032)

集成电路工艺外延图形漂移剖析

宋玲玲1,李 浩2,王利斌2

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.93271部队,沈阳110032)

外延结构的生长特性决定了埋层图形在外延层上漂移的现象,这种现象会给工艺带来危害,导致产品失效。在实际工艺中,通常是通过一定的校正原则来抵消埋层漂移的影响。另外,最后还给出了隔离击穿电压的测试分析方法。

外延;漂移;校正

1 引 言

在由体硅材料制作的双极晶体管中,体硅电阻率确定着集电极击穿电压,需用高阻材料才能取得高击穿耐压,但过大的集电极串联电阻又导致频率响应不好和大功耗[1]。外延生长技术是在1959年开始发展起来的晶体生长技术。采用低阻衬底上外延高阻材料的外延片制作双极器件,就可以解决上述矛盾。它的出现解决了过去半导体器件生产中许多难于解决的矛盾,大大提高了器件的电学特性,为高频大功率晶体管和集成电路的发展开辟了广阔道路。

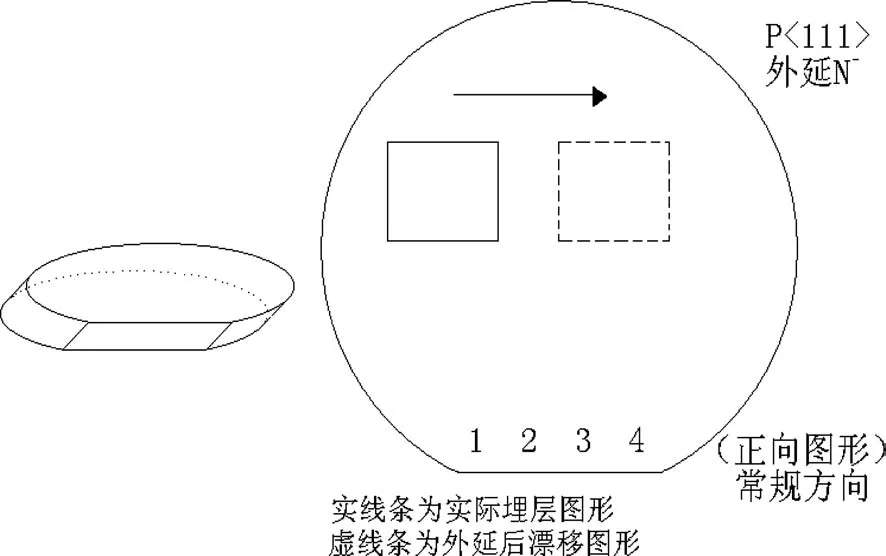

在集成电路制造的双极工艺中,在单晶片上生长外延层,就会出现引入埋层漂移问题。例如,在TTL标准工艺中,需要P<111>单晶衬底上生长N-外延,在N-外延生长中图形会产生漂移,该现象是由于外延层的生长特性引起的。如图1所示,在埋层片上观察到的图形较实际图形向右偏移了,偏移尺寸大约为外延层的厚度。

2 基本原理

外延生长就是在一定的条件下,使某种物质的原子(或分子)有规则排列,定向生长在经过微细加工的晶体(一般称为衬底)表面上。生长的外延层是一种连续、平滑、并与衬底晶格结构有对应关系的单晶层[2]。

图1 埋层漂移图形

虽然,外延工艺水平在不断提高,但只是在漂移量上发生了改变,不能从根本上消除图形漂移。外

3 外延漂移造成工艺危害

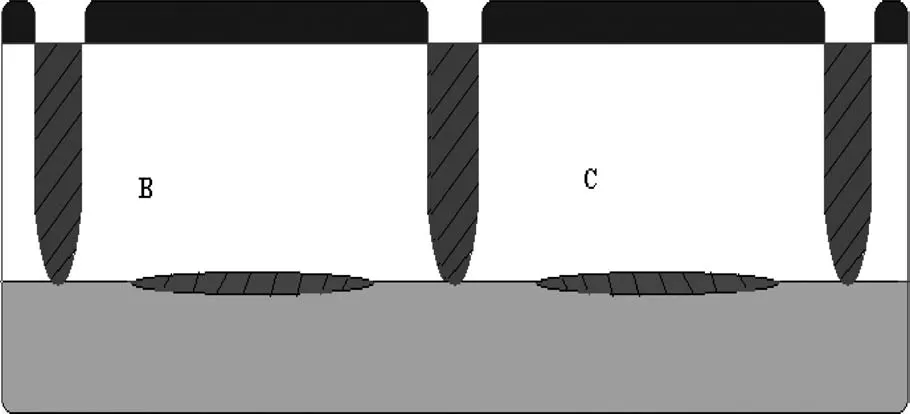

延漂移主要影响是在外延隔离上,造成岛与岛之间击穿电压为零,隔离不成功。如图2是隔离成功的剖面图,隔离后分为B岛和C岛;图3是隔离成功的伪像。

图2 隔离透

图3 隔离不透

在实际工艺中,版图内各个单元尺寸不尽相同,设计规则尺寸应为埋层到隔离的最小尺寸,否则就会如图3所示,由于B岛内的埋层发生漂移,而导致隔离未透的现象。实际工艺中,埋层结深大约为4~6μm,如果发生埋层漂移,部分埋层与隔离槽发生相撞时,即使相邻的隔离岛在隔离工艺正常条件下完成,N+埋层也不易被隔离的P+扩透。因此,隔离槽底部仍有N+把相邻的隔离岛相连在一起,导致图3中的B岛与C岛之间击穿电压为零,造成未隔离透的假象。很显然,图3中若B岛或者C岛与无漂移的隔离岛或者无埋层的隔离岛之间的击穿电压,测试将会是正常击穿电压。

4 工艺校正

由于上述问题在实际工艺中的存在会导致产品失效,因此,在平面版图设计时通常给予校正。

4.1 埋层图形漂移校正(亦称光刻套偏)方案

工艺实验证明P<111>N-外延片,N+埋层漂移方向是顺着晶片主弦方向右漂移,为了计算方便,通常认为漂移方向大致成45°角,漂移量与外延层厚度相同。因此,只需在版图设计时,将刻蚀隔离区时的刻蚀标记向左移动外延层尺寸的量,即能校正埋层漂移效应,这个方案已经在实际工艺中应用,并通过了产品验证。

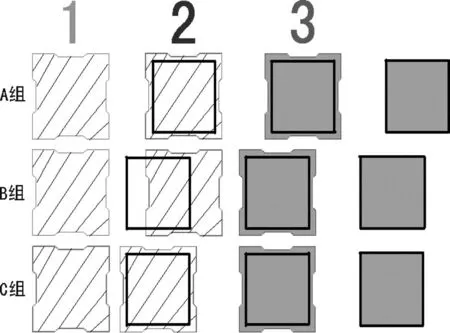

图4 光刻套偏图

图4中A组为未加校正标记的刻蚀情况,B组为未加校正标记,手动校正的刻蚀标记,C组为加完校正标记的刻蚀情况,其中1号标记为埋层,2号标记为隔离,3号标记为基区。根据前面介绍很容易得出的结论就是:A组标记虽然基区标记看似套准关系,但实际工艺中会造成图3所示的隔离不透的现象;而B组手动校准方式虽然可以满足结果要求,但是增加了工艺过程中的复杂度,而且认为操作易引入误差;所以工艺中最优化的选择是在设计版图时就考虑埋层漂移的影响,进行埋层图形漂移校正。

4.2 工艺中添加埋层校正的原则

但是需要指出的是,并不是所有电路在工艺实现中都要采用校正方案。例如,设计规则中埋层与隔离之间的尺寸很宽富,即使在未校正的情况下,正常的隔离工艺完成后,埋层也不会与隔离岛相连,就可以不采用漂移校正方案。但是随着技术发展,对器件尺寸的要求越来越高,因此设计规则会越来越苛刻,即必须采用漂移校正方案,否则,两个岛间的NPN管集电极全部相连会造成功能失效。

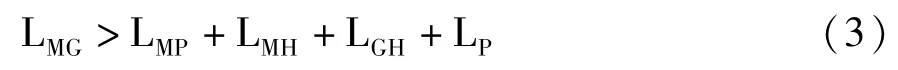

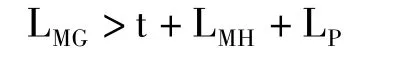

4.3 “埋层—隔离”平面设计的计算

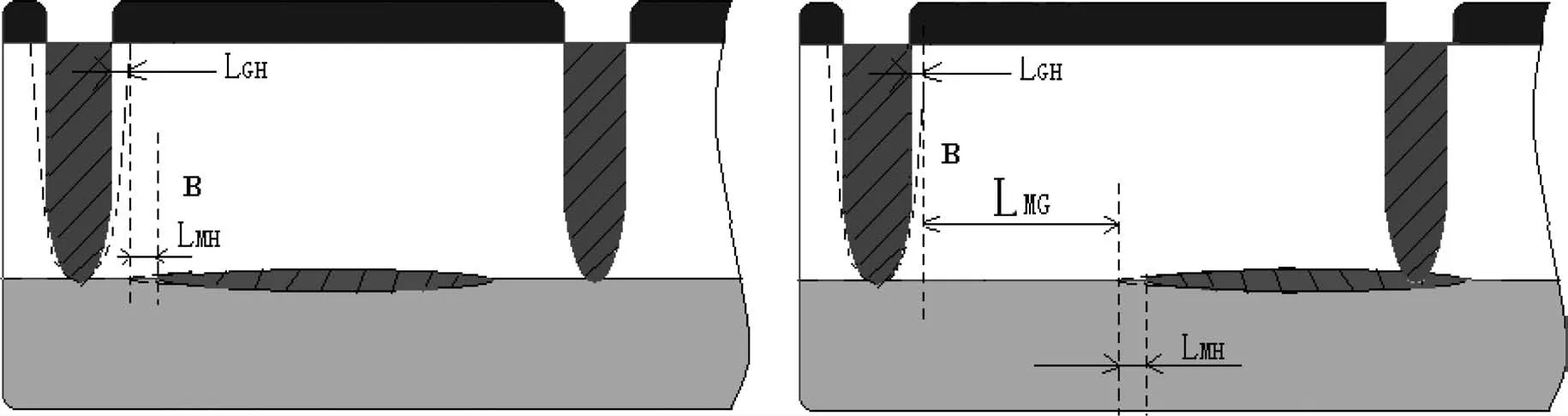

为了方便计算,首先将几个参数进行定义,在设计规则中所讲的“埋层-隔离”间距用LMG表示,影响这个参数的主要因素有三个方面:埋层漂移量(LMP)、埋层横向扩散量(LMH)和隔离槽横向扩散量(LGH),如图5所示标注。

不采用漂移校正方案的LMG设计值为

采用漂移校正方案,LMG设计值为

图5 “埋层—隔离”平面设计原理图

由此可以看出,只有LMG最终余量大于零的情况下,隔离才能成功。

在实际工艺中,光刻套准精度会引入偏差Lp,隔离扩散工艺条件的控制会使LGH和LMH产生浮动。

因此,最终LMH设计值应为

由于埋层杂质一般采用As作杂质源进行注入,由于As的活性差,LMH很小,几乎不到1μm。硼扩散方程式及工艺生产经验的横向扩散LGH约和纵向的t相等,同型外延埋层漂移量LMP和外延层厚度t相等。代入以上当量,即为

若采用漂移校正方案,则

综上所述,随着技术的发展需要,管芯尺寸在不断缩小,同时成品率的要求在不断提高,采用漂移校正能够获得更大的产品利润。

5 隔离击穿电压测试分析

介绍一些工艺过程中击穿测试的相关内容,因为实际工艺过程中,需要根据击穿测试的图形形貌,来判断隔离效果。一般隔离测试时,主要有四种现象[3]发生,分别是隔离透、隔离不透、击穿电压低、击穿电压软,具体情况如图6所示。

图6 隔离击穿电压曲线图

(1)隔离成功:击穿电压BVCSO具有较高值,击穿曲线在小电流下仍然很硬(棱角分明),如图中所示的曲线Ⅰ。

(2)隔离不透:有两种情况,一是有漏电流,有正常的棱角分明的击穿电压,如图所示曲线Ⅱ;二是无击穿电压,如曲线Ⅲ。

情况一是由于工艺条件产生偏差,隔离槽杂质并未按工艺条件扩散到设计要求的衬底深度。当两岛加低压时呈现击穿现象。这时的情况与栅极浮偏的场效应晶体管的工作原理是类似的。开始小电压时电流从n型“沟道”流过,随着电压的增加,p型隔离墙及p型衬底与n型外延层之间的pn结势垒区将不断扩宽,当电压大到一定值时,两势垒区相接,这就相当于“挤没了沟道”,而显示出pn结特性,pn结击穿。若工艺中出现此情况,可以继续推P+杂质,当P+杂质与P-衬底相通时,漏电流就会消失,隔离成功。

无击穿电压的情况,有两种导致它的可能。一是由于氧化层太薄,使得隔离失效。隔离扩散时未能完全起到掩蔽作用,使有氧化层保护处的外延层表面也形成了一薄层p型层,这称之为穿通。为了避免这一现象,隔离扩散前的氧化层要足够厚。此外隔离光刻时由于光刻掩模上某隔离条断开,或是光刻时隔离条上某段氧化层并未刻去,则在隔离扩散时这一局部区域就未扩进P型杂质而仍为n型,这样虽然整个硅片已扩透,由于这局部n型区域的连通作用而没有击穿电压。

但在相对成熟的工艺线上这样导致隔离失败的可能性非常小,而更可能的是前面所述的P+区域由于N+埋层漂移,与之相通,使两邻近岛区通过N+埋层相通,无击穿电压。

(3)击穿电压BVCSO很低,如曲线Ⅳ

主要问题是出在埋层与P+隔离槽上,当间距很小时,正常加扫描电压时曲线是平直的无任何电流。当扫描电压加大,N-区电场强度加大时,由于P+区与埋层N+区域空间电荷相互扩散,产生电流,提前击穿。

若出现该问题,判定是否隔离成功,还要取决于设计规则及工艺方案。如果埋层无漂移校正,LMG>2t+LMH+LP,隔离推进程度不够,使得P+杂质区在N+杂质区上表面发生该现象,会有低击穿电压现象。如果LMG>t+LMH+LP,则是在N+区侧面发生该现象。解决该问题主要调整LMG使得余量较大些,能较好解决。

(4)击穿电压软现象,见曲线V

主要是由于表面处理问题,杂质污染,在漂洗过程中,漂洗中含有其它杂质,吸附到硅片表面,使得击穿曲线棱角不分明,软击穿现象Ⅴ。

[1] 孙俊人.电子工业生产技术手册(半导体与集成电路卷7硅器件与集成电路)[M].北京:国防工业出版社,1989.

[2] 杨树人,丁墨元.外延生长技术[M].北京:国防工业出版社,1992.

[3] 孙俊人.电子工业生产技术手册(半导体与集成电路卷6半导体材料)[M].北京:国防工业出版社,1989.

Research on Pattern Shift Process in IC Process

Song Lingling1,Li Hao2,Wang Libin2

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.Troop 93271,Shenyang 110032,China)

The phenomenon,buried layer graphics drifting on the layers,is decided by the characteristics of extensional structure,which will cause damage to process and result in product failure.In the process,a certain principle of correction is usually used to offset the effect of drift.In addition,the test and analysismethods of Isolation breakdown voltage is also described in this paper.

Epitaxial;Drifting;Correction

10.3969/j.issn.1002-2279.2015.01.007

TN405.95

A

1002-2279(2015)01-0019-03

宋玲玲(1982-),女,河北深州人,工程师,硕士研究生,主研方向:微电子学与固体电子学。

2014-03-21