FPGA中的多标准IO端口设计

2015-08-07郭滨

郭 滨

(中国电子科技集团公司第四十七研究所,沈阳110032)

FPGA中的多标准IO端口设计

郭 滨

(中国电子科技集团公司第四十七研究所,沈阳110032)

现场可编程门阵(FPGA,Field Programmable Gate Array)是可编程逻辑器件的一种,已广泛运用于通信领域、消费类电子和车用电子。I/O端口模块是FPGA中最主要的几个大模块之一,它的主要作用是提供封装引脚到CLB之间的接口,将外部信号引入FPGA内部进行逻辑功能的实现并把结果输出给外部电路,并且根据需要可以进行配置来支持多种不同的接口标准。FPGA允许使用者通过不同编程来配置实现各种逻辑功能,在I/O端口中它可以通过选择配置方式来兼容不同信号标准的I/O缓冲器电路。

现场可编程门阵列;输入/输出;I/O标准

1 引 言

FPGA(Field Programmable Gate Array)即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA能完成任何数字器件功能,上至高性能CPU,下至简单ASIC电路,都可以用FPGA来实现。利用FPGA,工程师可以通过传统的原理图输入法,或是硬件描述语言自由设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用FPGA在线修改能力,随时修改设计而不必改动硬件电路。使用FPGA来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。FPGA的这些优点使得FPGA技术在90年代以后得到飞速发展,同时也大大推动了EDA软件和硬件描述语言(HDL)的进步。

FPGA包括3个大模块和若干小模块。3个大模块指:①可配置逻辑模块CLB(Configurable Logic Block);②输出输入模块lOB(Input Output Block);③内部连线(Interconnect)。

这3部分占据了整块芯片90%以上的面积。此外,FPGA还包括一些周边电路,如配置电路模块、边界扫描/回读模块、DLL时钟控制模块、上电复位模块、电压补偿模块等,它们大多分布在芯片边界,共同完成FPGA功能。

2 I/O模块设计

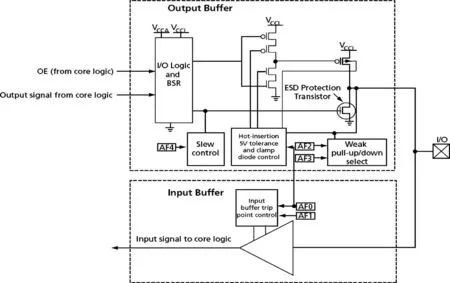

每个IO端口可以被配置成输入、输出、三态输出的双向端口。每个IO端口可以使用相同的电源电压,配置成独立端口。如图1,是一个IO电路。输出使能信号(OE),可以使信号从内核电路经过输出缓冲器输出给外部端口。输出缓冲器包含ESD保护电路。每个IO还包含一个可编程的斜率控制器,上拉下拉电阻控制器,支持热插拔,支持5V耐受,钳位二极管控制电路。图中AF0,AF1,AF2, AF3,AF4是可编程的反熔丝点选择器。根据图1,IO端口由输入缓冲器和输出缓冲器组成。输入缓冲器的作用就是由IOB PAD上接收到外部信号,并把这个信号的IO标准转换为可供FPGA内部逻辑模块(主要是CLB)使用的电平信号,使转换后的信号电压波峰值为片内核心电压。输出缓冲器就是把FPGA内部逻辑实现后输出的结果转换为符合各IO标准的输出,其中输出电压,摆率,电流关系等都要和对应的标准符合。

图1 I/O模块

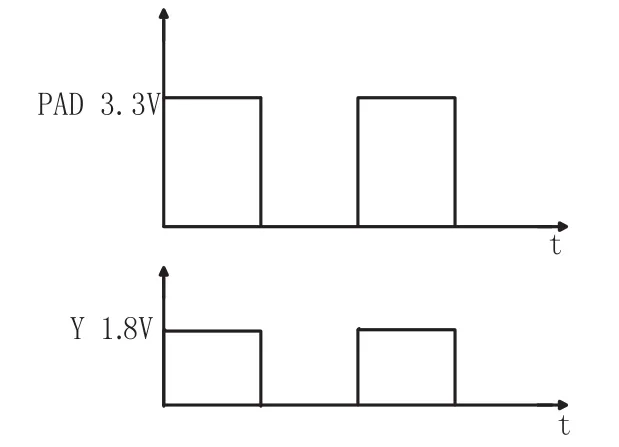

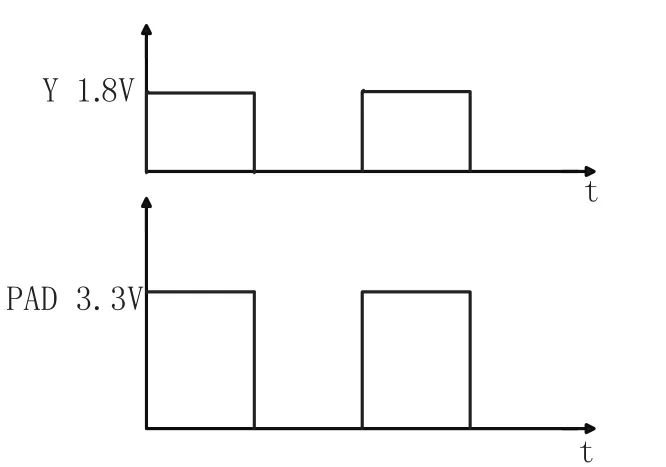

对图1中IO电路进行仿真,内核电压vcca=1.8V,IO电压vcci=3.3V,首先把使能信号配置成输入IO,给IO一个高电平为3.3V、低电平为0V的方波,经过内核从Y输出,输出一个高电平为1.8V,低电平为0V的方波,如图2所示。再把使能信号配置成输出IO,从内核输入一个高电平为1.8V,低电平为0V的方波,经过IO,从PAD输出一个高电平为3.3V,低电平为0V的方波,如图3所示。这就实现了IO的电平转换。

图2 输入IO

图3 输出IO

3 多标准IO电路单元模块的实现

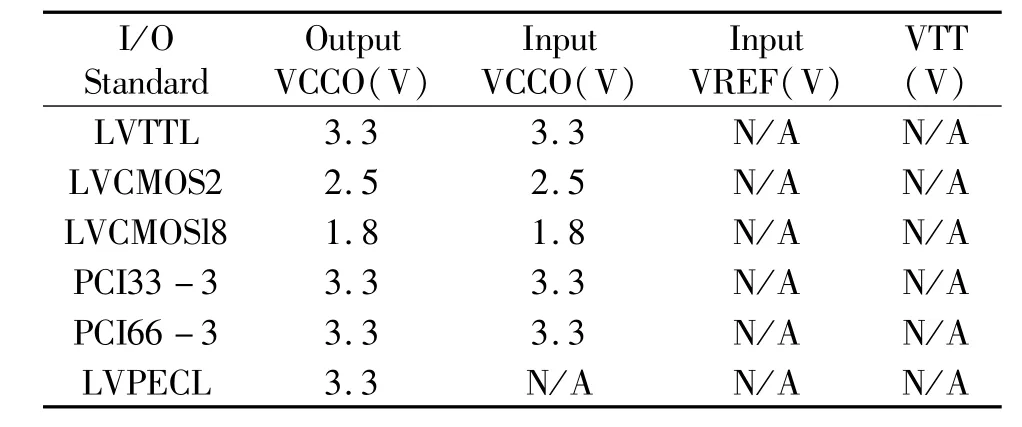

FPGA中I/O接口的主要作用是提供封装引脚到CLB之间的接口,将外部信号引入FPGA内部进行逻辑功能的实现并把结果输出给外部电路,并且根据需要可以进行配置来支持多种不同的接口标准。例如Virtex.E型号FPGA中高灵活性的Select I/O技术一共支持了多种高性能接口标准。如表1所示。

表1 Virtex.E型号FPGA支持的IO标准

因为I/O电路主要作用是为数字逻辑电路(CLB)提供输出驱动能力与输入驱动能力的一个接口电路,如果没有该电路,那么数字电路的输出将只有一个电压标准(芯片工作电压),而且也不能满足外部驱动能力的要求。因此所谓不同的接口标准,实际上体现在I/O上就是不同接口标准对输出电压与输出电流大小的要求不同,I/O接口电路显然不能简单的用一个Buffer缓冲器来代替。根据表1可以得知Virtcx.E的I/O需要支持多种不同的接口标准,而Virtex.E仅仅是Virtcx系列比较早期的型号,越为先进的型号,它们支持的I/O标准数量越多。为了适应越来越繁多、层出不穷的I/O标准,FPGA的多标准IO接口模块设计必须遵循一个核心思想:不去考虑各种不同接口协议的具体编码规则,而是着重于不同接口协议的电气特性参数有哪些不同。不同I/O标准的电压、电流要求不同。

4 结束语

从总体结构出发,将FPGA中的I/O电路分为三大部分,即用于储存配置信息和实现I/O可编程的阵列、I/O布线矩阵资源以及I/O电路多标准兼容功能实现模块。其中多标准I/O兼容模块分为触发器模块、输入缓冲器模块和输出缓冲器模块。针对各种单端I/O输入/输出标准,自上而下设计了它们的电路。此电路具备很好的灵活性,可通过编程使电路能够兼容多种标准的单端标准和伪差分标准。同时,此电路也具备很好的可扩展性。最后提出了I/O接口电路的测试方案,以验证设计的可实现性。

[1] R Jacob Baker,Harry W Li,David E Boyce.CMOS:circuit Design,Layout,and Simulation[M].北京:机械工业出版社,2003.

[2] [美]尤耶缪拉(Uyemura,J.P.)著.超大规模集成电路与系统导论[M].周润德,译.北京:电子工业出版社,2004.

[3] 朱明程,熊元姣.ACTEL数字系统现场集成技术[M].北京:清华大学出版社,2004.

Design on Multi-Standard I/O Ports in FPGA

Guo Bin

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

FPGA(Field Programmable Gate Array),as an type of programmable logic devices,has been applied in the fields of communication,consumption electronics and automobile electronics.I/O Blocks is one of themost importantmodules in FPGA,which provides the interface between the package pins and CLBs,receives exterior signals for implement the logic functions in FPGA and exports the result to exterior circuit.The signals can be configured to support different I/O standards according to the requirements.In I/O Blocks,I/O output/input buffer circuit is compatiblewith different I/O standards by configuration.

FPGA;Input/Output;I/O standard

10.3969/j.issn.1002-2279.2015.01.003

TN4

A

1002-2279(2015)01-0007-03

郭滨(1982-),女,河北省吴桥县人,学士,主研方向:IC设计。

2014-03-21