一种基于FPGA的信号发生器研究与设计

2015-08-07孔德鹏毛惠丰姬占涛

孔德鹏,毛惠丰,姬占涛

(西安工程大学电子信息学院,西安710048)

·大规模集成电路设计、制造与应用·

一种基于FPGA的信号发生器研究与设计

孔德鹏,毛惠丰,姬占涛

(西安工程大学电子信息学院,西安710048)

基于数字频率合成技术,生成数字化正弦波,采用模块化设计和查表的方法实现。直接数字合成技术是一种先进的电路结构,能在全数字下对输出信号频率进行输出,在精度、灵活性上大大超越了模拟信号发生器。在Quartus II环境下,用超高速集成电路硬件描述语言编程,进行模块化设计。使用ALTERA公司提供的EP1K30TC144-3芯片作为核心器件进行设计,来实时生成数字化波形,结合GW48-CK实验开发系统,最终给出了信号发生器的设计方案。

现场可编程门阵列;直接数字合成技术;模块化设计;查表法

1 引 言

传统的信号发生器是使用模拟电路或者专用芯片搭建而成,存在频率不高,稳定性较差,且不易扩展和调试的缺陷。

数字化波形技术的应用越来越广泛,例如正弦波信号发生器,正弦波振荡器,正弦波逆变器等。数字正弦波的精度高,误差小,在工业应用中比模拟电路产生的正弦波更稳定,更精确。设计一种以FPGA为基础的数字化波形信号发生器。该方法采用直接数字合成技术,改变了以往的设计思路,在精度、灵活性上大大超越了模拟信号发生器。随着可编程逻辑器件FPGA的迅速发展,基于FPGA控制的信号发生器使得电路设计更加简单和精确。

以此产生的波形信号为其它系统提供波形,它是各类波形发生器和信号源的基础,采用FPGA结合简单电路就可以实现输出正弦波或三角波,可以很方便的改变频率大小,具有电路结构简单、工作频率稳定度高、频率调整精度高等特点,该设计也可以直接拓展到其它领域的电路中。

2 正弦波信号的产生方法概述及原理分析

2.1 正弦波信号的产生方法概述

工程实践中常用的正弦波信号生成方式有以下两种。方式1,使用模拟电路或者专用芯片搭建而成,可以产生方波,正弦波,三角波,通过调整外部元件可以改变输出频率。但是采用模拟器件分散性大,存在频率不高,抗干扰能力差,成本也较高且不易扩展和调试的缺陷。方式2,由单片机来完成。单片机功能强大,集成度高且其设计和控制比较容易。但是由于单片机设计系统中需使用许多分立元件组成单片机的外围电路,因此系统复杂,随着采用数据的增加,需要占用系统很多存储资源,复杂的运行过程容易出现死机或进入死循环,可靠性降低。

基于FPGA的正弦波信号发生器的设计方法可以实现三角波和正弦波的数字化处理,将一个周期内的采集点存储起来,生成频率和幅值都可调的正弦波或者三角波,再通过D/A转换和滤波电路便可得到模拟波形。该方法编程简单,实现灵活。

2.2 基于FPGA的正弦波产生原理

图1给出了基于FPGA的正弦波发生器的组成示意图。系统由4部分组成:波形发生控制电路,波形数据ROM,D/A转换和滤波电路。波形发生控制电路由FPGA来完成。FPGA波形发生控制电路通过输入控制信号和高速时钟信号,向波形数据ROM发出地址信号。波形ROM中存有发生器的波形数据。取出采样点的幅值就可以产生数字化的波形。

图1 波形发生器组成示意图

正弦波在一个周期内的波形可以通过数字采样实现,即用N个幅值离散的等间隔采样点表示。如图2为正弦波采样的原理示意图,设周期为T,采样点数为N,采样间隔为△t,T=N*△t,那么就可以得到图示的数字信号。要改变频率只需要改变采样时间间隔,由于采样点数N不变,N=T/△t,因此△t越小,T就越小,对应的频率就越大。

D/A转换器负责将FPGA中ROM输出的数字量数据转换成模拟信号量,再经过滤波电路后,输出就是所要得到的需要波形。输出波形的频率上限与D/A器件的转换速度有重要关系。本实验采用DAC0832器件。

图2 正弦波采样原理示意图

3 基于FPGA信号发生器的模块化设计

FPGA的模块化设计就是按照一定规则把系统划分成若干模块,然后对每个模块分别进行设计,并将结果约束在预先设置好的区域内,最后将所有模块有机的组织起来完成整个系统设计。下面对需要设计的模块进行介绍。

3.1 FPGA的输入输出模块

输入模块采用按键输入,同时通过按键来改变波形和频率。输出端口输出八位二进制码,代表数字化的正弦波形。输出受内部程序控制,通过FPGA与DAC0832的互联接口输出模拟波形。

3.2 波形发生模块

由于波形发生控制器和波形数据ROM都是利用硬件描述语言VHDL编程实现的,所以统称为波形发生模块。波形发生模块包括频率设置、正弦波/三角波切换进程。

具体ROM模块生成步骤如下:

(1)建立.mif格式文件

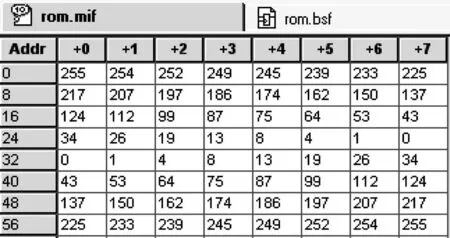

在Quartus II的ROM数据编辑窗口中建立.mif或.hex格式文件,然后将波形数据填入mif文件表中,如图3所示,波形数据mif表格。在表格中输入正弦波形数据,表格中的数据为10进制形式,任一数据(如第三行的99)对应的地址为左列数与顶行数之和)。共64个波形点。

图3 波形数据mif表格

(2)定制ROM元件

根据需求设置Mega Wizard Plug-in manager,根据设置得到ROM模块的外部原理图,即ROM模块的结构。如图4所示,并且生成相应的ROM模块VHDL程序。

图4 ROM的外部原理图

(3)验证ROM模块的正确性

为了验证正弦波波形数据的正确性,在应用ROM模块之前,首先对定制的ROM模块进行仿真,使其符合我们的设计要求。仿真数据如图5所示。

图5 ROM数据仿真输出波形

3.3 D/A转换模块及滤波电路

D/A转换器负责将ROM输出的二进制数字信号换成模拟信号,再经滤波电路后输出。DAC0832是8位D/A转换器,转换周期为1μs,其引脚信号可以直接与FPGA目标芯片相连。它典型的接口方式如图6所示。其参考电压与+5V工作电压相接。

滤波电路采用简单的RC滤波就可以达到要求。

4 基于FPGA的信号发生器程序设计

软件设计分为三个进程。正弦波/三角波切换进程,频率设置进程,以及波形数据ROM。如正弦波,分为64个采样点,最高采样点值为255,对应的八位二进制数为11111111。通过给输入信号设定值,改变内部采样时钟脉冲的时间△t,让FPGA取出波形数据ROM中的采样点数据,设定值的大小直接影响采样速率,使得输出的波形频率产生变化。

结合所有设计需要和期间内部资源,进行软件程序设计,程序流程图如图7所示。

程序初始化后,通过按键输入,可以按键设置频率,切换输出三角波或者正弦波。实现预设功能。

5 实验结果分析

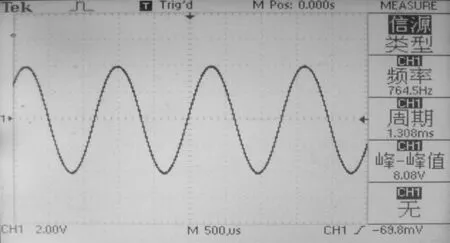

连接示波器到DAC0832输出口DOUT,调节示波器各项参数设置,进行测试。根据示波器的显示,可以直观的观察波形频率、周期以及幅值大小,和软件仿真结果对比,验证实验结果的正确性。以下是示波器观察得到的波形图。

设置输入键1,2位为00时,即输入data为00000000,观察到的波形如图8所示。

图6 DAC0832接口电路

图7 软件设计流程图

图8 输出频率最小的波形图

设置输入键1,2位为FE时,即输入data为11111110,观察到的波形如图9所示。

图9 输出频率最大的波形图

由图8所示,图中输出的最小频率为764.5Hz,周期最大为1.308ms。同样,由图9所示,图中输出的最大频率为98.04KHz,周期最小为10.20μs。

在相同条件下进行对比,时钟CLK都为50MHz,进行软件仿真与实验对比,结果如表1所示。

表1 软件仿真与实验对比

输出频率最小时刻,仿真与实验误差在1.15Hz,误差精度为0.001。输出频率最大时刻误差在0.38KHz附近,误差精度为0.0038。

通过按键实现波形在正弦波和三角波之间的切换,下图为波形切换为三角波输出时的波形图,如图10所示。三角波的频率变化和正弦波一致。波形切换可以在任意时刻进行。

图10 三角波波形

6 结束语

在研究基于FPGA的数字化信号发生器设计的基本原理及其优缺点的基础上,给出了相关的仿真结果与最终的实验结果。仿真与实验结果表明,该方法具有简单、可靠、精度高、可移植性好等优点,具有一定的工程实践价值。

在实验测试时,低频段波形输出比较正常,输出频率达到高频(f>20KHz)段时,波形输出幅值开始衰减,频率越大,幅值衰减越严重。

[1] 赵艳华,曹丙霞,张睿.基于Quartus II的FPGA/CPLD设计与应用[M].北京:电子工业出版社,2009:172-184.

[2] 周俊峰,等.基于FPGA的直接数字频率合成器的设计和实现[J].电子技术应用,2002(4):28-30.

[3] 曾云,韩顺锋.基于FPGA的DDS信号源设计及误差分析[J].舰船电子工程.2009(2):72-74.

[4] 蔡丽,翟晓东,高红云.基于FPGA技术的多功能信号发生器设计[J].仪表技术,2007(8):16-20.

[5] 田大方,祝忠明.一种基于FPGA的信号发生器的设计方法[J].电子质量,2012(4):27-30.

Design and Research of Signal Generator Based on FPGA

Kong Depeng,Mao Huifeng,Ji Zhantao

(School of Electronic Information,Xi’an Polytechnic University,Xi’an 710048,China)

Based on the digital frequency synthesis technology,the digital sine wave is generated by modular design and look-up tablemethod.The direct digital frequency synthesis technology,as a kind of advanced circuit structure,can output in full digital signal frequency.So it ismuch better than the analog signal generator in precision and flexibility.In the circumstances,Quartus II,with very-highspeed integrated circuithardware description language,themodular design is conducted by programming.EP1K30TC144-3 chip from ALTERA,as the core component,is used formicrochip design to generate digital wave in real-time.Combining with the experiment development system GW48-CK,the signal generator design scheme is finally provided.

Field programmable gate array;Direct digital frequency synthesis technology;Modular design;Look-up table

10.3969/j.issn.1002-2279.2015.01.001

TP346

A

1002-2279(2015)01-0001-04

孔德鹏(1990-),男,安徽省阜阳市人,硕士研究生在读,主研方向:数字PWM控制技术,伺服控制。

2014-06-27