VxWorks下串行RapidIO总线驱动的实现

2015-01-27王璐,龚俊

王 璐,龚 俊

(中国兵器工业第五八研究所,四川 绵阳 621000)

0 引言

随着高性能嵌入式系统的不断发展,数据传输能力和信号处理能力也在不断的提高。但与处理器内核性能的增长速率相比,总线频率的提升仍然滞后,且两者之间的差距在不断扩大。处理器性能的提升已无法满足处理器间或处理器与外设间高速通信的需求。因此,需要新兴的高性能总线互连技术来满足系统互连通信的更高要求[1]。

RapidIO 是新一代高速互连技术,已于2004 年被国际标注化组织(ISO)和国际电工协会(IEC)批准为ISO/IEC DIS 18372 标准。RapidIO 技术主要面向高性能嵌入式系统的互连通信,可在4 对差分线上实现10Gbps 的有效传输速率,而且具有比万兆以太网、PCI express 更高的传输速率[2]。RapidIO 互连定义包括两类技术:一类是面向高性能微处理器及系统互连的并行接口;另一类是面向串行背板、DSP 和相关串行控制平面应用的串行接口。

1 RapidIO 互连技术简介

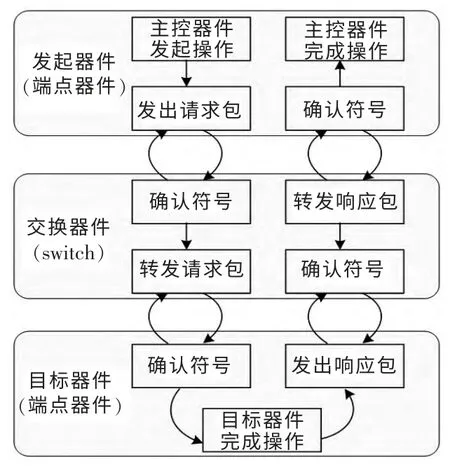

RapidIO 采用三层分级体系结构,即逻辑层、传输层和物理层:①逻辑层:最高层,定义了全部协议和包的格式,为端点器件发起和完成事务提供必要的信息;②传输层:中间层,定义了交换器件如何将传输的数据包路由到目标器件,即定义了设备ID 路由方法;③物理层:最底层,定义了相邻处理单元之间的电气连接,描述器件级接口规范。例如:包传输机制、流量控制、电气特性和低级错误管理等内容[3]。分层结构如图1 所示。

串行RapidIO 的传输操作基于请求和响应,数据包(packet)是消息传递的基本通信单元。RapidIO 系统一般由端点器件和交换器件组成,每个器件由唯一的设备ID标识。端点器件产生或接收数据包,交换器件实现数据包在各端点间的路由和传递,不对数据包做解析。图2是传输操作的流程图。首先由发起器件产生一个传输请求,请求包被传输到相邻的交换器件,通过交换器件这个请求包被完整的转发到目标器件。目标器件根据请求完成相应操作后,发送相应的响应包,经过交换器件传回到发起器件。至此一个完整的传输过程完成。

图1 RapidIO 体系结构图Fig.1 Structure diagram of RapidIO system

图2 RapidIO 传输操作流程图Fig.2 Flow chart of RapidIO transmission

2 RapidIO 互连系统平台简介

RapidIO 互连系统采用Freescale 公司的MPC8548 处理器作为端点器件,一端设置为主设备,另一端设置为从设备。采用IDT 公司的Tsi578 芯片作为交换器件,使能其中两个端口并设置为1×模式,波特率为3.125 Gbps。RapidIO 硬件平台互连示意图如图3 所示。

图3 硬件平台互联图Fig.3 Interconnection diagram of hardware platform

MPC8548 处理器内部具有PowerPC e500 的内核以及CPM 通信处理模块,内部的时钟频率为1GHz。除此之外,还集成了RapidIO 控制器,其中1×/4×串行通道的传输速率可配置为1.25Gbps、2.5Gbps 或3.125Gbps,消息单元支持存储地址寄存器最大长度4KB 的消息[4]。

Tsi578 芯片是Tundra 公司推出的RapidIO 交换产品,后并入IDT 公司,该芯片基于RapidIO 1.3 规范,共有16 路串行通道,可以灵活配置为8×4 或16×1 的端口工作方式,端口数最多可以配置为16 个,芯片内部交换带宽达到80Gbps,提供无阻塞的全双工交换能力。高性能的SerDes 通道可以实现单路1.25Gbps、2.5Gbps或3.125Gbps 的传输速率[5]。

本系统软件采用VxWorks 嵌入式实时操作系统[6],由windRiver 公司研制,使用wind 内核,具有高效的实时任务调度、中断管理、实时的系统资源和任务通信等功能,内核精简并且可高度裁剪、高效、稳定并具有良好的可移植性,专门用于对实时性要求较高的硬件设备。

3 RapidIO 总线驱动的设计与实现

RapidIO 总线驱动包含:本地设备初始化、网络配置、消息传递这三个部分基本功能。

3.1 本地设备初始化

本地设备初始化首先要初始化MPC8548 处理器内部的RapidIO 控制器和使能端口,这是进行RapidIO 通信的基础。其次要配置TLB 表,申请本地设备地址空间。最后要创建维护窗口,用以完成维护读/写操作。其中,维护窗口的建立及维护读/写函数实现如下:

(1)建立维护窗口:

STATUS rioSetupMaintenanceWindow (UINT32 rioBase,UINT16 deviceID,UINT8 hopCount,UINT32 offset, UINT32 window);

(2)维护读操作:

STATUS rioMaintenanceRead(UINT16 targetId, UINT8 hopCount,UINT32 offset,UINT32 *data, UINT32 window);

(3)维护写操作:

STATUS rioMaintenanceWrite(UINT16 targetId, UINT8 hopCount,UINT32 offset,UINT32 data, UINT32 window);

3.2 网络枚举与配置

网络枚举与配置包含了枚举网络设备、分配设备ID、维护路由表以及地址空间映射等主要功能。

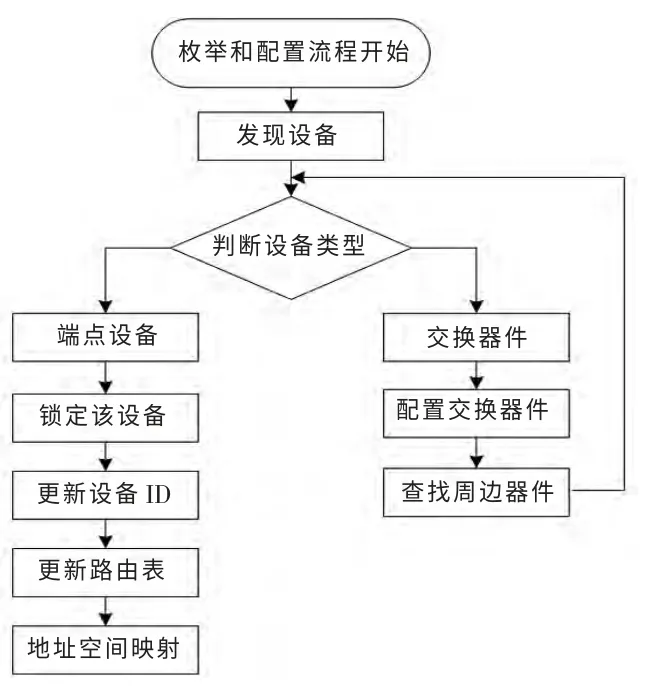

端点器件(主设备)在完成本地初始化后,要进行RapidIO 网络的枚举与配置。需要查找与之相连的端点器件(从设备),并通过读取制造商ID 判断是端点器件或交换器件。若为端点器件,首先要锁定此设备,表明主设备即将要对它进行配置;其次要将此从设备ID 由0xFF 更新为RapidIO 网络设备ID 编号;再次要更新路由表,指明主设备通过交换器件到该从设备的路径;最后要进行地址空间映射,为主设备访问该从设备做好准备。主要枚举和配置流程如图4 所示。

路由表维护函数实现如下:

图4 枚举与配置流程图Fig.4 Flow chart of enumerate & configuration device

(1)添加路由项:

STATUS rioAddRouteEntry ( UINT16 targetId, UINT8 hopCount ,UINT16 routeDestid, UINT8 routePort) ;

(2)获取路由项:

STATUS rioGetRouteEntry ( UINT16 targetId, UINT8 hopCount ,UINT16 routeDestid, UINT8 *routePort);

3.3 消息传递

RapidIO 的消息传递方式主要有Doorbell、Message、Nread 和Nwrite 等方式。软件中主要使用的函数实现如下:

(1)Doorbell 方式。Doorbell 消息传递方式适合传递8bit 或者16bit 的短消息,主要用于处理器间的中断。

UINT32 rioSendDoorbell (UINT16 localPort, UINT16 destId, UINT16 data);

(2)Message 方式。Message 方式最多可传输4096 字节数据。这种消息传递方式类似于以太网的传输方式,主设备不需要知道从设备的存储器状况,数据存放的位置由destId 决定的邮箱号确定。邮箱号类似于以太网协议中的端口号。

UINT32 rioSendMessage(UINT16 mbox, UINT32 destId,void *buffer, UINT32 len);

UINT32 rioReceiveMessage(UINT16 mbox, void *buf,UINT32 len);

(3)Nread 和Nwrite 方式。此种方式可直接读写从设备的存储器。数据长度在1~256 字节之间,返回的数据应进行对齐限制。

UINT32 rioDmaNread(UINT8 chan, UINT16 destId,UINT32 localAddr, UINT32 rioAddr, UINT32 byteCnt);

UINT32rioDmaNwrite(UINT8 chan, UINT16 destId,UINT32localAddr, UINT32rioAddr, UINT32byteCnt);

4 性能测试

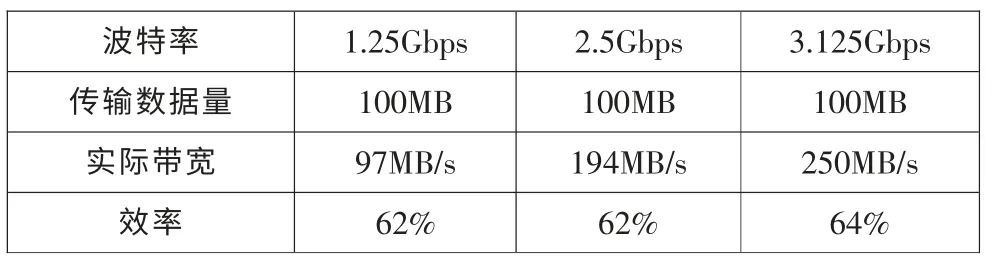

在波特率为1.25Gbps、2.5Gbps 和3.125Gbps 时,分别测算出带宽及效率。带宽的计算公式为:传输数据量/传输时间;效率的计算公式为:实际带宽/理论带宽。性能测试结果如表1 所示。

表1 性能测试结果Tab.1Theresultofperformancetest

5 结束语

该RapidIO 总线驱动采用采用VxWorks 嵌入式实时操作系统,软件设计采用模块化设计,提高了系统的可靠性和可维护性,具有高效的实时任务调度、中断管理、实时的系统资源和任务通信等功能,内核精简并且可高度裁剪、高效、稳定并具有良好的可移植性。性能测试表明,该系统满足RapiIO 高速通信需求,达到了设计要求。

[1]李鹏.基于RapidIO 的双主机节点嵌入式系统互连设计[J].电子科技,2014,4.

[2][美]Sam Fuller,等. RapidIO 嵌入式系统互连[M].电子工业出版社,2006.

[3]张强.串行RapidIO 互连系统的设计与实现[D].南京理工大学,2013.

[4]Freescale Semiconductor. MPC8641 and MPC8641D Integrated Host Processor Hardware Specifications[EB/OL]. http://www.freescale.com,2009/07/2.

[5]Tundra Semiconductor Corporatiot. Tsi578TM Serial RapidlO Switch UserManual[EB/OL]. http://www.tundra.com, 2006/10/11.

[6]Wind River Systems, Ine. VxWorks Device Driver Developer' S Guide,6.4,2006,9.

[7]张娟,苏海冰,吴钦章.基于多处理器的高速RapidIO[J].计算机工程,2014,9.