不符合20H规则的阻抗线参考层设计对阻抗测量的影响

2014-07-31苏藩春

苏藩春

(汕头超声印制板公司,广东 汕头 515041)

1 前言

20 H规则作为PCB(印制电路板)典型布线规则,随着传输信号工作频率逐步提高,其越来越被PCB设计人员采用以用来减少EMI(电磁干扰)问题。当然,PCB制造人员无法模拟20 H规则的EMI但须控制特性阻抗,故本文试图首次阐述20 H规则对特性阻抗控制的影响,并通过相关试验与量产过程进行证明。

2 20 H规则概述

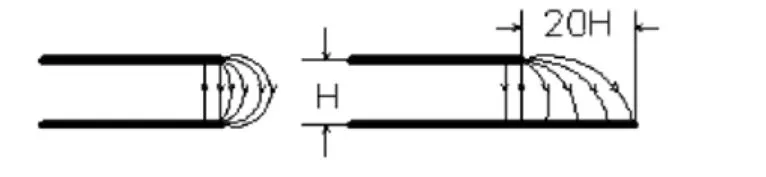

20 H规则最初是由W. Michael King提出,是减小电路板辐射的设计规则之一,但20 H规则是一条尚未得到明确证明的经验规则,目前许多学者主要是通过反射系数分析、FDTD(有限差分时域)和实际测量等方法对其影响效果进行模拟和探究。简单而言,就是因为PCB板电源层与地层之间的电场是变化的(高频设计板更为显著),在板的边缘会向外辐射电磁干扰,即平常通称的边缘效应。在PCB设计过程中,MI工程师或设计人员通常做法:将电源层内缩,使得电场只在接地层的范围内传导。理论模拟分析初步表明:以一个H(电源和地之间的介质厚度,对于特性阻抗参数设计而言,通常即为H)为单位,若内缩20 H则可以将70%的电场限制在接地边缘内,内缩100 H则可以将98%的电场限制在内;用图示简单说明如图1。

图1

PCB作业人员一般无法模拟EMI问题但需精确控制特性阻抗。故关于20 H规则与EMI问题的研究颇多,但关于20 H规则影响阻抗控制的研究较少。

3 试验过程

3.1 资料设计

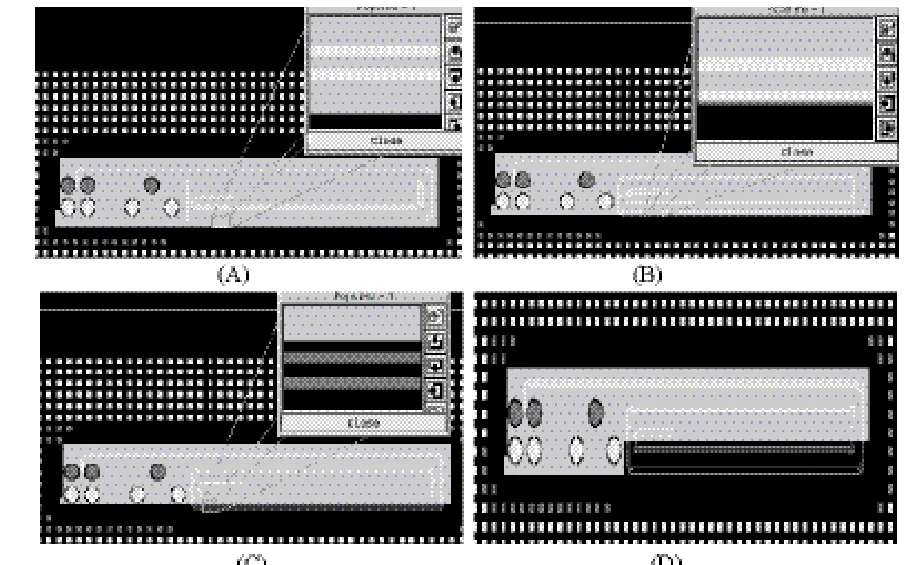

设计正常铺铜、铺铜异常的不同阻抗测试附连板,如图2所示。

图2 采取不同参考层设计的阻抗测试附连板. (A)正常铺铜设计,参考层铺铜相对于讯号线路垂直缩入0.05 mm (B)和0.5 mm (C) 以及参考层相对夸张的设计(D)

3.2 测试结果

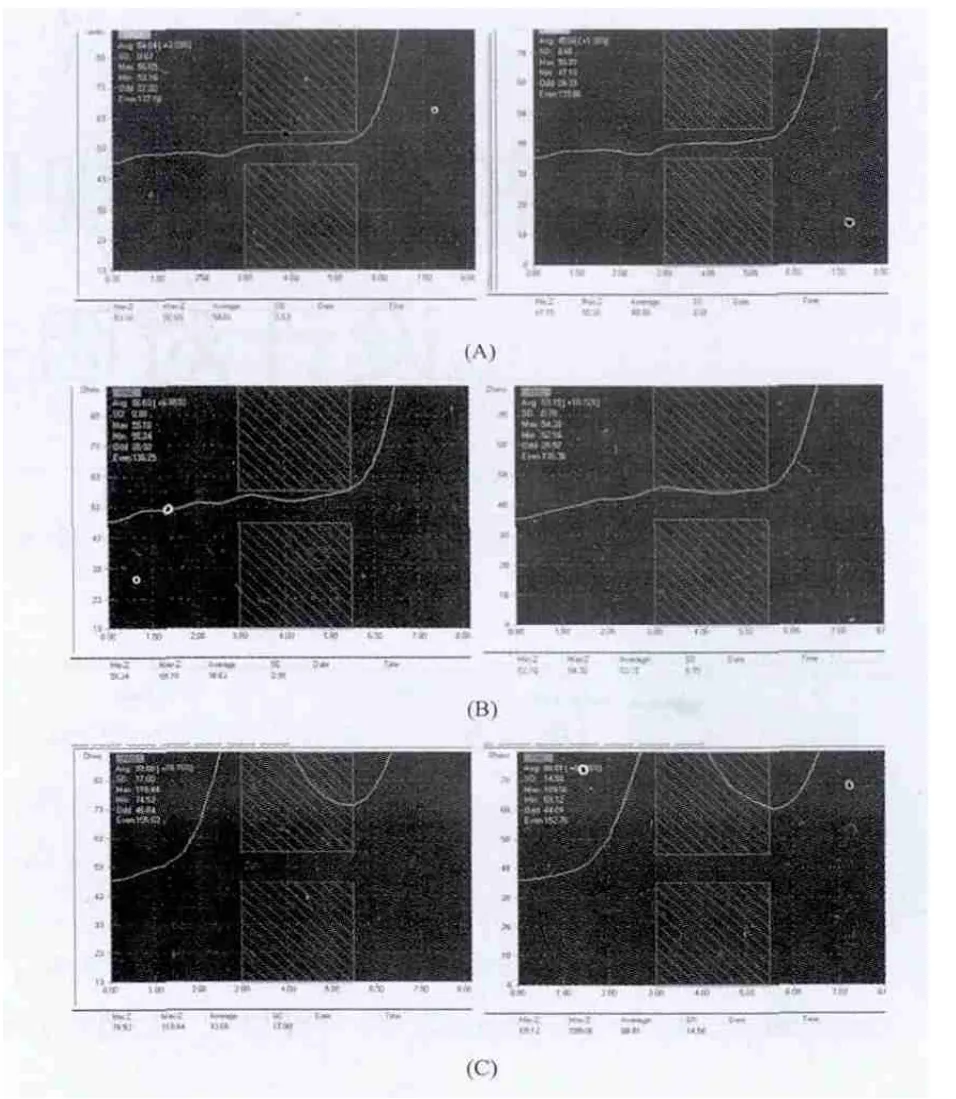

针对上述测试图形,采取Polar CITS800s TDR系统测试,从相应Testwave(测试波峰)可见,对于正常设计的A附连板,测试曲线相对光滑且阻抗值分别为54.65 W和48.66 W(图3A);当测试附连板不再满足20 H规则时,测试曲线变得不再光滑且阻抗测试值开始增大,且不满足程度越大、相应阻抗测试值变得越高,如从附连板B的56.63 W(图3B)突增到附连板D的127.2 W(图2D)。

3.3 量产验证

图3 不同测试附连板的TDR Test waveform(测试波形)

随着高速信号传输所需信号完整性的增加,PCB不仅需要保证测试附连板的阻抗控制精度,更要保证板内实际走线的阻抗控制;但板内阻抗布线环境相对复杂,下述例举部分不满足20 H规则的板内实际走线实例(图4)。与参考层垂直相切,(B)讯号线跨过且部分超出隔离环设计,(C)部分讯号线完全超出参考地层

图4 不满足20规则的设计案例。(A)讯号线边缘

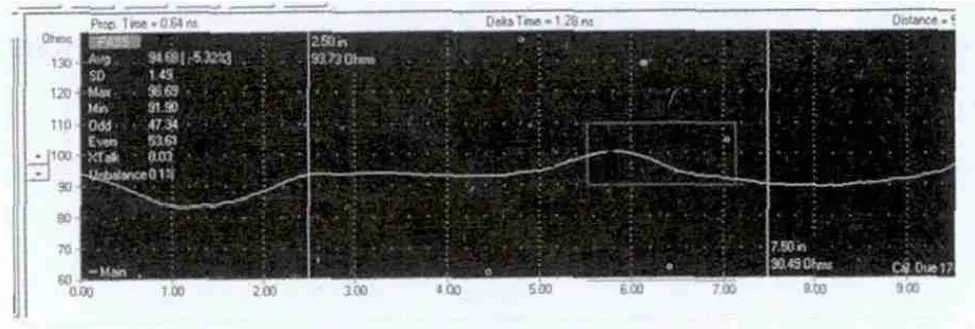

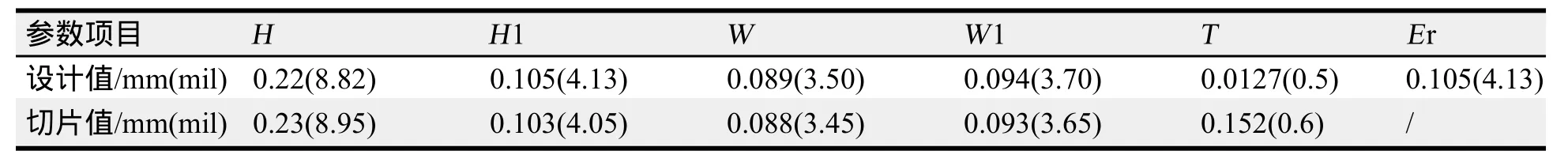

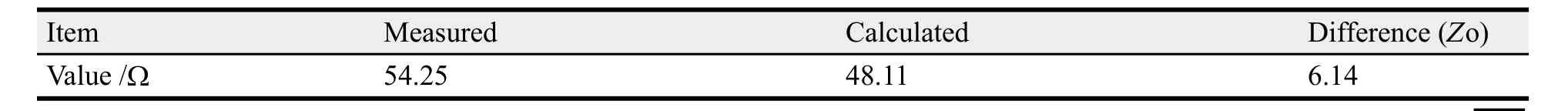

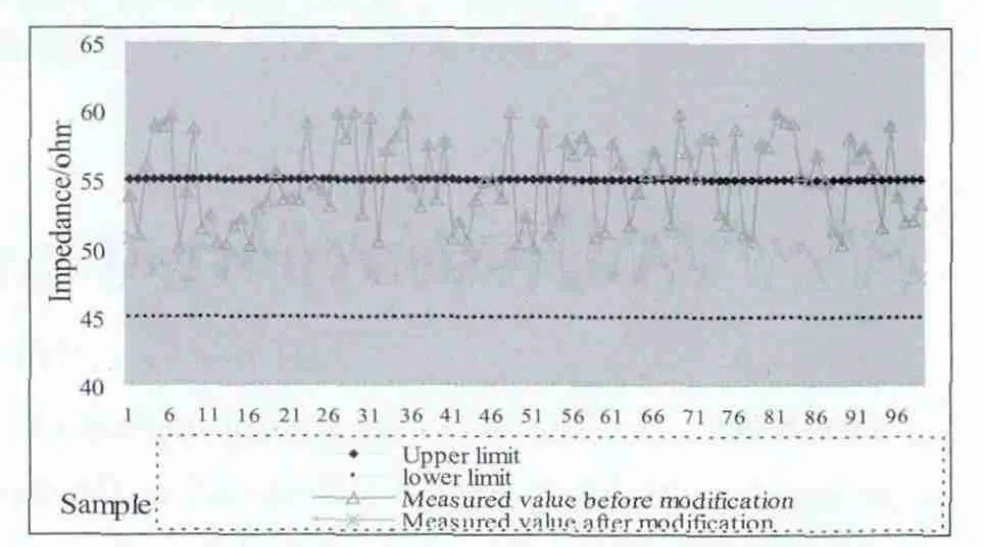

对上述实际走线采取Polar TDR测试并与基于相应讯号线的切片反算,其阻抗值差异很大,如设计案例A,尽管切片反馈各控制参数正常,但相应阻抗差异非常明显(如表1~表2所示);案例B的Test waveform(测试波峰)也表现的相对不平坦(图5);案例C的阻抗测试值更是以26%的不合格率超出相应控制范围,但将相应讯号线设计位置内移以确保参考层铺铜设计满足20 H规则,所有阻抗控制均变得相对完美,如图6所示。

图5 产品B的阻抗讯号线测试曲线示意图

3 试验结论

试验表明,PCB讯号线的TDR阻抗测试受相应讯号线的参考层铺铜是否满足20H规则影响较大;其表现结果是,参考层内缩程度越大(即越不满足20H规则),其阻抗测试值越大,阻抗测试曲线越不平坦。故建议PCB设计人员需确保相应阻抗讯号线务必满足20 H规则以利于阻抗控制和保证PCBA产品的信号完整性。

表1 50W单端阻抗设计的产品A的阻抗设计参数与实际走线切片值比对。

表2 50W单端阻抗设计的产品A的阻抗实测值与切片反算值比对。

图6 针对相同设计参数的50W单端控制的产品C,参考层是否满足20H规则设计的阻抗测试比对