高速PCB单端过孔研究

2014-07-31王红飞

王红飞 陈 蓓

(广州兴森快捷电路科技有限公司,广东 广州 510063)

1 前言

现代高速数字电路设计中,过孔对PCB信号完整性的影响不容忽视[1][2]。在高速设计中往往要采用多层PCB,而在多层板中,信号从某层互连线传输到另一层互连线就需要通过过孔来实现连接,在频率低于1 GHz时,过孔能起到一个很好的连接作用,其寄生电容、电感可以忽略。当频率高于1 GHz后,过孔的寄生效应对信号完整性的影响就不能忽略,此时过孔在传输路径上表现为阻抗不连续的断点,会产生信号的反射、延时、衰减等信号完整性问题[3]。当信号通过过孔传输至另外一层时,信号线的参考层同时也作为过孔信号的返回路径,并且返回电流会通过电容耦合在参考层间流动,并引起地弹等问题[4][5]。

目前,有关过孔研究基本是采用仿真软件来模拟过孔参数对过孔阻抗及S参数的影响[6]-[8]。这些仿真结果只能帮助设计者了解相关参数对过孔阻抗及信号完整性的影响趋势,但不能准确给出过孔参数的影响程度,难以指导实际工程设计。本研究通过采用网络分析仪测试TDR曲线方法研究了单端过孔阻抗,分析了过孔孔径、过孔长度、焊盘/反(阻)焊盘尺寸对过孔阻抗的影响;通过为过孔信号提供返回路径的方法,研究了接地孔对过孔阻抗、损耗的影响,还探讨了多余短柱对过孔阻抗及损耗的影响。

2 试验方法

2.1 主要材料与仪器

材料:不同厚度FR4覆铜板,铜厚34.3 mm/34.3 mm;各规格半固化片(106、1080、2116和3313)。

仪器:矢量网络分析仪(VNA),频宽为20 GHz。

2.2 方法

试验制作了不同层数测试板,信号过孔孔径设计值为0.20 mm ~ 0.50 mm,过孔长度设计为0.5 mm~ 2.0 mm,设计了不同尺寸焊盘、反焊盘。为研究多余短柱对过孔阻抗、损耗的影响,试验通过背钻技术,控制背钻深度获得了不同短柱长度单端过孔,过孔长度为0.20 mm ~ 0.80 mm。

试板制作流程:开料→烘板→内层干膜→内层蚀刻→内AOI→棕化→层压→钻孔→去钻污→沉铜→外层电镀→镀锡→背钻→外层蚀刻→外层干膜→图形电镀→外层蚀刻→外AOI→阻焊→沉金→铣板……

试板制作完成后采用矢量网络分析仪测试含过孔单端线的TDR曲线和S参数,通过过孔处TDR曲线变化情况获得过孔阻抗值,并通过S参数分析过孔损耗。

3 结果与讨论

3.1 过孔参数对阻抗连续性的影响

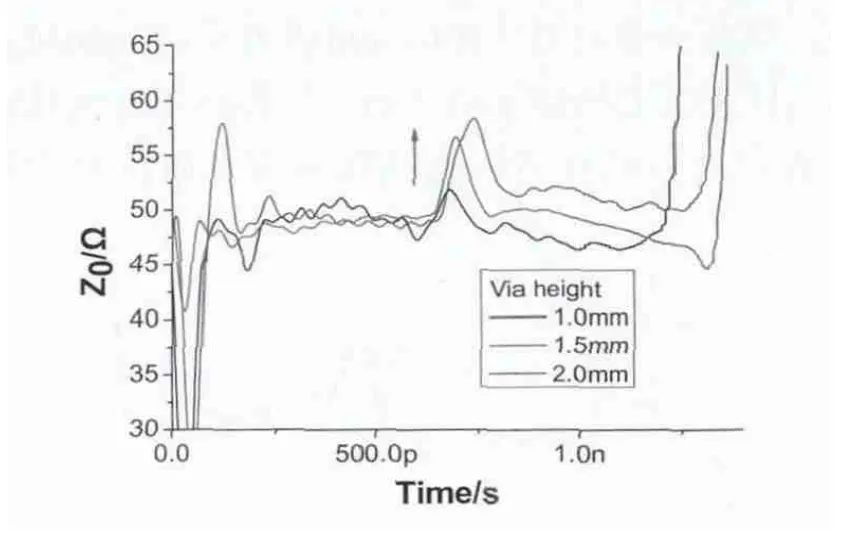

过孔长度是影响过孔电感的主要因素之一[1]。对用于顶、底层导通的过孔,过孔长度等于PCB厚度,由于PCB层数的不断增加,PCB厚度常常会达到5 mm以上。然而,高速PCB设计时,为减小过孔带来的问题,过孔长度一般控制在2.0 mm以内。这里研究了过孔长度在1.0 mm ~ 2.0 mm范围变化时,过孔阻抗变化情况(见图1)。由图看出,过孔长度由1.0 mm增加至2.0 mm时,由于过孔电感的迅速增加,导致过孔阻抗也迅速增加,即过孔长度越大,过孔阻抗不连续性越差。试验还表明,当过孔长度在1.0 mm范围内时,通过过孔参数优化,可以将过孔引起的阻抗变化控制在10%内,但过孔长度超过1.5 mm时,过孔阻抗不连续性问题变得难以解决。

图1 过孔长度对过孔阻抗的影响

图2为过孔孔径对过孔阻抗的影响。由图看出,当过孔孔径由0.20 mm增加至0.50 mm时,过孔阻抗由58.4 W降低至52.5 W。这主要是由于过孔孔径增加后导致过孔电容增加,而过孔阻抗与电容呈反比。对于过孔长度大于2.0 mm过孔,通过增加过孔孔径,可在一定程度上提高过孔阻抗连续性。当过孔长度为1.0 mm及以下时,最佳过孔孔径为0.20 mm ~ 0.30 mm。

图2 孔径对过孔阻抗的影响

图3为过孔焊盘尺寸对过孔阻抗的影响。由图看出,当过孔焊盘直径由0.45 mm增加至0.55 mm时,过孔阻抗由57.5 W降低至55.2 W。这是由于过孔焊盘尺寸增加,同样会导致过孔电容增加。由测试结果可以得出,过孔焊盘尺寸每增加0.05 mm,过孔阻抗约下降0.5 W ~ 0.7W。

图3 焊盘尺寸对过孔阻抗的影响

图4显示了反焊盘尺寸对过孔阻抗的影响。由图看出,当反焊盘尺寸由0.40 mm增加至1.2 mm时,过孔阻抗由57.1 W增加至61.7 W。这表明通过优化过孔反焊盘尺寸,同样可以起到改善过孔阻抗的连续性的效果。

图4 反焊盘尺寸对过孔阻抗的影响

3.2 接地孔对过孔阻抗和损耗的影响

对于一个4层板,当信号由顶层传输线转至底层时,可能会出现两种情况(见图5)。图5(A)表示信号过孔旁没有地孔的情况,此时信号通过过孔时,返回路径通过两地层返回,未受控的返回电流产生了地弹效应,且信号通过过孔时产生的电磁波(EM)在两底层上传输,导致电压波动,引起信号完整性问题[9][10]。图5(B)为增加接地孔情况,此时接地孔为过孔信号提供了完整的返回路径,同时也为过孔信号提供了参考孔,从而提高了信号过孔的阻抗连续性,并减小信号损耗。这里主要研究了接地孔对过孔阻抗及损耗的影响。

图5 无地孔和有地孔时过孔信号返回路径

试验在单端信号过孔旁增加了1至4个接地孔参考孔,研究了接地孔数量对单端过孔阻抗的影响,结果见图6。由图看出,过孔阻抗随接地孔数量增加而降低。这是由于随接地孔数量增加,信号过孔与地孔间电容增加,即调整接地孔数量可有效控制过孔阻抗。

图6 接地孔数量对过孔阻抗的影响

图7显示了信号孔与接地孔距离对过孔阻抗的影响。由图看出,当信号孔与接地孔距离由0.40 mm增加至0.70 mm时,过孔阻抗呈不断增加趋势。与传输线以地层作为参考层类似,增加接地孔后,信号过孔以接地孔为参考孔。当信号孔与接地孔距离增加后,信号孔与接地孔间电容降低,过孔阻抗增加。由此可见,通过调整信号孔与接地孔之间的距离,可实现对过孔阻抗的控制。

图7 信号孔与接地孔距离对过孔阻抗的影响

通过以上试验可以发现,当有4个接地孔围绕在信号孔周围时(效果见图8),其结构类似同轴电缆。此时单端过孔阻抗可通过同轴电缆阻抗公式(公式1)进行近似计算[11]。

式中,D表示接地参考孔对角距离,d表示信号孔孔径,e为介质层介电常数。

图8 采用4个接地孔时的过孔结构[12]

通过公式(1)可以计算出不同设计参数时的过孔阻抗,结果见表1。由表看出,过孔阻抗理论计算值与测量结果基本一致。这表明该结构过孔的过孔阻抗可采用同轴电缆阻抗公式进行近似计算。

表1 过孔阻抗计算值与测量值对比

图9为过孔孔径为0.20 mm、过孔长度为1.0 mm时接地孔及数量对过孔损耗的影响。由图看出,增加接地孔后,过孔损耗明显降低,且接地孔数量越多,过孔损耗越小。这是由于接地参考孔为过孔信号提供了完整的返回路径,使过孔导致的阻抗不连续程度明显降低,阻抗不连续引起的信号反射减弱,因此过孔损耗减小。增加接地孔后,还可以减弱信号过孔间的串扰,提高过孔信号传输质量。同时,接地孔还可以避免辐射导致的EMC/EMI问题[4]。

图9 接地孔对过孔损耗的影响

3.3 多余短柱对过孔阻抗和损耗的影响

在高速多层PCB中,当信号从顶层传输到内部某层时,用通孔连接就会产生多余的导通孔短柱,短柱极大地影响着信号的传输质量。当信号在通过过孔传输到阻抗匹配的另一层线路时,会有一部分能量被传递到过孔的短柱上,而这一部分由于没有任何的阻抗终结,所以可以被看作是全开路状态,因此这个分支便会造成剩余能量的全反射,这大大地削弱了信号质量,损坏了原始信号的完整性[1]。采用盲孔和埋孔,可有效避免短柱对信号完整性的影响,但该技术工艺复杂且成本高。而采用背钻技术将信号孔中多余的短柱钻掉,可获得更好的过孔信号传输质量,所以,研究短柱对过孔信号完整性的影响有助于平衡成本与性能。

为研究短柱对过孔信号完整性的影响,试验通过采用背钻技术,控制背钻深度方法获得了不同短柱长度的单端过孔。图10为多余短柱长度对过孔阻抗的影响。由图看出,当多余短柱长度由0.20 mm增加至0.80 mm时,过孔阻抗呈不断下降趋势;多余短柱长度每增加0.10 mm,过孔阻抗约下降0.40 W ~0.90 W。

图10 多余短柱长度对过孔阻抗的影响

研究多余短柱对过孔损耗的影响,图11显示了过孔多余短柱长度由0.20 mm增加至0.80 mm时过孔损耗变化情况。随多余短柱长度的增加,过孔损耗呈现出明显增加趋势,且短柱越长谐振幅度越大;10 GHz频率下,多余短柱长度每增加0.10 mm,过孔损耗增加0.15 dB。试验还表明,信号过孔孔径越大,多余短柱对过孔阻抗、损耗的影响越大。

图11 多余短柱对过孔损耗的影响

多余短柱会导致过孔电容增加,且短柱长度越大,电容越高,而电容增加会导致谐振频率降低,从而使谐振点附近的损耗变大。谐振频率与电容、电感关系可用公式(2)进行描述。图12显示了不同短柱长度情况下的谐振情况。由图可以看出,多余短柱越长,谐振频率越低。当短柱长度分别为0.20 mm、0.45 mm和0.80 mm时,各过孔第二次谐振频率分别11.03 GHz、10.99 GHz、10.92 GHz,第三次谐振频率分别为12.66 GHz、12.52GHz和12.39 GHz。

图12 多余短柱对谐振频率的影响

4 结论

通过对过孔设计参数孔径、过孔长度、焊盘/反焊盘尺寸进行优化可有效提高过孔阻抗连续性。当过孔长度小于1.0 mm时,可通过对这4个设计参数进行优化,将过孔引起的阻抗变化控制在10%以内。为过孔信号提供返回路径,可实现对过孔阻抗的控制,并能降低过孔的信号损耗。采用4个接地参考孔时,过孔阻抗可通过同轴电缆阻抗公式近似计算。多余短柱会导致过孔阻抗降低,损耗增加。

[1]Richard W. Y. C., See K. Y., and Chua E K.,Comprehensive analysis of the impact of via design on high-speed signal integrity, 9th Electronics Packaging Technology Conference, Cambridge(USA), 2007: 262-266.

[2]Laermans E., Geest J. D., Zutter D. D., Olyslager F., Sercu S., and Morlion D., Modeling complex vìa hole structures, IEEE Transactions on Advanced Packaging, 2002, 25(2): 206-214.

[3]Kohlmeier D., Via modeling, Printed Circuit Design& Manufacture. 2005, 22(12): 26-28.

[4]Hsu H., and Richard W. Z., Via structure for improving signal integrity, United States Patent,2011, 12, No. US 8084695 B2.

[5]Pak J. S., Aoyagi M., Kikuchi K., and Kim J., Bandstop filter effect of power/ground plane on throughhole signal via in multilayer PCB, IEICE Transactions on Electronics, 2006, E89-C(4): 551-559.

[6]Cai X. W., Tian Y., and Tong L., Electromagnetic characterization analysis of the connecting structure of the via in multilayered microwave circuit, Global Symposium Millimeter Waves, Nanjing (China),April 2008: 21-24.

[7]Kim Y. W., Kim J. H., Yang H. W., Kwon O. K., Rvu C., and Min B. Y., A new via hole structure of MLB(multi-layered printed circuit board) for RF and high speed systems, 55th Electronic Components &Technology Conference, Lake Buena Vista (USA),2005, vol.2:1378-1382.

[8]Wang C., Fan J., Knighten J. L., Smith N. W.,Alexander R., and Drewniak J. L., The effects of via transition on differential signals, IEEE Electrical Performance of Electronic Packaging, Singapore,2001:39-42.

[9]赵莲清, 刘二利. PCB中过孔对高速信号传输的影响[J]. 印制电路信息2009, (9): 46-49.

[10]魏丽丽,刘浩. 高速PCB设计中的过孔研究[J]. 印制电路信息, 2007, (9):31-34.

[11]Dong X. W., Lu M., and Chen X. Q., Analysis and calculation of the characteristic impedance of eccentric coaxial cables, Electric Wire & Cable,2007, No.6:16-20.

[12]Thomas H., Design of impedance controlled through via-holes, Technical Feature, 2004, 2:84-88.