基于0.18 μm 工艺SOI 技术60 V LDMOS 的设计与分析*

2013-12-22檀柏梅

戚 帆,檀柏梅* ,翁 坤,宋 雯

(1.河北工业大学微电子技术与材料研究所,天津300130;2.福州大学福建省微电子集成电路重点研究室,福州350002)

随着电子科学技术的迅猛发展,纳米级(100 nm以下)加工的CMOS 电路已逐渐成为研究工作的重心以及产业生产主流[1]。SOI(Silicon-On-Insulator)技术是在顶层硅和背衬底之间引入了一层埋氧化层,在它上面的Si 薄层内制作MOS 器件[2]。与体硅MOS器件相比,SOI 绝缘无需复杂的阱结构,闩锁现象也不复存在,源极与漏极区的寄生电容也因绝缘衬底而大幅的降低,此外,SOI 可有效的改善体硅MOS 在辐射损伤方面的容忍度,SOI 技术易形成浅结和全介质隔离,功耗小、工作速度快。SOI 技术的发展提高了MOS IC 的集成度、功能和可靠性,将成为深亚微米及纳米级集成电路的主流技术之一[2-3]。

阈值电压的控制是一个很关键的问题,同时源漏击穿电压、饱和电流也是器件正常工作的一个重要指标[4-6],本文研究分析了基于SOI 技术的60 V LDMOS(Lateral Double-Diffused Metal-Oxide Semiconductor,横向扩散金属氧化物半导体),并对这些参数进行了onwafer 特性表征。

1 器件结构及分析

1.1 基础理论

漂移区加入STI(Shallow Trench Isolation)浅沟槽隔离,并没有使用传统的LOCOS(Local Oxidation of Silicon)局部场氧化工艺。这种结构在保证器件在不改变其他工艺参数的同时,漂移区更易达到完全耗尽,缩小器件尺寸[4],承受高击穿电压。STI 结构在此设计中相当于一种槽氧层,能够减弱场板边缘下面硅层中的电场强度,使器件不易在此处提前击穿,从而提高器件整体的击穿电压[5-6]。,并且消除了LOCOS 带来的鸟嘴现象。同时还在器件的最外层加入了Trench Isolation 槽型隔离(图中TR 部分),这是SOI 器件实现全介质隔离的一个优势所在,能有效地防止高电压产生的寄生效应及器件被击穿后对周围元器件产生影响,增加了元器件的隔离效果和集成度[8-9]。

1.2 器件结构

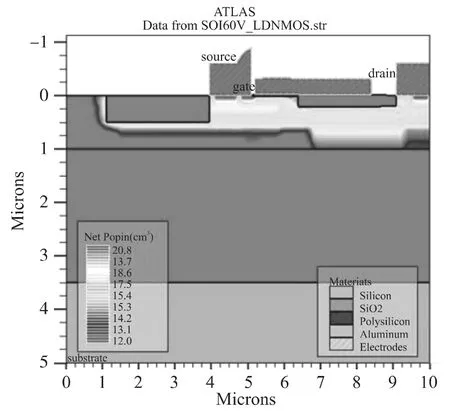

本文所使用的工艺为0.18 μm 60 V SOI 工艺,集成1.5 V/5 V LDNMOS、HPVMOS,BJT VNPN/LPNP,Zener Diode,Schottky Diode 等器件。本文中涉及的LDNMOS,在器件与衬底之间加入了一层绝缘埋层SiO2隔离,并且绝缘埋层与横向的器件隔离相连,即Trench Isolation,从而很好地实现了全介质隔离。图1为SOI 60 V LDNMOS 的结构示意图,上侧为器件俯视图,下侧为器件纵向中心位置剖面图。

图1 SOI 60 V LDNMOS 的结构示意图

如图1 中,BOX,Deep NM(N-shift),STI 分别表示埋氧层、横向漂移区和浅沟槽隔离。LDNMOS 是非对称结构,并且栅极、有源区成六边形的环状结构,这种结构可增大饱和电流,降低导通电阻、寄生电容,并且无寄生的Kink 效应,在沟道与漏端之间是横向掺杂漂移区,使高电压集中在这一区域,在漂移区通过阶梯掺杂技术[7]引入,能够使器件更易耗尽从而提高整个器件的耐压。

器件组成结构:P 型衬底→BOX 埋氧层→顶层硅→Trench Isolation 隔离→深P 阱→N 型补偿区→P 型掺杂阱区→N 型漂移区→STI 浅沟槽隔离→注入N+形成源漏区。

表1 SOI 600 V LDNMOS 的结构图层含义

其中,关键尺寸有沟道长度为1.2 μm,沟道宽度为3 μm(10 μm、20 μm、50 μm、80 μm),STI 结构的厚度和长度直接影响BV(击穿电压)和器件尺寸的大小,STI 长度为3 μm,厚度为0.25 μm,此结构的设计,很好的调整了漂移区浓度和长度,达到了减小器件尺寸的目的。漂移区为长度3.4 μm,栅长为3.2 μm。

STI 技术工艺步骤:首先,类似LOCOS,依次生长SiO2淀积Si3N4涂敷光刻胶,光刻去掉场区的SiO2和Si3N4;其次,利用离子刻蚀在场区形成浅的沟槽;然后,进行场区注入,再用CVD 淀积SiO2填充沟槽;最后,用化学机械抛光技术去掉表面的氧化层,使硅片表面平整化形成沟槽隔离区和有源区。

Trench 隔离首先进行光刻,在圆片的基础上刻蚀至BOX 埋氧层,刻蚀出沟槽后,去掉氮化物,生成5 000 Å 热氧化层,Trench 内填充多晶硅,然后刻蚀掉表面的多晶硅和氧化物。

2 仿真与分析

2.1 工艺仿真

图2 SOI 60 V LDNMOS 工艺仿真结构图

利用SILVACO 公司的Athena 工具,对器件工艺步骤和结构进行仿真,初步确定出器件的关键尺寸,并验证foundry 提供工艺参数。图2 为SOI 60 V LDNMOS 仿真结构图。实验只对器件进行了二维仿真,衬底浓度2×1015cm-2,漂移区浓度1.2×1013cm-3。沟道长度1.2 μm,横向宽度设为3 μm。STI长度为3 μm,STI 厚度为0.25 μm,漂移区为长度3.4 μm,栅长为3.2 μm。在经过前端工艺的多次牺牲氧化,1.5 μm 的顶层硅大约还剩下1.3 μm,再次通过做隔离的氧化减薄后,规模控制在1 μm 左右,且顶层硅厚有较好的均匀一致性。因为器件为环形,所以仿真的结构为器件的一半,能够正确地反映出器件的电学特性。

2.2 器件特性仿真

利用SILVACO 公司的Atlas 工具对器件结构进行电学特性模拟。使用工艺仿真的器件结构,加载器件模型,调整参数,利用TCAD 软件仿真得到LDNMOS 主要直流特性参数:开启电压Vth为1.05 V(如图3 所示IdVg),饱和电流Idsat为300 μA(如图4所示IdVd),击穿电压BV 为76 V(如图5 所示BV)。模拟仿真的结果与设计所预计达到的结果非常吻合,说明各掺杂区的杂质掺杂浓度、温度、时间等条件得到了很好的优化,对Foundry 的工艺参数进行了很好的验证。

图3 LDNMOS 器件仿真转移特性曲线图

图4 LDNMOS 器件仿真输出特性曲线图

图5 LDNMOS 器件仿真击穿电压曲线图

3 流片结果分析

本次流片采用0.18 μm 60 V SOI 标准工艺,选定新傲公司3 μm 埋氧层和1.5 μm 顶层硅的SinBond SOI 材料,通过对模拟仿真结果分析,确定器件测试结构,进行On-wafer 测试,测试曲线如图6 ~图8 所示。图6 中,以3 μm/1.2 μm 管子为例,栅极加载扫描电压0 ~5 V,漏端加载30 V 工作电压,扫描漏端电流,得到在Vth=1.1 V 时,电流开始增大,当VG=5 V时,ID 达到2.3 mA。表明管子在正常阈值电压范围内开启,性能良好。

图6 流片测试开启电压曲线

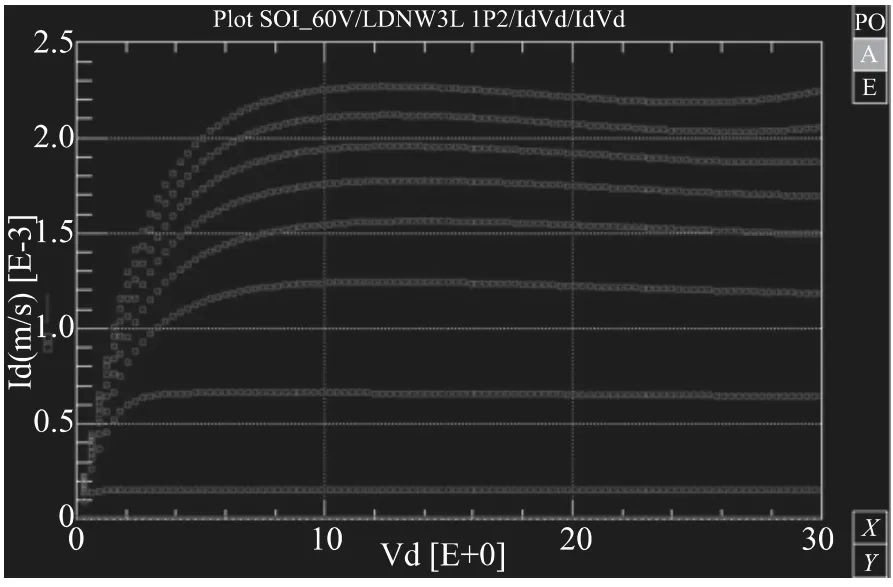

图7 流片测试输出特性曲线

图8 流片测试击穿特性曲线

图7中,同样以3 μm/1.2 μm 管子为例,栅极电压分别为0 ~5 V,漏端电压加载0 ~30 V,扫描漏端电流。当VG=10 V 时,漏端饱和电流Idsat基本稳定在2.5 mA。从曲线图中我们看出,测试管在6 V 左右进入饱和区,Idsat一直比较稳定,无明显的kink 效应。

图8 中,加载漏端电压0 ~80 V,并且将漏端电流限制在1 μA,以防止漏端电压过高,器件被击穿烧毁。发现当Vds=66.4 V 时,漏端电流急剧增大,这时LDNMOS 管被击穿。同时发现沟道宽度器件的击穿电压BV 都稳定集中在65.6 V ~66.4 V 之间,能够在高压条件下正常工作,说明器件获得良好的击穿特性。

经过数据处理分析之后,得到了LDNMOS 器件的主要性能参数:Vth=1. 1V,Idsat=2. 3 mA,BV=66.4 V,直流特性参数表现良好,与传统的采用LOCOS 隔离的SOI 器件相比,器件尺寸得到了缩小,驱动能力更强。

表2 流片测试采用STI 结构与传统LOCOS 结构对比结果

4 结论

本文采用标准0.18 μm SOI 工艺技术对其中的高压60 V LDMOS 进行了研究与分析。采用SILVACO 软件对器件进行了模拟仿真,确定器件的设计规则和关键尺寸,再进行流片测试对所设计的器件进行了验证。实验结果表明该SOI 60 V LDMOS 器件结构无明显kink 效应,器件的阈值电压、击穿电压以及饱和电流等直流特性都获得良好的表征参数,并有进一步提升的空间,为今后高压器件建模、设计和流片提供了很好的基础。对0. 18 μm SOI DMOS 设计、发展、利用以及高压功率器件领域实际应用中具有十分重要的意义。

[1] 黄如,张国艳,李映雪,等. SOI CMOS 技术及其应用[M]. 北京:科学出版社,2005.

[2] 施敏.半导体器件物理与工艺[M]. 苏州:苏州大学出版社,2004,1652213.

[3] 林成鲁,张正选,刘卫丽. SOI 材料和器件及其应用的新进展[J].核技术,2003,26(9):658-663.

[4] Costa J,Carroll M,Jorgenson J.A Silicon RFCMOS SOI Technology for Integrated Cellular/WLAN RF TX Modules[C]//2007 IEEE Microwave Symposium,2007(3-8):445-448.

[5] Chamdhry A,Kmmar M J. Controlling Short-Channel Effects in Deep-Submicron SOI MOSFETS for Improved Reliability:A Review[J].IEEE Transactions on Device and Materials Reliability,2004,4(1):99-109.

[6] Pornpromlikit S,Jeong Jinho,Presti Calogero D. A 25 dBm High-Efficiency Digitally-Modulated SOI CMOS Power Amplifier for Multi-Standard RF Polar Transmitters[C]//IEEE RFIC 2009,Boston.157-160.

[7] 张盛东,韩汝琦,Tommy Lai,等. 漂移区为线性掺杂的高压薄膜SOI 器件的研制[J].电子学报,2001,29(2).

[8] Bonetal O. High Voltage Devices Added to a 0. 13 μm High(Symbols)Resistivity Thin SOI CMOS Process for Mixed Analog-RF Circuits[J].IEEE International SOI Conference,Hawaï,171-173.

[9] Langdo T A,Cmrriemt,Cheng Z Y,et al. Strained Scilion-on-Insulator Technology:from Materials to Devices[J]. Sol Sta Elec,2004,48(8):1357-1367.

[10] Bon O,Gonnard O,Gianesello F. First 15 V Complementary LDMOS Transistors in Thin SOI 65 nm Low Power Technology[J].IEEE Power Semiconductor Devices and IC’s,2007:209-212.