基于Petri Nets的ASIP流水线研究

2013-10-25赵谦,朱勇

赵 谦,朱 勇

基于Petri Nets的ASIP流水线研究

赵 谦,朱 勇*

(武汉纺织大学 数学与计算机学院,湖北 武汉 430073)

探讨了将CPU中流水线用PetriNets模型进行描述设计的一种方法,为了分析验证PetriNets流水线模型描述的正确与否,搭建了一个用verilog语言实现的模型CPU运行环境,该CPU的CU单元用PetriNets描述,对其做了仿真验证,对这项研究的可行性进行了验证,为以后进一步研究提出了一个可行的指导思想。

Petri网;专用指令集处理器;Verilog硬件描述语言;可编程门阵列

1 引言

目前,随着超大规模集成电路FPGA和CPLD的发展[1],国外集成电路设计也越来越强调设计的可重用性和短周期性[2],IP(Intellectual Property)复用概念应运而生,并且已成为集成电路发展的趋势[3],中国科技大学李曦等提出了“描述-搜索-细化”的ASIP设计方法学,并设计了相应的描述语言与设计环境。山东科技大学信息学院陈新华、张德学承担的青岛市科技局基于OR1200嵌入式SoC网关集成电路的设计。Petri网理论现在已经十分的成熟,国内外有多所大学在对Petri网的应用进行研究,中科大的朱赟等人[4],利用Petri网对ASIP进行了初步的建模。

Petri Net模型在并发性和延时性上要优于moore和mealy型状态机,基于CPU中的并行和跳转运行机制,设计者可以采用Petri Nets模型描述MIPS CPU的状态机。在本文中,作者用Petri Nets建模方法实现了一个多周期的简单32位MPIS架构模型CPU,在FPGA开发板上进行了逻辑验证,该CPU可以实现基本的MIPS指令集。

2 Petri Net定义

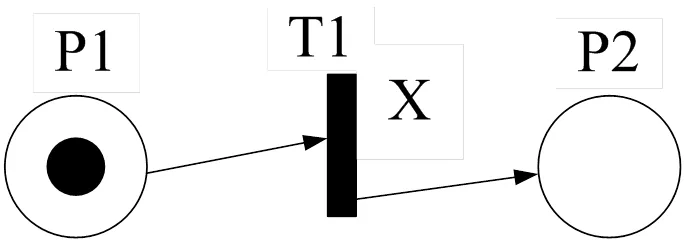

1962年,C.A.Petri(Carl Adan1 Petri)博士提出了Petri Nets模型(见图1),2007年,中国科技大学提出了基于PN的ASIP体系结构建模的PNP模型,对于这方面的研究作出了很大的贡献。当今Petri Nets是一种系统的、数学的和图形的描述和分析工具。

Petri Nets由同一个arc连接的两个placeholder,P1、P2,placeholder不能同时带有token值,P1带有token值,此时P1处于激活状态,而P2中没有token值,说明P2此时处于非激活状态。

图1 Petri Nets模型

3 基于PetriNets的流水线建模

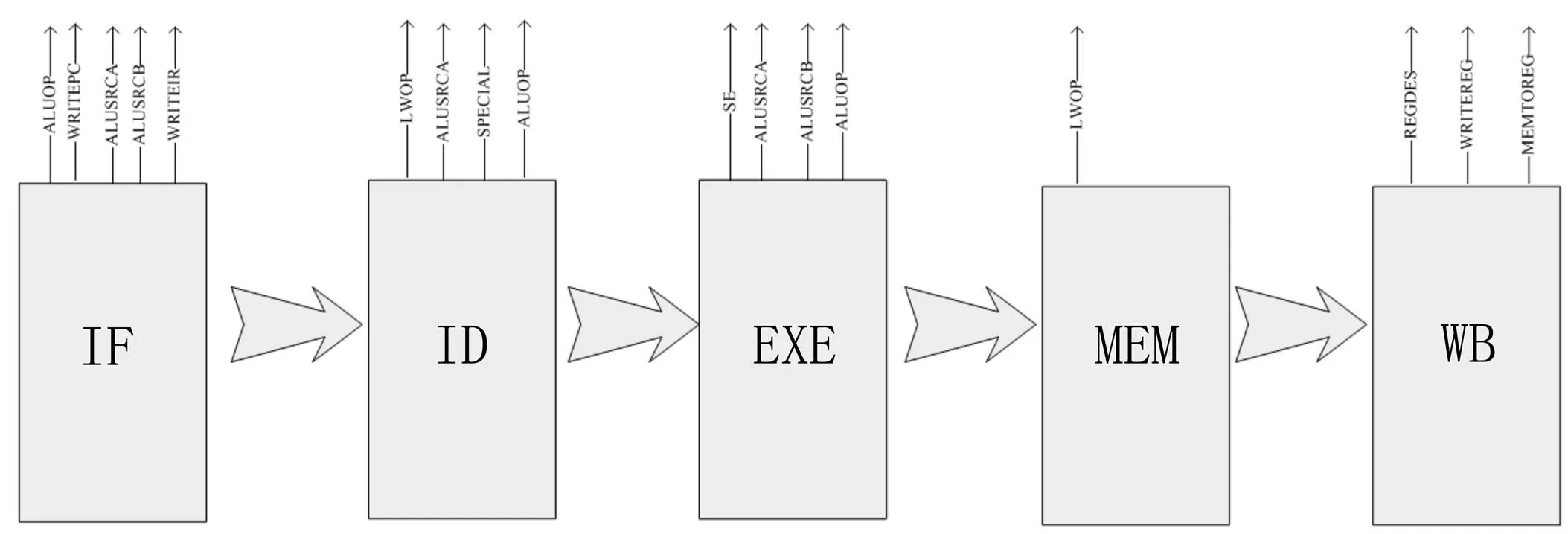

对于PetriNets描述的状态机模型进行了初步的研究,在此探讨了I类指令中LW指令的5个运行周期在PetriNets模型中的转换与变迁[5-7],给出了ASIP流水线在执行LW指令时从取指令状态变迁到指令译码状态时,Petrinets流水线描述见图2。

图2描述的是模型CPU中CU模块中的状态机,图中表示的含义是,在IF状态,库所会输出ALUOP,WRITEPC,ALUSRCA,ALUSRCB,WRITEIR五个控制信号,箭头代表是每个变迁T,同理ID,EXE,MEM,WB4个库所也在相应的变迁时输出对应的信号,设计者可以根据这个PetriNets模型变迁图,重新的设计模型CPU中CU单元控制信号的状态机模型,不采用传统的mealy型状态机的设计方式。

图2 CU单元PetriNets流水线描述

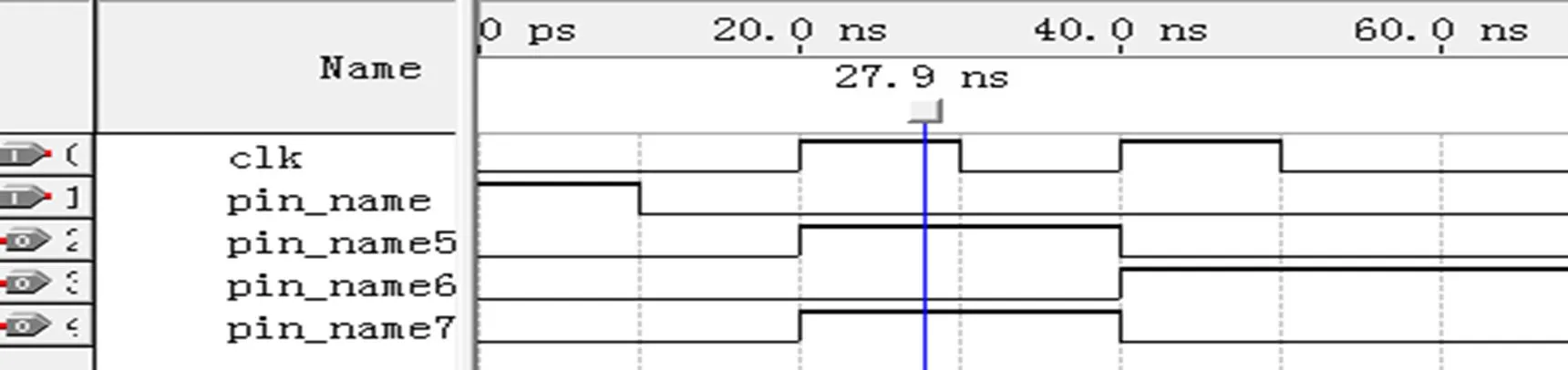

在Quartus9.0中针对IF到ID的变迁进行了系统建模实现,采用quartus9.0自带的功能仿真,将IF和ID库所初始化,IF库所被激活,然后发出ALUOP的控制信号,当ID被激活后,ALUOP拉低,LWOP处于高电平。图3是库所变迁的功能仿真图。

图3 库所变迁仿真图

4 基于PetriNets描述的流水线研究分析

4.1 硬件实验环境搭建与仿真

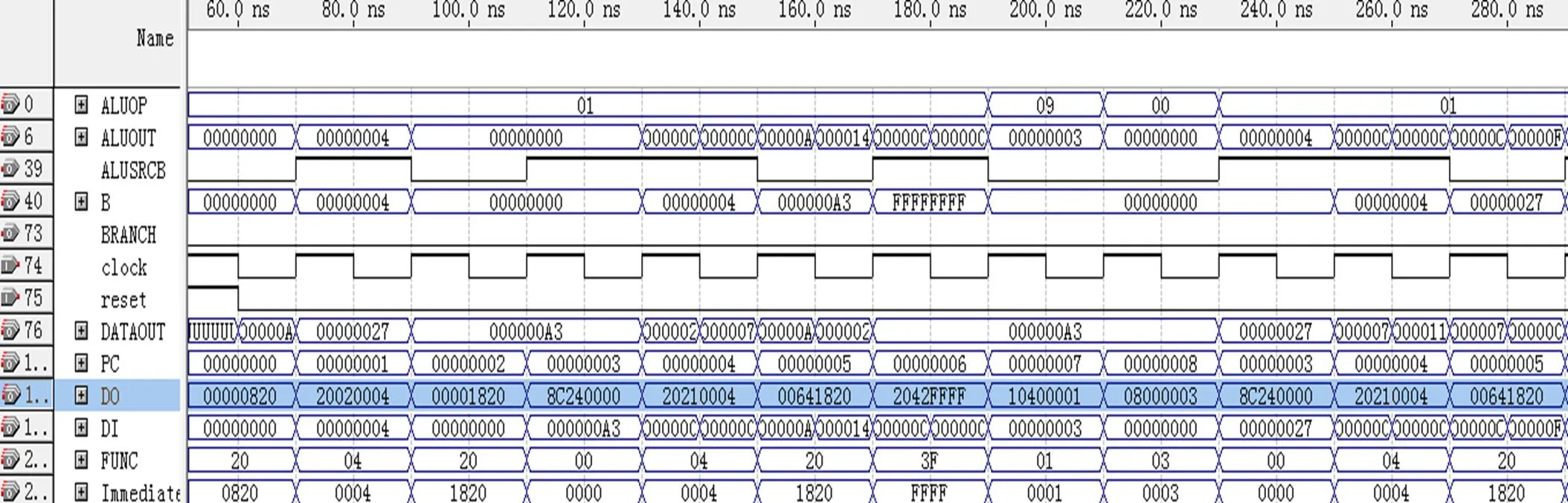

用PetriNets模型来对MIPS架构的模型CPU的CU单元进行状态机的高级描述首先要保证模型CPU的硬件环境搭建成功,为此,设计者通过Quartus软件,用Verilog硬件描述语言完成了一个多周期的模型CPU,并且用测试程序对模型CPU进行了功能仿真与验证,测试仿真图如图4,每次循环在8C240000指令时,memory成功的取出对应地址的值,第一次取A3,第二次是27,接着取出79和115,结果和预期一致,仿真完将工程下载到FPGA开发板上正常运行,证明模型CPU的逻辑设计是正确的,实验的硬件环境搭建成功。

图4 模型CPU测试仿真图

4.2 硬件逻辑实现

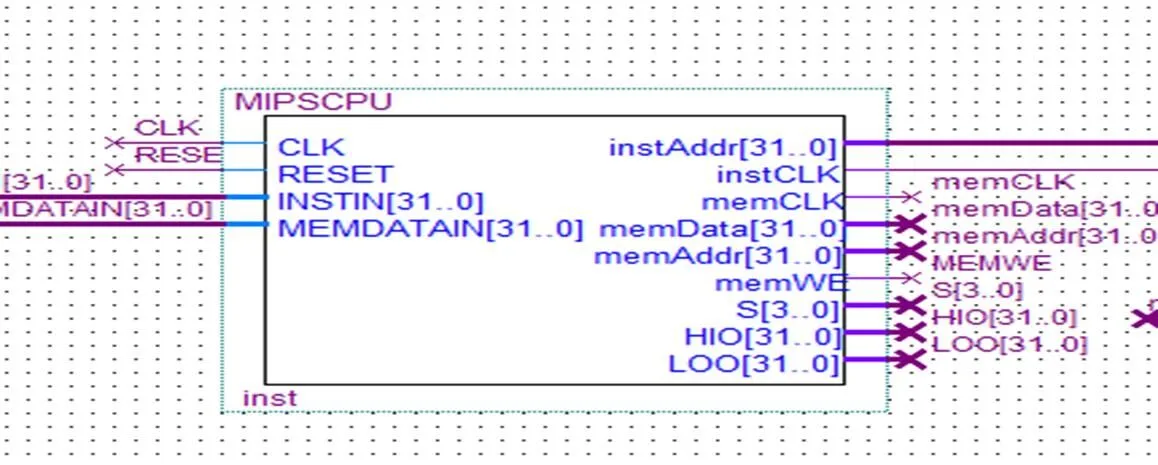

图5是模型CPU模块的截图,CLK是时钟信号,memwe是memory写信号,instaddr是PC值,instin是指令信号,来源于指令存储器,MEMDATAIN是从memory中读取的数据,其它的信号是设计者做仿真引出来的内部信号。

图5 模型机的硬件逻辑实现模块

5 总结

设计者给出了多周期ASIP的硬件环境搭建,对于CU单元中基于PetriNets模型的状态机的描述给出了抽象的描述图,设计者实现了CPU中CU单元流水线PetriNets描述验证,完成了CU单元硬件描述与逻辑综合。给出流水线模型CPU的硬件环境搭建,然后给出流水线PetriNets状态机变迁描述图,最后根据设计的状态变迁图转换成对应的verilog硬件描述代码,仿真成功后下载到FPGA开发板上运行。在以后的研究进行中,最终实现对基于MIPS架构的模型CPU的流水线状态机进行完整的设计实现。

[1] 张彦铎,陈驰,于宝成,等. 高速图像采信系统的研制[J]. 武汉工程大学学报,2013, (5).

[2] 吴琼飞.基于ADL的ASIP系统级综合方法研究[D]. 武汉:武汉纺织大学,2011.

[3] 徐智辉,李卫中,肖永军. 自由摆上目标动态平衡控制系统的设计[J]. 武汉工程大学学报,2013,(1).

[4] 朱赟,李曦,龚育昌,等.基于Petri网的ASIP体系结构形式化建模方法研究 [J].MINI-MICRO SYSTEMS,2006.

[5] 朱勇.TTA流水线Petri网模型[J].微电子学与计算机,2013,(2).

[6] 陈文.基于Petri网的ASIP体系结构研究 [D].武汉:武汉纺织大学,2012.

[7] 朱子玉, 李亚民. CPU芯片逻辑设计技术 [M].北京:清华大学出版社, 2005.

Pipeline of ASIP Design Method Based on Petri Nets

ZHAO Qian, ZHU Yong

(College of Mathematic and Computer Science, Wuhan Textile University, Wuhan Hubei 430073, China)

A method of using PetriNets model design the pipeline of the traditional CPU, to verify this method is correct, set up a model CPU environment which is designed by verilog language, the CU of this CPU is designed by PetriNets, which has simulated this model, at the same time, author comes up with acorrect theory.

PetriNets; ASIP; VerilogHDL; FPGA

TP368.1

A

2095-414X(2013)03-0061-03

武汉纺织大学研究生创新基金(2012).

朱勇(1964-),男,教授,博士,研究方向:嵌入式SOC,ASIP.