多通道高速ADC电路PCB设计技术浅谈

2013-09-30李军辉简育华袁子乔

李军辉 简育华 袁子乔

(西安电子工程研究所 西安 710100)

0 引言

随着芯片技术的不断发展,ADC的采样频率已经从以前的MHz发展到当前的GHz。伴随着ADC采样频率的不断提高,ADC的模拟输入信号频率和带宽也在不断提高,从视频信号到现在的中频甚至射频信号。因此,用于低速ADC采样电路的一些设计方法已经不适用于高速ADC的采样电路[3]。如何在高速ADC采样电路设计中提高ADC模拟输入信号各通道之间的隔离度变得尤为关键,对于数字地平面和模拟地平面的处理方式也非常关键。

对于高速ADC而言,模拟通道PCB上的每个过孔和走线都通过空间、电源平面和地平面对外进行电磁波的辐射;另一方面,由于高速ADC芯片的带宽都在GHz,它不仅容易受到其它通道模拟信号的干扰,也容易受到系统内或外界高速数字信号的电磁干扰。所以,在多通道高速ADC电路的设计中,首要的问题就是解决多通道之间的互耦问题,这其中就主要是解决模拟部分地平面的传导耦合以及各通道之间的辐射干扰问题。其次,还得解决外界和系统内数字部分对模拟输入信号的辐射干扰。

下面就以E2V公司的EV10AQ190这款芯片为例,先介绍一下此款芯片的主要特点,然后分别从模拟输入信号的处理,模拟电源、数字电源、数字和模拟地平面的隔离,数字输出信号的处理以及采样时钟的处理四个方面进行讨论[1],最后给出一个应用的实例。

1 EV10AQ190介绍

EV10AQ190是英国E2V公司的一款低功耗的高速ADC,其主要特点如下:

·四通道、10位分辨率的ADC,使用了e2v单

核技术;

四通道、1.25GHz的采样率;

两通道、2.5GHz的采样率;

单通道、5GHz采样率;

内置四通道高速交错采样电路;

·单个2.5GHz差分输入采样时钟;

·500mVpp的模拟输入信号(交流或直流耦合方式);

·高达3.2GHz的输入信号带宽;

·通道间的隔离度大于60dB;

·DDR-LVDS数据输出方式;

·SPI配置接口;

·3.3V模拟电源和1.8V的数字电源;

·每通道1.4W功耗。

其内部结构如图1所示。

图1 EV10AQ190内部结构图

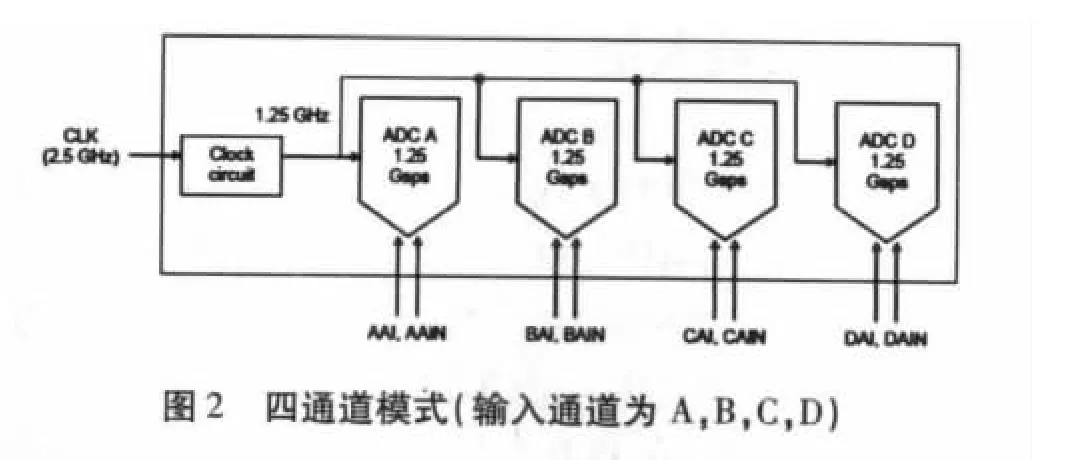

通过SPI口,它可以灵活的配置为四通道1.25GHz采样率,或者两通道2.5GHz采样率,或者单通道5GHz采样率的ADC,不同的配置模式见图2~7。

2 模拟输入信号的处理

前端接收机对天线接收到的微弱信号进行多级放大后输出到ADC,ADC前端采用与ADC相匹配带宽的射频变压器将单端模拟信号转换为差分信号后直接输入到ADC。为了保证多路模拟输入信号之间的隔离度,在PCB布局时就要对模拟信号的走线方式和布局等方面进行多重考虑:

a.在允许的布局空间内尽可能扩大各模拟通道之间的距离;

b.尽可能的保证各通道模拟信号走线的等长;

c.电源尽量远离模拟信号的走线;

d.对整个模拟信号所在区域以及各模拟信号之间加以屏蔽处理;

e.模拟信号尽量在TOP层走线,以减少模拟信号线的过孔数量;

为了尽量降低模拟信号的空间辐射,提高通道间的隔离度,需要在模拟信号走线周围铺设地平面。

EV10AQ190的输入信号带宽达到了3.2GHz,因此在ADC输入的前端选择变压器的带宽范围为4.5MHz~3GHz。通过变压器将单端模拟输入信号转换为差分信号后送给ADC的输入端,原理图设计和PCB的布局见图8和图9。

图9 模拟输入信号布局

3 模拟电源、地和数字电源、地的处理

模拟电源、地和数字电源、地的处理在高速ADC的PCB设计中至关重要[1]。在高速混合信号处理的电路设计中,必然存在模拟电源和数字电源。但随着高密度、高复杂系统需求的不断发展,PCB板的供电方式已经由模拟和数字电源分别供电的方式转变为单独的数字供电方式[4]。

EV10AQ190的电源有两种:模拟电源3.3V和数字电源1.8V。模拟电源3.3V采用了线性电源芯片(LDO)从数字电源取电,再经过电容滤波和磁珠的隔离后给ADC的模拟电源供电。同时为了提高ADC芯片的性能,ADC的数字电源1.8V也采用了线性电源供电的方式,从系统的数字电源取电后直接供电,如图10所示。此外,还需对模拟电源和数字电源进行良好的去耦处理,靠近模拟电源和数字电源的管脚附近都需要放置适量的去耦电容。

图10 电源供电方式

随着芯片技术的不断发展,在高速ADC芯片中,已经没有模拟地与数字地管脚的区分。因此在高速ADC的采样电路中,不再像以前那样进行模拟地和数字地的分割,一般采用统一的地平面,这样可以较好的保证信号阻抗的连续性和信号回流路径的完整性。为了保证ADC输入模拟信号通道之间的隔离度,防止模拟信号经过地平面进行传导干扰,对模拟输入部分的地平面进行了强行分割处理,使得每个模拟通道的参考地平面在模拟走线下方分开,最后在ADC芯片下方与系统的地平面连接。经过测试,这种分割方法能够有效降低模拟信号之间通过地平面的传导干扰。同时将模拟走线层上的铺地区域通过过孔与下面的地平面连接,吸收模拟信号的空间辐射。EV10AQ190前端模拟部分地平面的分割见图11。

图11 模拟部分地平面分割示意图

4 对ADC输出信号的处理

对于高速ADC而言,输出信号的速率一般都达到了Gbps。为了能够将数字信号稳定可靠地传输到后端处理芯片,保证输出信号阻抗的完整性至关重要[5]。此时,PCB的叠层一般选择“电源层-信号层-地层”的顺序,这样对于复杂的PCB板,至少可以保证信号有一个完整的地平面作为参考平面,从而保证信号线阻抗的完整性。在四通道1.25GHz采样率下,EV10AQ190每个通道输出信号的速率为1.25Gbps,输出信号的时钟为625MHz。即使电源平面因为模拟电源和数字电源而进行分割,但因为地平面为一个完整的平面,因此输出信号阻抗的完整也是有保证的。

5 采样时钟的处理

采样时钟的相位噪声会引起系统信噪比的降低。它的抖动将对输入信号进行调制并抬高噪声和失真电平,所以必须采用低相位噪声和抖动的时钟芯片作为ADC的时钟源。在采样系统中采样时钟既与模拟信号一样易于被噪声感染,也与数字信号一样易引起噪声,因此必须同时把它与模拟和数字系统相隔离。然而,受系统所限这通常不容易实现[1]。

在许多情况下,高速ADC的采样时钟都由系统的频综模块产生后直接送出,经过变压器隔离后转换成差分信号输入给ADC。由于频综产生的是模拟正弦时钟,极易受到干扰,因此在变压器前端的单端时钟PCB走线要尽可能短,而经过变压器后的差分时钟信号线的抗干扰能力较强,所以变压器一般选择尽量靠近时钟的输入端放置。同时为了减少时钟信号线与模拟信号线之间的干扰,将它们之间的地平面进行分割以及在它们的走线层上铺设地平面是很有必要的,见图12所示。

图12 时钟走线与模拟走线的处理图

6 设计实例

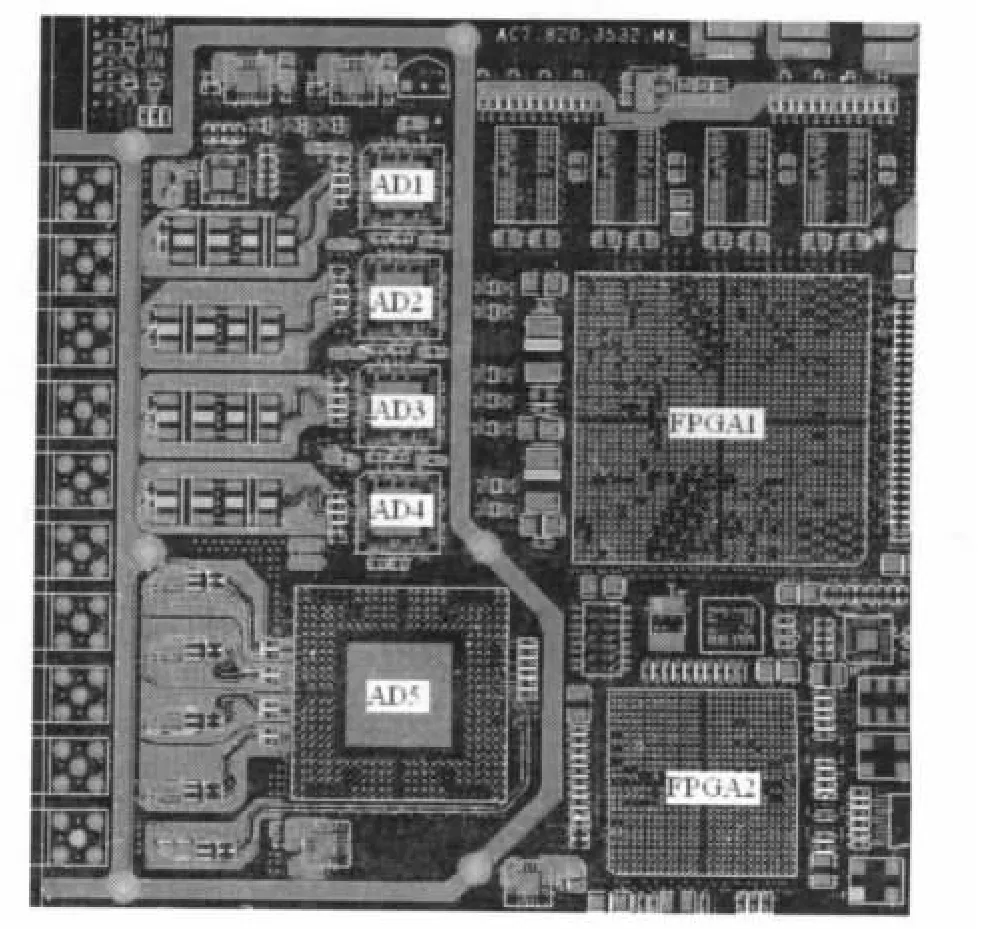

如图13所示,是一个包含5个高速采样ADC的高速数模混合处理板的PCB部分截图。

图13 设计实例

AD1-AD4是四通道独立采样的高速ADC;AD5为高速ADC(EV10AQ190);FPGA1用来接收AD1-AD5的数据并进行处理,FPGA2完成对AD1-AD5的SPI配置。从图中可以看出,ADC前端都采用了变压器方式将输入的单端模拟信号转变为差分信号后送给ADC。AD1-AD4的时钟由外部提供,经过一个时钟缓冲器后分别给它们提供时钟,AD5的时钟也由外部提供,经过变压器后直接送给了AD5。

在图中可以看出,5路ADC的电源都由线性电源分别进行供电,并在它们之间用磁珠进行了隔离处理;模拟输入部分和时钟在其布线层都铺设了隔离的地平面,并对它们之间的地平面进行了分割,这样尽可能地提高了ADC各路之间的隔离度。在整个ADC所在的区域周围铺设了屏蔽罩,降低了ADC受到附近高速数字信号的干扰。

7 结论

在多通道高速ADC采样的数模混合PCB电路设计中,通过对模拟电路与数字电路进行合理的布局,减少数字电路对模拟电路的干扰;同时对模拟部分的电路进行合理的分割设计,降低模拟信号通道之间的互耦干扰,一定能够设计出满足指标要求的电路系统。

[1]陈慧青,江桦等.高速ADC电路的电磁兼容设计[C].第十六届电工理论学术年会论文集,22004,(7):93-96.

[2]吕文红,郭银景,唐富华等.电磁兼容原理及应用教程[M].北京:清华大学出版社,2009-08.

[3]Howard Johnson,Martin Graham.High-Speed Digital Design[M].北京:北京工业出版社,2012.

[4]钱振宇,史建华等.开关电源的电磁兼容性设计,测试和典型案例[M].北京:电子工业出版社,2011-07.

[5]Howard Johnson,Martin Graham.High-Speed Signal Propagation[M].北京:北京工业出版社,2012.