一种基于DSP的电能质量分析平台的研究与设计

2013-05-17曹爱飞

曹爱飞

(宿州职业技术学院机电工程系 安徽·宿州 234101)

一、引言

电力系统存在着大量非线性、冲击性和波动性负荷(比如大功率的变频设备),这些负荷造成电网可能发生波形畸变、电压波动、三相不平衡等,使得电网电能质量的严重降低。同时,随着科学技术和国民经济的发展,基于计算机、微处理器控制的精密电子仪器对供电质量的敏感程度较高的设备在企业中大量使用,由此对电能质量提出了更高的要求,从而使电能质量问题越来越受到人们的关注。而要对电网的电能质量进行改善,首先要对电能质量做出精确的检测和分析,基于单片机的电能质量分析系统由于运算速度慢,精度低,存储空间小,运算能力低等缺点,使其应用范围受到了很大的限制,往往不能满足系统的要求。本文提出的基于TMS320LF2407 DSP的系统,达到了实时数据采集和实时监测的功能,以及一些复杂的运算功能。同时还可充分利用该处理器的外设附加一些控制功能[1],为进行进一步的电能质量分析以及系统功能的扩展提供了良好的平台和基础。

二、系统的主要功能

根据电能质量分析平台的要求,系统的主要功能包括:

(一)采集电压互感器输出的电力系统中三相电压、三相电流的值,并计算基波的有效值。测量精度应不低于±0.1%。

(二)采集基波频率。测量精度应不低于±0.01Hz。

(三)通过基于RS-232标准串行口和上位机通信,数据格式和功能的定义符合电力系统中的101规约[2]。

(四)实时监测电能质量中的电压偏差和频率偏差的范围。当电压的偏差大于额定值的107%或小于额定值的90%时[2],向上位机报警电压越限;当频率值大于 50.2Hz 或小于 49.8Hz 时[3],向上位机报警频率越限。

(五)具有开关量输入输出能力,可以实现各种开关控制功能。

三、系统的硬件实现方案

(一)系统的整体结构

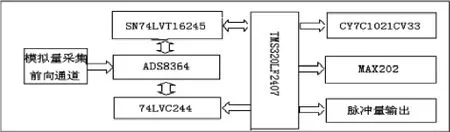

基于以上功能的要求,系统的整体结构如图1所示。

图1 整体结构框图

TMS320LF2407作为系统的核心,它内部有16K*16 位的 FLASH EEPROM,1.5K 字的数据/程序RAM,544字的双口RAM(DARAM)和2K字的单口RAM(SARAM)。所以本系统没有外接程序存储器,但数据空间是不够的,因为系统运行中需存储大量的中间变量,并且程序中有比较多的‘double’变量,一个‘double’变量需占用四个字节的空间。另外,在系统仿真时,仿真器要把程序下载到RAM区运行,所以本系统必须外扩数据存储器。CY7C1021V33-12是CMOS型的异步静态RAM,容量为64K字,存取速度为12ns,最大峰值功耗为576,满足系统使用要求,因此本设计选择CY7C1021V33-12作为扩展数据区。

LF2407是16位总线,为了提高ADS8364工作的稳定性,通过SN74LVT16245将DSP的数据总线同ADS8364的数据总线隔离。而为了增加一些关键控制信号(如启动ADS8364转换的信号)的稳定性,将它们首先通过74LVC244,再连接到各芯片的控制端。

本系统预留了脉冲量的输出通道,所以,当系统需要脉冲量输出时,就不必修改硬件,只需增加软件的控制就可以了。

(二)主要功能模块的硬件设计

1、数据采集模块的设计

数据采集功能主要是由ADS8364完成的。ADS8364是高速、低功耗、六通道同步采样的16位模数转换器。它的六个16位ADCs成对的同步工作。三个保持信号HOLDA、HOLDB、HOLDC可以启动指定通道组的转换。当三个保持信号HOLDA、HOLDB、HOLDC同时选通时,六通道实现同步采样。ADS8364的输入选择单端输入方式。参考电压VREF为2.5V,输入信号应该在0~+5V的范围内。ADS8364的内部输出缓冲器供电电压BVDD选择由3.3V供电,直接和TMS320LF2407的电源DVDD相连。DSP读取ADS8364的转换结果是通过访问外部的I/O空间实现的,本系统由I/O引脚IOPF1和IS信号共同选通ADS8364。DSP的复用引脚BIO/IOPC1用作IOPC1功能,它用来给ADS8364复位。给ADS8364复位是为了保证DSP从ADS8364中读出的数据转换结果顺序依次是通道A0、A1、B0、B1、C0、C1,否则通道的顺序是随机的,DSP将无法正确存储数据。

2、测频通道的设计

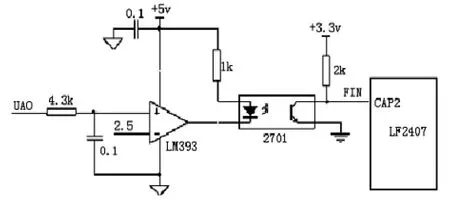

测频通道的功能是完成基波频率的测量,要求精确到±0.01Hz。它通过TMS320LF2407的事件管理器中的捕获单元实现,原理如图2所示。

TMS320LF2407的事件管理器模块包括EVA和EVB,每个模块都包括通用定时器、比较单元、捕获单元等。在本文中应用的是EVA模块中捕获单元2,选择通用定时器2作为它的时基,外接捕获引脚CAP2。捕获单元在CAP2出现跳变时被触发,通用定时器T2的计数值被捕获并存入到一个2级深的FIFO栈中备用。

图2 测频通道原理图

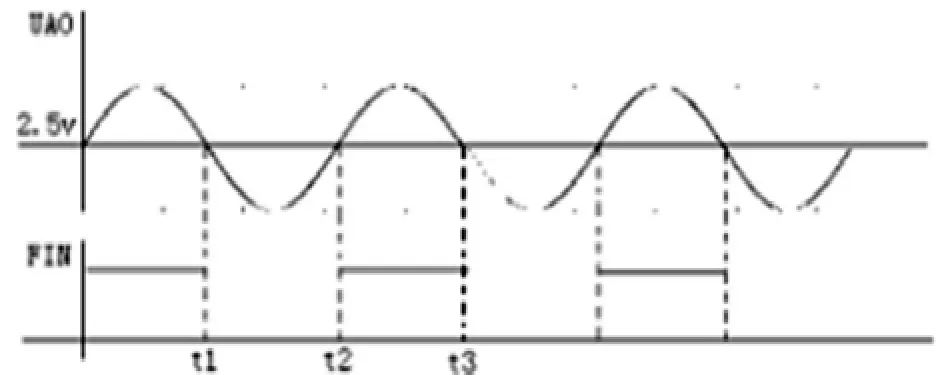

本系统中取A相电压的频率进行计算。由图2可以看出,当UAO≤2.5V时,LM393输出负的最大值, 光电耦合器 2701 导通,FIN=‘0’(低电平);当UAO>2.5V 时,LM393输出正的最大值,2701 截止,FIN=‘1’(高电平)。原理时序如图3所示。在t1时刻,FIN端的信号发生由高电平到低电平的跳变,被DSP的引脚CAP2捕获 (将CAP2设置为检测下降沿),此时通用定时器2的计数值存放在CAP2FIFO寄存器的底层;在t2时刻,FIN端的信号又发生跳变,但是由低电平到高电平,所以对CAP2无影响;在t3时刻,FIN端的信号又发生由高电平到低电平的跳变,CAP2第二次把它捕获,此时通用定时器2新的计数值存放在CAP2FIFO寄存器的顶层;两次的时间差即是A相电压的周期,从而可得A相电压的频率。

图3 测频时序图

由以上分析可知道,只要对方波信号的连续的两个下降沿进行捕捉,得到两个计数值,且这两个计数值处于在定时器的同一个计数周期内,即计数无溢出,那这两次计数值的差值就是方波信号的周期。设定时器的计数周期为Tcount,待测信号的周期为TS,那么,要保证在定时器的一个计数周期内捕获到两个上升沿,Tcount与Ts应有如下关系:

2Ts<Tcount<3Ts

所测量的信号的频率在40Hz到60Hz之间,典型值为50Hz。也就是说TS的典型值为0.02s,这就要求设置定时器的计数周期在0.04s至0.06s之间,本系统的CPUCLK为40MHz,定时器的计数值为最大65536,如果定时器直接使用内部时钟为时钟源,则最大计数时间周期为:

因此,不能直接使用内部时钟作为时钟源,应对其进行预定标, 预定标因子 N(1,2,4,8,16,32,64,128)应满足:

0.04 <N×0.0016<0.06

得25<N<37

所以取N=32,同时计数周期值设置为:0x0ffff。

需要说明的是,这种方法的目的是简化软件中读取的计数值的处理。所以即使不这样做,在程序中考虑到计数器的溢出,将其对65536取模值也得到同样的结果。

四、功能模块软件设计举例

测频功能模块是由DSP的捕获单元实现的。软件部分主要包括捕获单元的初始化和测频子程序的设计。

下面是本系统的捕获单元的初始化程序:

*T2CON=0X1500;计数模式为连续增计数,时钟源为内部CPU时钟,使用自身的周期寄存器;

*T2PR=0X0FFFF; 周期寄存器设为最大值;

*T2CNT=0X00;计数器清零;

*CAPCONA=0X0A020;使能捕获单元1和2,选择通用定时器2,检测下降沿;

*IMR=*IMR|0X08;允许优先级 4 中断;

*EVAIFRC=0X0FFFF;清中断标志;

*EVAIMRC=*EVAIMRC|0X02;捕获单位 2 中断使能;

*T2CON=*T2CON|0X40;定时器 2 脱离复位;

在测频子程序中,查询FIFO状态寄存器的指示,若为01,说明只捕获到一次下降沿,则不对堆栈进行访问;若为10,则连续对FIFO堆栈进行两次访问,得到的两个计数值,调用频率计算子程序进行频率计算;若为11则对FIFO堆栈进行访问,但不对访问得到的计数值进行处理,因为此时FIFO堆栈中两个计数值不是同一个计数周期内的计数值。

五、试验及误差分析

(一)模拟量精度试验

本系统计算模拟量有效值的方法是:把采样值先通过中值滤波算法处理,然后再用付氏算法计算,因为中值滤波算法主要对一些无规律的突发噪声有比较好的滤波作用,而付氏算法主要滤除直流和各整次谐波,而电力系统的运行中,经常受到一些突发噪声的干扰,所以中值滤波算法对误差的改善应该有比较好的效果。

从中值滤波算法的原理可以看出,中值滤波中唯一要设置的参数就是滤波窗口宽度,一般来说,这个宽度不宜设置过大,过大将会影响滤波运算速度,由中值滤波定义可知,窗口宽度最小为3。经过多次试验,本系统选取滤波窗口宽度为7,这样既不会明显减小滤波运算速度,还可以很有效的消除信号的脉冲噪声。

(220.1286,220.0861,220.0535,220.0087,220.1332,220.1769,220.1944,220.2048,220.1851,220.0962,220.0134,119.9803,119.9628,119.9937,220.0251,220.0919,220.1355,220.1683,220.1850,220.1559)是一段时间内计算得到的三相电压有效值数据。找出其中的最大值(220.2048)和最小值(119.9628),计算误差:

可见误差在允许的范围内。

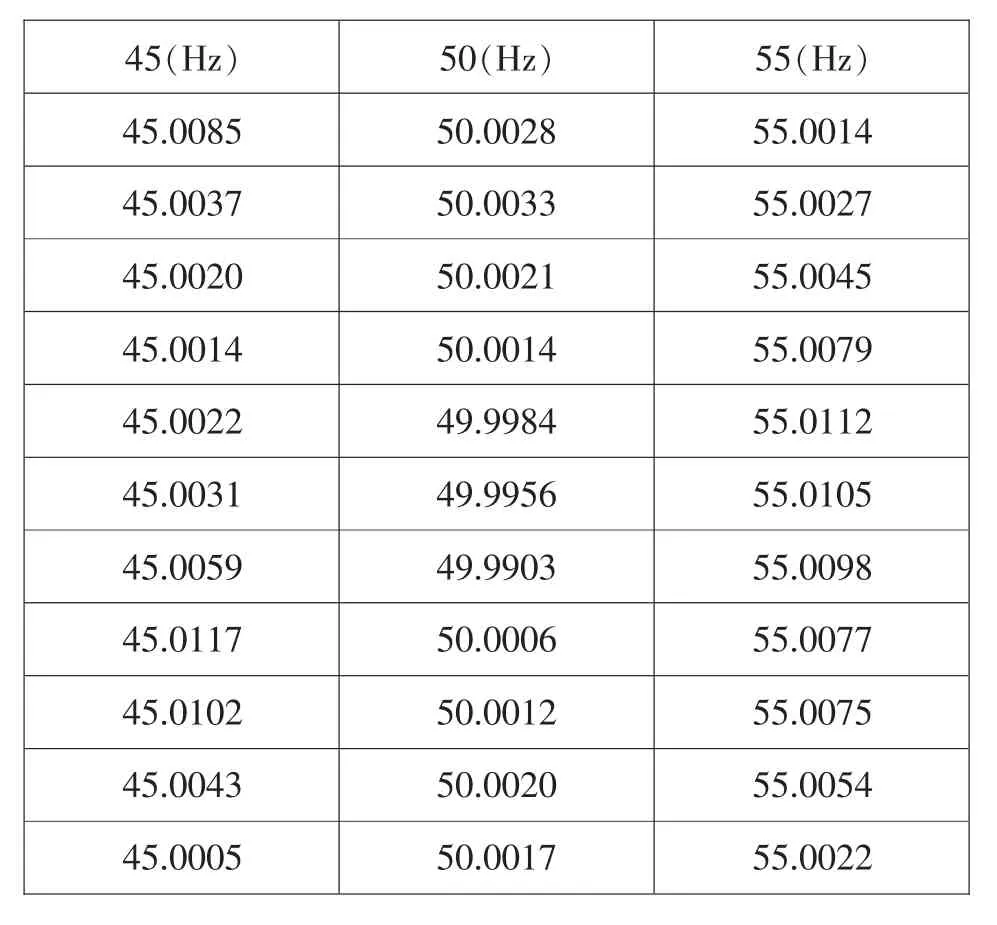

(二)基波频率测量试验

此试验所用的信号是来自信号发生器的标准正弦信号,频率可调。把信号发生器的输出连接到模拟量的输入端,调节信号的幅度超过2.5V后,测频通道启动。

根据电能质量的国家标准,电力系统正常频率偏差允许值为±0.2Hz,当系统容量较小时,偏差值可放宽到±0.5Hz。在此试验中,调节信号发生器,分别使其输出频率为 45Hz、50Hz、55Hz、 峰-峰值为4V的正弦波。表1是一段时间内的试验数据。由试验数据可以看出,频率测量的精度可以精确到±0.01Hz。

表1 频率测量试验数据

六、结束语

本系统是基于DSP的电力信号采集、分析、处理的平台,它完成了三相电压、三相电流有效值的计算,以及基波频率的测量,并且可以实时监测电压质量。在此平台的基础上,还可进行各种电力系统参数和电能质量的分析和处理,并可和上位机实现通信。试验证明,该系统实时性较好,计算精度高,可以较好地满足系统的要求,可作为基于单片机的电能质量监测系统的升级换代产品,具有良好的发展前景。

[1]徐科军,张兴,肖本贤等译.Texas Instruments.TMS320LF/LC24系列 DSP 的 CPU 与外设[M].北京:清华大学出版社,2004.

[2]全国电压电流等级和频率标准化技术委员会.电压电流频率和电能质量国家标准应用手册[Z].北京:中国电力出版社,2001.

[3]中华人民共和国国家质量监督检验检疫总局.GB/T 18657.3-2002.远动设备及系统[M].北京:中国标准出版社,2002

[4]刘和平,王维俊,江渝等.TMS320LF240xDSP C语言开发应用[M].北京:北京航空航天大学出版社,2003.

[5]郑力新,周凯汀,方瑞明,黄东海.DSP多路同步数据采集板设计 [J].华侨大学学报 (自然科学版),2004,25(2):145-149.