一种适合高速接收机的帧同步方法

2013-01-31张波

张 波

(中国电子科技集团公司第十研究所,四川成都610036)

高速接收机是现代通信领域的一个重要发展方向,可广泛应用于气象、海洋、资源、环境、遥感和侦察等众多领域[1]。随着近年来有效载荷技术的发展,对数据传输速率的要求越来越高,国外吉赫兹以上宽带接收机已经投入应用,国内越来越多的单位也已经开展了此方面的研究。帧同步作为数传接收机中的一个重要环节,对最终数据的恢复有着至关重要的影响。高速接收机的帧同步过程与一般接收机相比有以下几点区别:

1)为了实现高速接收,在目前的硬件条件下必须采用并行处理,这样在进行帧同步时通常采用并行帧同步,而并行操作会增加数据相位模糊度,提高假锁概率。

2)在有编译码的情况下,很多时候要求先进行帧同步再译码,此时用于帧同步的数据误码率较高,帧同步检测需要保持一定的容错位数,否则会增加帧同步锁定时间,漏同步概率也会增大,影响后续数据处理。由于数据模糊状态较多,增加容错位数又会进一步提高假锁概率,造成数据错误。

文献[2-4]中对并行帧同步的方法进行了详细说明,文献[5-7]对低信噪比下的帧同步机制进行了研究,但上述文献均没有对并行帧同步时数据的模糊状态进行分析,也没有对低信噪比下并行帧同步可能产生的问题进行关注。本文首先对高速接收机中的并行帧同步流程进行介绍,针对数据中的模糊状态对帧同步的影响,提出了一种新的帧同步方法,并对其性能进行了分析。

1 现有帧同步方法

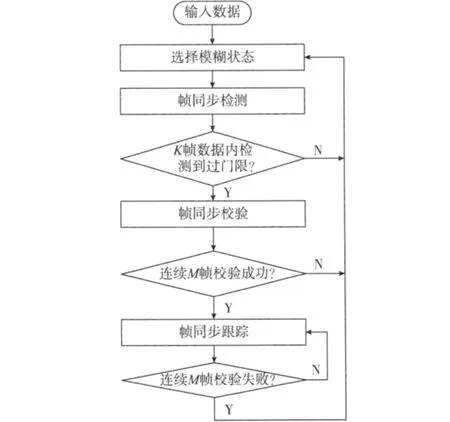

现有的帧同步方法主要分为同步搜索、同步校验和同步跟踪3个环节。在同步搜索状态,预先设置一定的容错比特N,把解调后的数据与预先设置的帧头进行比较,当连续K帧数据中出现与预置帧头的差异小于N bit的数据时,转入帧同步校验状态,否则更新至下一个模糊状态,重新开始搜索。帧同步校验时,当连续M帧数据的固定位置与预置帧头的差异都小于N bit,就认为找到了帧头,从而转入帧同步跟踪状态,否则重新进行帧同步搜索。在帧同步跟踪状态,如果出现连续M帧数据的帧头与预置帧头的差异都超过N bit时,认为帧同步已经失锁,重新开始下一次帧同步搜索过程,否则继续维持帧同步跟踪状态。其中,N称为容错比特,K称为搜索帧数,M称为校验帧数。图1是普遍采用的帧同步流程图,从图中可以看出,模糊状态越多,帧同步搜索时间越长,从后续分析还可以看出,模糊状态数对帧同步性能也有重要影响。

2 改进的帧同步方法

低速接收机处理速率较低,用于帧同步的数据是串行输入的,由于接收机在解调中本身会引入数据相位模糊,因此在帧同步过程中需要根据帧同步字消除模糊状态。当调制方式为BPSK时,接收机解调出的数据存在“0”、“1”翻转的可能,因此在帧同步过程中要利用帧头来对数据进行纠正。如果调制方式为QPSK信号,那解调过程中引入的模糊会更多,包括I、Q分别翻转和I、Q颠倒等,总共有8中可能的模糊,在帧同步过程中需要对这8种情况一一判断,从而确定真实的数据情况。

图1 帧同步过程状态转移图

对于高速接收机,由于现有器件处理速度的限制,数据解调并行进行,这样送给帧同步器的数据除了常规解调中固有的模糊状态外,还引入了串并转换的模糊,接收机处理速率越高,串并转换引入的模糊状态越多。这样在解模糊的过程中很容易把原本不是帧头的数据当作帧头,造成假同步。

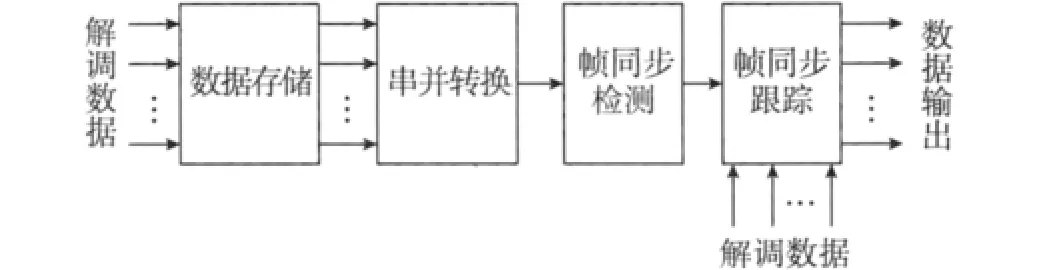

为了解决这个问题,需要对以往的帧同步过程进行改进。由于解调模糊是接收机固有的,不能去除。因此只能通过消除串并转换模糊来减少总的模糊状态。首先,引入串并转换的根本原因是器件处理速度不足,如果把数据速率降低就可以消除串并转换模糊。其次,现在常用的帧同步都是对数据进行连续检测,但对于单纯的帧同步过程来说并不需要对输入的所有数据进行检测,只要能够得到连续的几帧数据,就可以完成帧同步检测。在检测到帧同步位置和状态后便可以对输入的连续数据流进行帧同步跟踪。详细的处理过程如下:

1)对输入的连续多帧并行数据进行存储;

2)以较低时钟从存储器中读出存储的数据,同时进行并串转换,把多路数据恢复成单路数据;

3)对得到的单路数据进行帧同步检测,此过程包含选择不同的解调模糊;

4)在检测到帧同步后,根据帧同步检测过程所花费的时钟个数和模糊状态对输入的并行数据进行调整,转入帧同步跟踪过程。改进后的帧同步流程如图2所示。

图2 改进的帧同步流程

3 帧同步性能分析

3.1 模糊状态分析

设解调引入的模糊状态数为S1,并行路数为P,新方法的模糊状态数为S2。原有方法的模糊状态数S1=S·P,并行路数P越多,则总的模糊状态数S1越大。改进后的方法只有解调引入的模糊状态数,与并行路数多少无关,即S2=S。

3.2 帧同步建立时间

虽然新的帧同步处理过程采用的是降速后的串行数据进行帧同步检测,但由于减少了模糊状态,帧同步检测所用时间与原有方法基本相同。

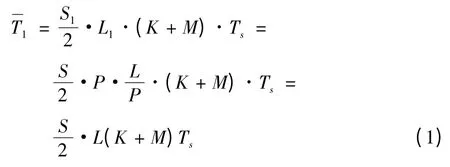

原有方法的帧同步平均建立时间为

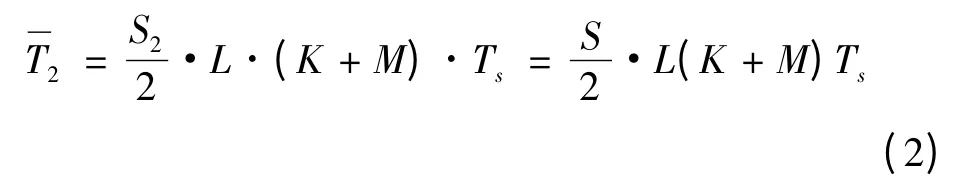

改进方法的帧同步平均建立时间为

式中:L1为并行数据帧长;L为串行数据帧长;S为解调中固有的模糊;P为并行路数;K为搜索帧数;M为校验帧数。

从式(1)、(2)可以看出,虽然改进方法在进行帧同步时是串行处理的,处理速度比并行处理慢,但由于改进方法的模糊状态少,因此与原方法相比,帧同步平均建立时间是相同的。

需要说明的是上述计算中假设误码率较低,此时由于误码造成的假同步对帧同步建立时间的影响很小,并且对两种方法的影响是相同的,不影响比较结论。当解调误码率偏高时有可能会出现假同步,此时帧同步时间会相应增加,下文对此进行具体分析。

3.3 假同步概率

当由于误码或者数据中存在与帧头类似的信息时,可能会造成帧同步错误锁定,此时称为假同步。另外在解模糊的过程中需要对各种可能的模糊状态进行尝试,一些原本与帧头相差很大的数据经过“0”、“1”翻转,I、Q交换,延迟等处理后也可能与帧头一致或类似,在高速并行帧同步中这是造成假同步的一个非常重要的因素。

增加帧头长度、减少帧长、减少模糊状态数可以有效降低假同步概率。由于帧头长度和帧长在系统设计中已经确定,通常不能随意更改,因此只能通过减少模糊状态数来降低假同步概率。

原方法由于模糊状态数多、造成假锁概率高,特别是在帧头较短时,假锁严重。新方法通过串行处理消除了并行数据中包含的帧头相位模糊,减小了假同步的概率,并行路数越多,改善越明显。

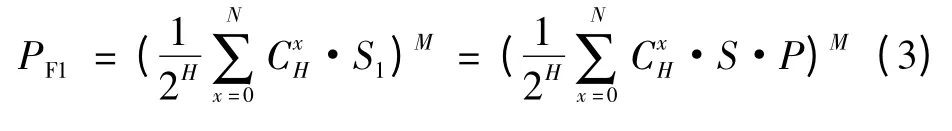

原有方法的假同步概率[8]为

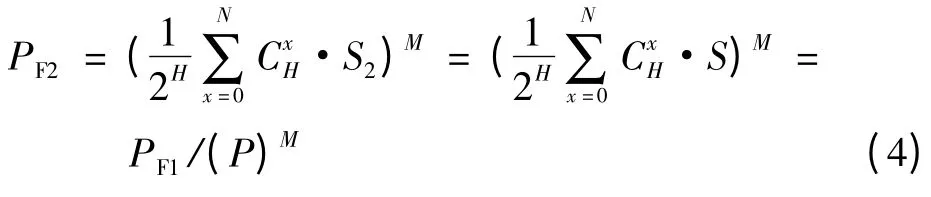

改进方法的假同步概率为

式中:H为帧头长;L为数据帧长;S为解调中固有的模糊;P为并行路数;M为校验帧数。比较式(3)、(4)可知,新方法的假同步概率只有原方法的1/PM。

3.4 漏同步概率

当帧头出现却没检测出来时称为漏同步,漏同步针对的是真实的帧头,这对两种方法是一致的,即

式中:Pe为解调误码率,其余参数定义与前面相同。从式(5)可以看出,容错位数越大、校核帧数越多、误码率越小,漏同步出现的概率越小。由于误码率在解调时已经确定,不能更改,只能通过改变其余两个参数来调整漏同步概率。然而,增加容错位数会提高假同步概率,增加校核帧数会增加帧同步入锁时间。

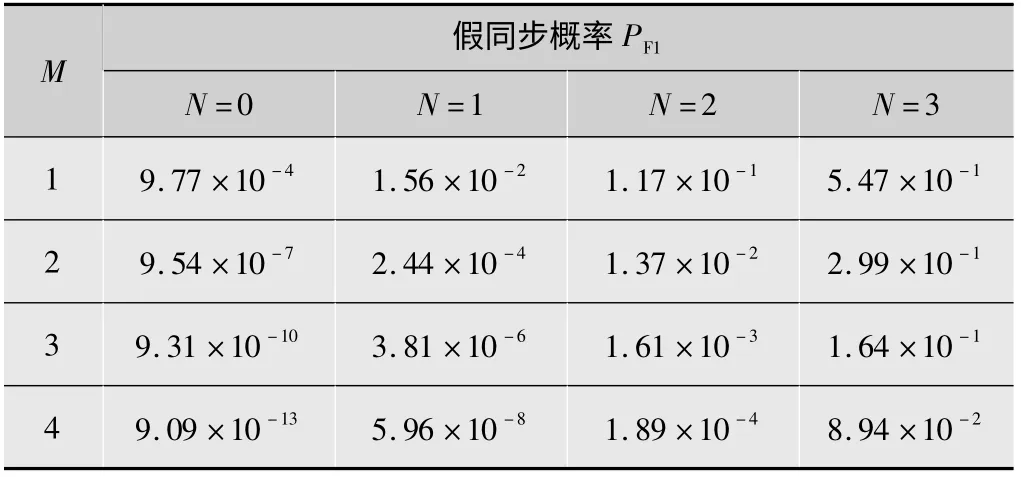

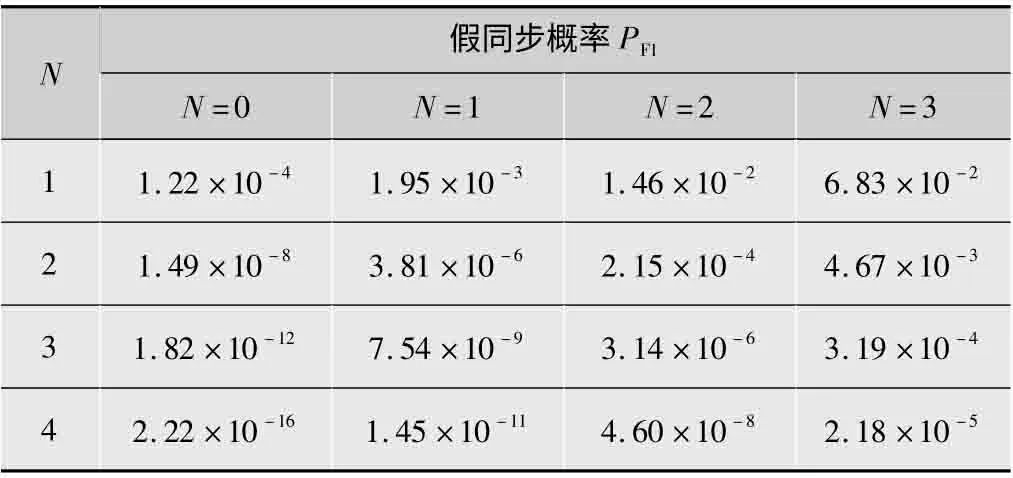

表1和表2是参数不同时两种方法的假同步性能。从表1和表2中可以看出,当选择相同参数时新方法的假同步概率要明显小于原方法,其中校核帧数越多,性能改善越明显。原方法虽然可以通过减少容错位数和增加校核帧数来降低假同步概率,但当解调数据中误码率较高时,如果容错位数太少会导致帧同步建立时间过长甚至不能同步。

表1 原方法的假同步概率,H=16,S=8,P=8

表2 新方法的假同步概率,H=16,S=8,P=8

4 实验分析

在600 Mbit/s接收机中分别采用上述两种方法实现帧同步,比较二者之间的差异。接收机速率600 Mbit/s,调制方式采用QPSK,接收机送给帧同步模块的并行路数P=4,帧长L=8 192 bit。上节在进行理论分析时假设每帧数据是各不相同的,实验中采用循环发送固定帧,一方面是为了测试简便,更重要的是在实际发送数据时常有部分数据是慢变化的,这对帧同步提出了更高的要求。发送固定帧可以很好地模拟这种情况,此时如果信噪比较高,校验帧数M的变化对帧同步性能影响不大,固定取4。采用传统帧同步方法和改进帧同步方法在不同参数时的帧同步情况如表3、表4所示。

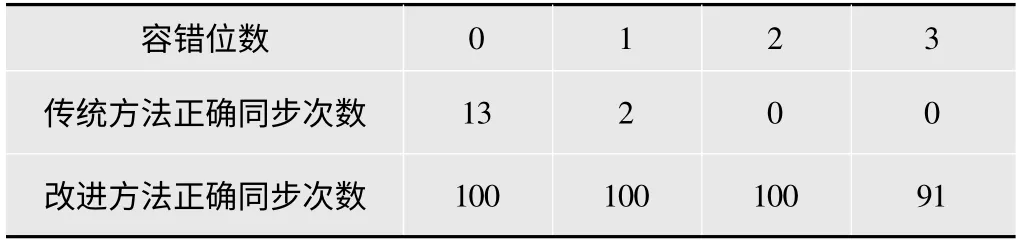

表3 两种方法的正确同步次数比较,统计次数100次,H=16,M=4,Eb/N0=7 dB

表4 两种方法的正确同步次数比较,统计次数100次,H=16,M=4,Eb/N0=4 dB

在表3中,接收信号较强,此时误码很少,传统帧同步方法在容错位数为0和1时,正确同步概率很低,容错位数增加为2和3后,100次测试中无一次正确同步。表4中信噪比进一步降低,此时解调数据包含大量误码,原方法由于模糊状态多在误码的影响下,当容错位数少时不断地处于帧头检测和校核中,造成同步时间很长,甚至不能同步,增加容错位数又会引起假同步。改进方法模糊状态少,在低信噪比仍然能够以较高的概率正确同步,达到了降低帧同步门限的效果。

5结论

针对高速接收机中并行帧同步容易假锁的问题,提出了一种改进的帧同步处理方法。文中对新方法的帧同步平均建立时间、假同步概率、漏同步概率等指标进行了理论分析。从分析结论可以看出,新方法通过减少模糊状态数改善了假锁概率,而假锁概率的降低可以允许更多的容错位数,因此能够降低跟踪门限,提高接收机灵敏度。此方法不受并行路数的影响,特别适用于高速接收机的帧同步检测。

[1]童长海,郑雪峰,郑戈,等.600 Mb/s高速数传接收机的设计与实现[J].遥测遥控,2007(28):30-34.

[2]单宝堂,王华,张健,等.一种并行帧同步设计方案的提出、设计与应用[J].通信与电视,2005(6):61-64.

[3]刘昭,金德鹏,曾烈光.基于连续性判别的并行帧同步系统[J].电子学报,2007,33(7):1178-1182.

[4]陈燕.基于FPGA高速帧同步设计及性能分析[J].信号与信息处理,2010,40(5):25-26.

[5]易智,周亮,刘德伟.一种新的极低SNR下帧同步机制研究[J].通信技术,2009,42(12):204-206.

[6]徐俭.多功能帧同步机在总控和播控系统中的应用[J].电视技术,2009,33(3 ):66-68.

[7]苏承毅,张彧,潘长勇.卷积-RS级联译码器并行帧同步算法及实现[J].电视技术,2010,34(11):48-50.

[8]夏俊.帧同步电路的设计和分析[J].电讯技术,2006(2):155-158.