基于FPGA局部视频图像任意比例缩放系统

2013-01-31孙俊喜顾播宇曹永刚宋立维

谭 亮,孙俊喜,顾播宇,曹永刚,宋立维

(1.长春理工大学 电子信息工程学院,吉林 长春130022;2.中国科学院 长春光学精密机械与物理研究所,吉林 长春130033)

目前,大多数视频缩放系统应用于2种不同视频格式之间的转换,例如SVGA格式(800×600)转换为XGA格式(1 024×768)[1],因此缩放比例不是任意的。而且这些方法是针对整幅图像,且工作在不同的时钟频率。然而在定位和监视系统中,需要详细地了解和操作截取的局部图像时,由于显示屏幕分辨率的限制,不能迅速并明显地检查每一处区域和名字的信息。同样在基于FPGA车牌字符识别系统中,为了保证字符分割后大小不一的车牌字符图像以一致大小进入识别阶段,几何归一化的实现非常重要。因此,根据上面的情况,工作在同一时钟频率的任意比例局部视频图像缩放操作是必要的。目前,大多数视频缩放操作是先进行整幅图像的缩放,然后截取需要操作的局部图像,这种方法既浪费时间又增加了操作的复杂性。文献[2]提出了一种针对局部图像缩放的方法,然而它采用的是先整体放大局部图像,再整体缩小局部图像来实现局部图像的缩放,这样增加了插值运算的复杂度,不能满足水平放大垂直缩小或者水平缩小垂直放大的情况。根据文献[3-4],采用一维缩放结构即水平和垂直方向分开独立处理,不仅降低了插值运算的复杂度,而且提高了系统处理的效率。

由于FPGA内部资源的限制,文献[5-6]提出一种采用两片片外存储器实现图像乒乓缓存的方法,但是它采用一次二维缩放结构[7],即将二维块状图像数据直接缩放到目标大小。这种方法会增加逻辑资源的使用和插值运算的复杂性,相比于文献[2]采用一片片外RAM,硬件设计成本和逻辑控制复杂性也会增加。

本文提出了一个能处理RGB和YUV 4∶4∶4格式的实时局部视频图像缩放系统硬件设计,通过FPGA验证,本设计能够截取需要缩放的视频局部图像,并准确地缩放到规定大小,同时保留视频图像的重要信息。

1 图像缩放原理

本文提出的视频局部图像缩放架构如图1所示。

缩放流程如下:

图1 视频局部图像缩放架构

1)系统实现水平、垂直同时缩小或者水平放大、垂直缩小:截取模块通过对行有效信号和时钟信号计数来选择局部图像所在的区域;数据缓存模块1交替缓存截取的图像数据,然后输出需要进行水平插值的数据;水平插值后的数据经过数据选择模块1进入数据缓存模块2;之后连续两行图像数据经过数据缓存模块2进入垂直插值模块;片外存储器SDRAM在控制器写信号的控制下缓存垂直插值后的一帧数据,然后在读信号的控制下输出需要显示的数据给数据选择模块3输出。

2)系统实现水平、垂直同时放大或者水平缩小、垂直放大:通过对行有效信号和时钟信号计数来选择局部图像所在的区域;数据缓存模块1交替缓存截取的图像数据,然后输出需要进行水平插值的数据;水平插值完后的数据经过数据选择模块1进入片外存储器SDRAM;片外存储器在控制器的写信号控制下,缓存经过水平插值后的数据,然后输出数据到数据缓存模块2;数据缓存模块2在读写信号的控制下,缓存并输出连续两行需要插值的图像数据到垂直插值模块;完成垂直插值后的放大数据进入数据选择模块3输出。

本设计中给片外存储器配置为4端口(2读2写端口),因此能够同时处理RGB或者YUV 4∶4∶4这3个通道的数据。该设计使用了一片片外存储器来存储图像数据,充分利用了片外存储器的资源,并获得了很好的效果。

插值系数生成模块用来计算:1)插值系数:dx,dy;2)目标图像坐标映射到原始图像的坐标:行坐标y、列坐标x。列坐标x是用来缓存截取图像数据的数据缓存模块1的读地址。根据行坐标y,图1所示片外存储器控制器产生读写信号控制片外存储器。水平插值系数和列坐标计算原理如图2所示。

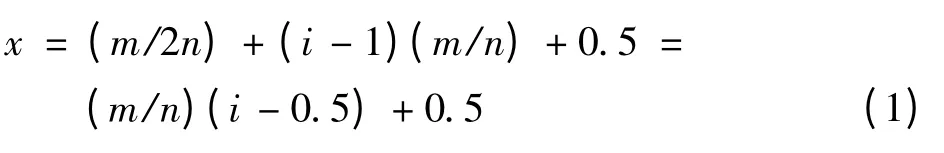

插值系数及列坐标计算为

图2 水平插值系数及列坐标计算原理

式中:i是目标图像的列坐标,范围为(1,n);m,n为原始局部图像和目标局部图像的水平分辨率。由于FPGA不能计算浮点数,因此根据文献[8],等式右边扩大2a倍,a由计算精度决定,本设计a取12。

所以式(1)可替换为

x的高(b-12)位是目标图像列坐标,低12位是水平插值系数,b是x的数据位宽。

数据选择模块用来选择数据进入下一个模块:根据数据选择信号,数据选择模块选择放大或者缩小后的数据进入下一个模块。如图1所示,例如当系统实现垂直放大时,数据选择信号置“1”,数据选择模块4选择放大后的垂直方向数据进入片外存储器缓存,否则选择缩小后的数据进入数据选择模块3。

如图3所示,数据缓存模块2包含两个存储器。每一个存储器由n个寄存器组成,n为原始图像水平分辨率。控制模块通过判断目标图像坐标映射到原始图像坐标的行坐标值来产生读写信号控制2个存储器,其中读信号1控制存储器1输出数据到存储器2,读信号2控制存储器1输出数据到垂直插值模块。这个坐标值代表了需要插值的连续两行数据,将坐标值存储在一个由r个寄存器构成的存储器中,r是坐标值的个数。当系统实现缩小操作时,如果这个坐标值不等于0,存储器1的读信号2和存储器2的读信号置“1”,同时输出连续两行有效数据到垂直插值计算模块;当系统实现放大操作时,如果第m+1个寄存器的值不小于第m个寄存器的值(m范围为(1,r)),存储器1的读信号1和存储器2的写信号置“1”,存储器1的读信号2和存储器2的读信号同为行有效信号。而且,为了确保需要插值的两个数据(P1和P2)和插值系数能同时进入插值计算模块,当存储器1的读信号2和存储器2的读信号都为“1”时,两个存储器能在一个时钟同时输出相邻两行需要插值的两个像素数据。

图3 数据缓存模块2

2 实验结果

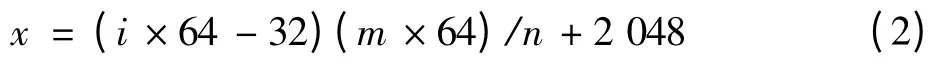

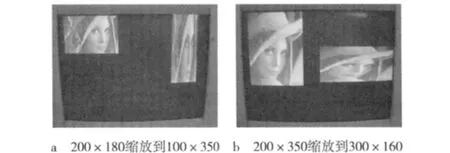

本文提出的基于FPGA视频局部图像任意比例缩放架构程序部分采用Verilog语言编写实现,FPGA芯片选择Altera公司的EP2C70F896C6N型号,其包含68 416个逻辑单元和1 152 000 bit存储容量。设计资源的使用如表1所示:原始局部图像分辨率为200×180和200×350,如图4a所示;目标图像分辨率为100×350和300×160,如图4b所示。

表1 设计资源使用

图4 实验结果

实验结果如图4所示,来自摄像机的视频局部图像被放大或者缩小然后在VGA上显示。VGA的分辨率为640×480,可以看出本设计工作良好,并能在显示器上高质量地显示缩放后的视频图像。证明了本文的架构在功能和时序上的正确性。

3 结论

本文讨论了视频局部图像缩放架构并用FPGA实现。系统利用了FPGA的强扩展性和重建性来实现图像缩放,因此能够根据实际需要来进行调整而不需要改变其硬件结构,所以系统具有较好的适用性和灵活性,而且片外存储器有足够的存储资源来存储一帧图像数据,能够很好地实现分辨率高达1 024×768任意比例的视频图像实时缩放。

实验结果表明,算法的实现比较简明,从而大大降低了资源的使用和设计成本,而且图像缩放系统能够高质量地输出视频图像数据,这些都证明了本文提出的硬件架构是可行的,能够作为几何归一化操作很好地融合到车牌字符识别系统中。

[1]RAMACHANDRAN S,SRINIVASAN S.Design and FPGA implementation of a video scalar with on-chip reduced memory utilization[C]//Proc.the Euromicro Symposium on Digital Systems Design.[S.l.]:IEEE Press,2003:206-213.

[2]袁杰,姚赛杰,朱毅,等.视频图像局部实时无级缩放装置:中国,10025624.8[P].2009-08-19.

[3]XIANG Zuquan,ZOU Xuecheng,LIU Zhenglin.An high quality image scaling engine for large-scale LCD[C]//Proc.the International Conference on Signal Processing.Wuhan,China:IEEE Press,2006:16-20.

[4]FENG Tao,XIE Wenlu,YANG Lianxing.An architecture and implementation of image scaling conversion[C]//Proc.the International Conference on ASIC.Shanghai,China:IEEE Press,2001:409-410.

[5]王阳,赵春喜,郭山河.基于一维数据插值算法的图像放大引擎[J].吉林大学学报:信息科学版,2010(7):410-413.

[6]张陌,程永强.基于FPGA的D1到XGA图像放大引擎[J].太原理工大学学报,2008(5):42-44.

[7]孙红进.FPGA实现的视频图像缩放显示[J].液晶与显示,2010(2):130-133.

[8]郑俊杰,陆虎敏,方向忠.基于自适应插值算法的视频图像缩放技术及其FPGA实现[J].航空电子技术,2008(3):46-50.