部分耗尽SOI ESD 保护电路的研究

2012-12-22汤仙明韩郑生

汤仙明,韩郑生

(1.杭州士兰微电子股份有限公司,杭州310012;2.中国科学院微电子研究所,北京100029)

SOI(Silicon-On-Insulator,绝缘衬底上的硅)技术是在顶层硅和背衬底之间引入了一层埋氧化层。SOI技术与体硅技术相比具有很多优点:全介质隔离;无闩锁效应;源、漏寄生电容小;易于形成浅结;工艺更为简单;较好地抑制短沟道效应;低压低功耗[1]。

然而随着SOI 技术的快速发展,以前不被人重视的SOI 电路的ESD(Electrostatic Discharge,静电放电)保护问题,逐渐成为SOI 电路广泛应用的一个主要障碍[2-3]。由于SOI 技术的器件是被埋氧隔离层和LOCOS 场氧隔离层包围,它们都是热的不良导体。在静电放电时产生大量的热很难耗散出去,导致SOI 器件比体硅器件更容易失效,因此SOI 电路的ESD 保护问题要比体硅更为严重。

1 SOI ESD 保护电路设计

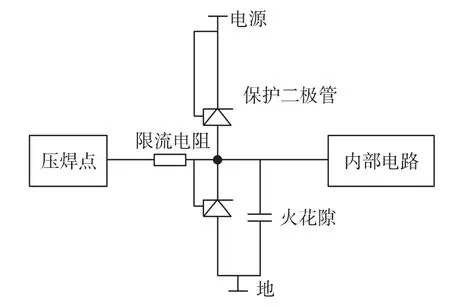

部分耗尽CMOS/SOI 的ESD 机理和体硅CMOS的差别很大,一般不能直接将体硅的ESD 结构直接移植到SOI 上来,但是二者ESD 保护电路的基本形式是类似的,如图1 所示都是由限流电阻,保护二极管和用于瞬间脉冲电压放电的电火花隙结构组成的。

图1 ESD 保护电路的基本形式

SOI 和体硅的最主要的区别在于保护二极管的结构不同,在体硅技术中常用扩散平面结来做保护二极管,此时二极管的结面积为底面平面结加上四周侧面结;而薄膜SOI,硅膜是耗尽的,PN 结是横向侧面结。因此在SOI 工艺中,如果按照体硅工艺制作ESD保护二极管,将是任何SOI 电路难以承受的[4]。

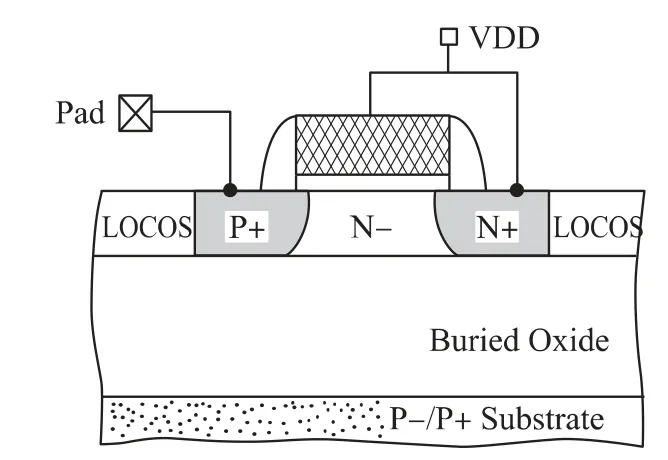

因此采用栅控二极管[2,4-5]作为保护二极管,栅控二极管的结构如图2 所示,它是一种不定向工作双极型绝缘栅横向晶体管(Lubistor)。

图2 栅控二极管的结构示意图

这种器件具有三极管特性并可以传输高达105A/cm2的电流密度[1]。正是由于栅控二极管很高的电流驱动能力,所以被用作SOI ESD 保护二极管。

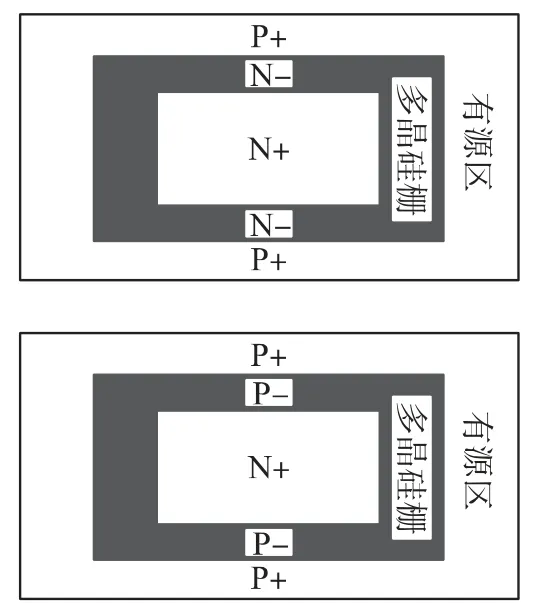

我们在设计中为了抑制边缘漏电和增加结面积,栅控二极管采用了环形栅结构[7],即p+注入的源/漏在环栅结构的外部,n+注入的源/漏在环栅结构的内部,如图3 所示。限流电阻我们选用的是P+有源区电阻和多晶硅电阻,电火花隙采用的是多晶硅梳状放电栅[6]。

图3 栅控二极管的版图

2 实验

采用SIMOX 和Smart-Cut 两种SOI 材料,工艺上与标准的1.2 μm 部分耗尽CMOS/SOI 工艺兼容。LOCOS 场氧隔离:SIMOX 基片采用传统的LOCOS 隔离,Smart-Cut 基片采用两步LOCOS 隔离;采用双栅结构:NMOS 采用N+多晶硅栅,PMOS 采用P+多晶硅栅;栅氧厚度为20 nm;沟道掺杂采用深浅两次注入;采用LDD 结构;以及Ti 自对准硅化物工艺。

ESD 实验是在宜硕科技(上海)有限公司做的,人体 放 电 模 型(HBM)[8]是 采 用MIL-STD-883C method 3015.7 工业标准,机器放电模型(MM)是采用EIAJ-IC-121 method 20 工业标准。静电放电失效判断采用相对I-V 漂移即当IC 被ESD 测试后,自输入/输出管脚看进IC 内部的I-V 特性曲线漂移量在30%就判定该器件已被ESD 所损坏了。

3 结果和分析

3.1 初始硅膜厚度的影响

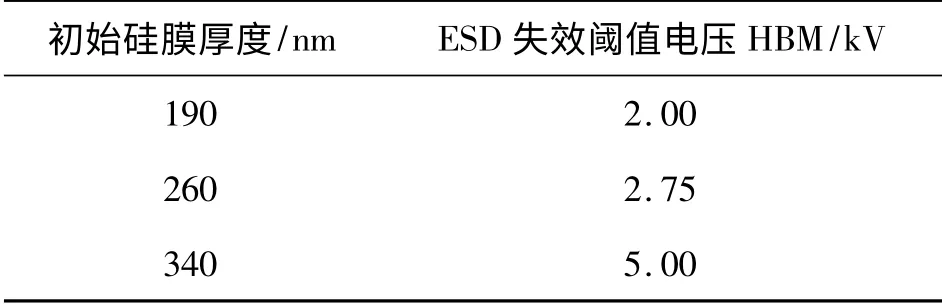

栅控二极管PN 结是横向侧面结,因此SOI 材料初始硅膜厚度对保护电路的抗ESD 能力影响很大,初始硅膜厚度的增加能在很大程度上增加结面积和电流驱动能力,进而提高保护电路的抗ESD 能力。

表1 初始硅膜厚度对ESD 失效阈值电压的影响

表1 给出了L=6 μm,W=200 μm,带火花隙结构的保护电路在不同硅膜厚度下ESD 失效阈值电压,可以看到随着初始硅膜厚度的增加保护电路的抗ESD 性能有了显著增加。初始硅膜厚度为190 nm 和260 nm 是SIMOX 材料,340 nm 是Smart-Cut材料,后面如果没有特别说明,都是采用的190 nm的SIMOX 材料。

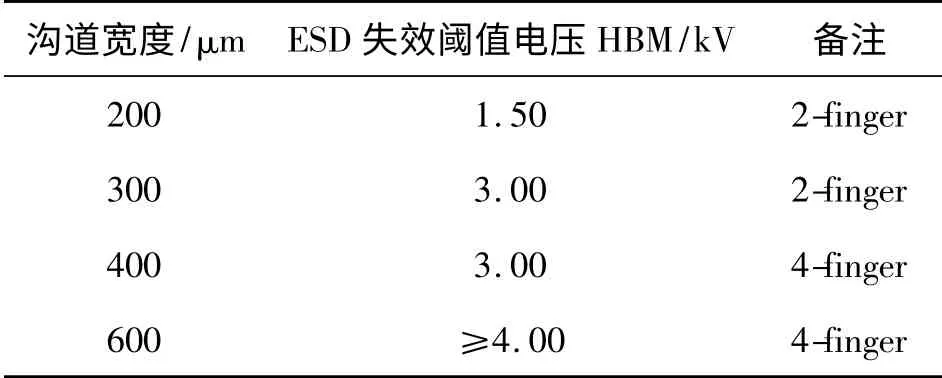

3.2 沟道宽度的影响

在体硅器件中,增加保护二极管的沟道宽度,保护电路的抗ESD 性能会相应的改善。在SOI 中,也可以通过增加沟道宽度的方法来提高保护电路的ESD 失效阈值电压。

表2 沟道宽度和ESD 失效阈值电压的关系

表2 给出了L=6 μm 的保护电路不同沟道宽度和ESD 失效阈值电压的关系,可以看到随着沟道长宽的增加,器件的抗ESD 性能有明显的增加。

由于采用的是多指结构,多指的长度和数量也会影响到器件的抗ESD 能力,同样是2-finger 结构300 μm 的器件比200 μm 的器件抗ESD 能力提高了将近一倍,而4-finger 结构的400 μm 的器件和2-finger 结构的300 μm 的器件抗ESD 能力是一样的,原因是多指器件在ESD 放电情下,会发生不均匀导通的情况,通常只有2 ~3 支finger 会先导通而其他的finger 没有起到泄放电流的作用。但是版图布局和面积考虑又都不允许finger 做的太长,因此设计时需要在这两方面折中考虑。

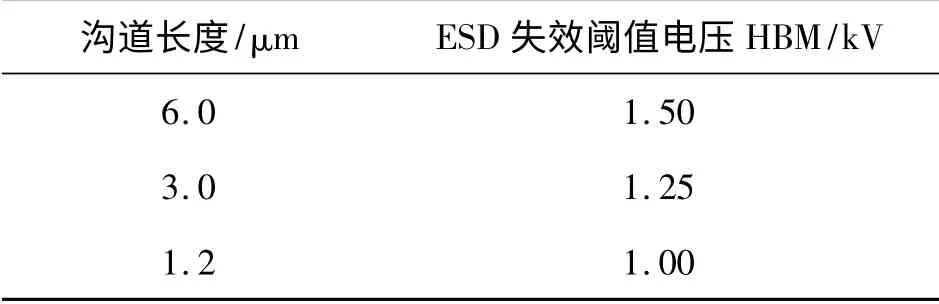

3.3 沟道长度的影响

不同的沟道长度对保护电路的抗ESD 性能也会有影响。在1.2 μm 部分耗尽CMOS/SOI 工艺下随着沟道长度的减小,保护电路的抗ESD 性能会有一定的退化。表3 给出了W=200 μm 的保护电路不同沟道长度的ESD 失效阈值电压。

表3 沟道长度和ESD 失效阈值电压的关系

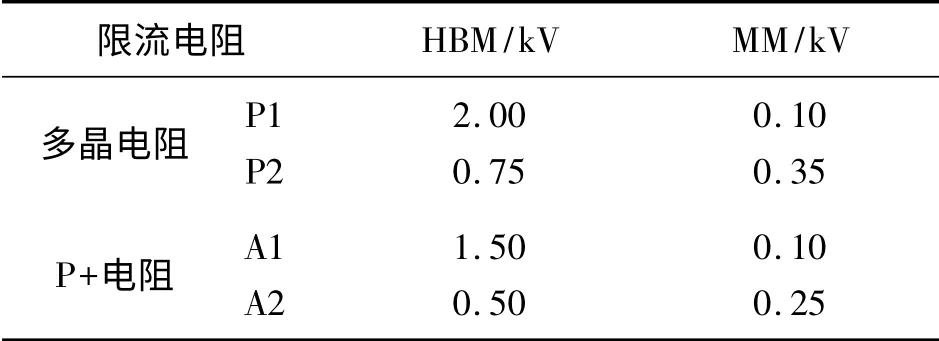

3.4 限流电阻的影响

电阻具有阻挡电流的能力,因此经常与其它器件共同使用以提升该器件的ESD 耐受能力。限流电阻可以是扩散电阻或者多晶硅电阻。

表4 限流电阻的影响

表4 给出了限流电阻对保护电路抗ESD 性能的影响,其中它们的保护二极管尺寸都是一样的(L=3 μm;W=200 μm)。在版图设计时,P1、P2 和A1、A2大小分别相同,只是P2、A2 要比P1、A1 窄很多,因此P2、A2 电阻阻值要比P1、A1 大很多。由于存在硅化物工艺,使得无论是多晶电阻还是P+有源区电阻都比没有做硅化物的要小的多,经过测试得到多晶硅电阻P1 阻值为50 Ω 左右,P2 为150 Ω 左右。

人体放电模型(HBM)和机器模型(MM)是两种不同的静电放电模型,它们的区别MM 放电时间更短,电流更大。200 V MM 的放电峰值电流为4 A,而2 kV HBM 的放电峰值电流只有1.33 A。

对于HBM 放电模型,宽的电阻P1、A1 要比窄的电阻P2、A2 抗ESD 性能要好。主要可能是因为在相同的功率,窄的电阻要比宽度更容易被烧毁。在HBM ESD 电流泄放时,在保护二极管失效以前,窄的限流电阻就已经烧毁了;

而对于MM 放电模型情况恰恰相反,电阻大的情况抗ESD 性能要比电阻小的都要好。主要可能是因为在MM ESD 电流泄放时,功率并不是很大,但是电流比较大。宽的电阻P1、A1 阻值比较小,使得流过栅控二极管的电流比较多,过电流栅控二极管在电阻烧毁之前就的热致二次击穿。

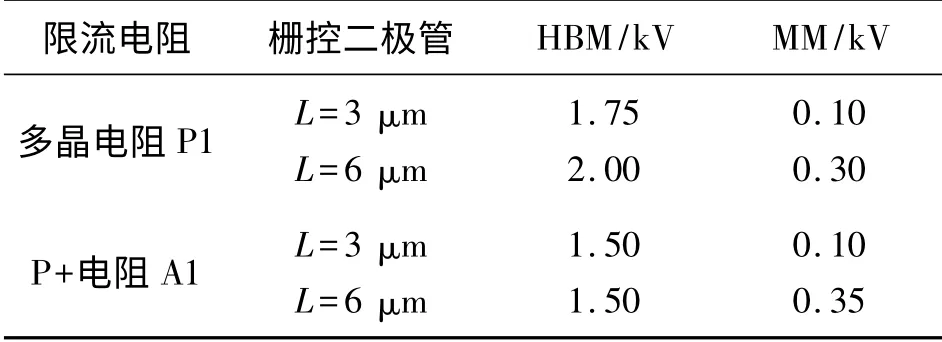

如果限流电阻后面的栅控二极管用L = 6 μm,W=200 μm 代替L=3 μm,W=200 μm,则可以提高保护电路抗MM ESD 的能力。

表5 相同限流电阻与不同栅控二极管组合的保护电路的ESD 失效阈值电压

从表5 中可以看出,对于人体放电模型HBM,P+电阻加L=6 μm 栅控二极管组合的抗ESD 能力和P+电阻加L=3 μm 栅控二极管组合抗ESD 能力几乎相同;然而对于机器放电模型MM 来说,P+电阻加L=6 μm 栅控二极管组合的抗ESD 能力(350V)要比P+电阻加L=3 μm 栅控二极管组合(100 V)高很多,这个结论对多晶硅电阻也适用。

造成这种情况的原因可能是,L=6 μm 的栅控二极管能承受二次崩溃电流(It2)要比L=3 μm 的栅控二极管的大。相同的电阻具有相同的限制电流的作用,对于人体放电模型HBM,由于放电电流比较小,在电阻烧坏之前,限流电阻限制的放电电流它们俩都能承受,因此保护电路能力取决于电阻的抗ESD 能力。

然而对于机器放电模型,由于放电电流比较大,限流电阻限制的放电电流,L=3 μm 的栅控二极管不能承受而L=6 μm 的栅控二极管可以承受,因此保护电路能力取决于栅控二极管的抗ESD 能力。

3.5 电火花隙的影响

由于SOI 器件能量耗散的能力较体硅器件差,因此在保护电路中加入用于瞬间脉冲电压放电的电火花隙结构,以减少保护电路中其它器件的能量耗散。L=6 μm;W=200 μm 的保护电路在没有电火花隙结构的情况下的抗HBM ESD 能力仅有1.50 kV 左右,而加上电火花隙结构之后抗ESD 能力能够提高到2.00 kV 左右。

4 结论

本文针对SOI 电路抗ESD 能力要比体硅差的缺点,设计一种适用于SOI 材料的栅控二极管结构的保护电路。通过实验研究了影响保护电路抗ESD 性能的主要因素:SOI 材料、栅控二极管的沟道长度和沟道宽度,限流电阻以及电火花隙结构等,发现综合考虑这些因素之后,也能够获得让人可以接受的抗ESD性能,而且并不需要增加额外的工艺步骤和掩膜版。

[1] Colinge J P.Silicon-on-Insulator Technology:Materials to VLSL[M].Boston:Kluwer Academic Publishers,1991.

[2] Voldman S,Hui D,Warriner L,et al.Electrostatic Discharge(ESD)Protection in Silicon-on-Insulator(SOI)CMOS Technology with Aluminum and Copper Interconnects in Advanced Microprocessor Semiconductor Chips[C]//EOS/ESD Symp.,1999,105-115.

[3] Voldman S,Assaderaghi F,Mandelman J,et al.Dynamic Threshold Body and Gate-Coupled SOI ESD Protection Networks[J].Journal of Electrostatics,1998,44:239-255.

[4] 刘文安,罗来华,赵文魁,等.TFSOI/CMOS ESD 研究[J]. 微电子学与计算机,2000,(6):36.

[5] Voldman S,Schulz R,Howard J,et al. CMOS-on-SOI ESD Protection Networks[J]. Journal of Electrostatics,1998,42:333-350.

[6] 刘新宇,韩郑生,周小茵,等.CMOS/SOI 64Kb 静态随机存储器[J].半导体学报,2001,21(1):47.

[7] 张兴,石涌泉,黄敝. 高速CMOS/SOI 电路输入保护网络的优化设计[J].微电子学与计算机,1993,(1):41-44.

[8] 王颖. MOS 集成电路ESD 保护技术研究[J]. 微电子技术,2002,(1):24-28.