基于Hyperlynx 的变电站状态监测无线节点信号完整性仿真分析

2012-12-22吴明赞

吴 超,吴明赞 ,李 竹

(南京理工大学自动化学院,南京210094)

随着电子系统中系统时钟和逻辑频率的迅速提高和信号边沿不断变陡,印刷电路板的连接线和板层特性对系统电器性能的影响也越发严重。当印刷电路板处于高频高速工作状态时,互连关系必须以传输线进行考虑,如果不满足系统的信号完整性要求,可能导致系统工作不稳定[1]。良好的高速电路设计要求具备信号完整性包括:避免传输线效应,选择合适的高速信号端接方式,高速信号间串扰尽可能小[2]。本文针对变电站电气设备状态监测系统中出现的信号完整性问题进行了研究,利用仿真软件HyperLnx 对系统中关键信号线进行仿真来分析系统的信号完整性。

1 信号的反射与串扰研究

信号沿传输线传播时,其路径上的每一步都有相应的瞬态阻抗。如果互连线的阻抗是可控的,那么瞬态阻抗就等于线的特性阻抗。无论什么原因使阻抗发生了改变,部分信号都将沿着与原传播方向相反的方向反射,而另一部分将继续传播。反射是一种较为常见的信号完整性问题,反射会使信号质量下降,引起振铃现象。

在高速PCB 设计中,传输线上的信号反射主要由于阻抗不匹配引起的,所以抑制发生的主要方法就是进行传输线的端接。通常所采用的端接方式有两种,一种是使负载端阻抗与传输线匹配,即并行端接,这时传输线负载端的反射系数为零,反射在负载端被消除;另一种是使源端阻抗与传输线特性阻抗匹配,即串行端接,这时源端反射系数为零,反射将在其到达源端时被消除。

串扰是信号在传输线上传播时,由于电磁耦合而在相邻的传输线上产生不期望的电压或电流噪声干扰,信号线的边缘场效应是导致串扰产生的根本原因[3]。我们称施加噪声的网络线为干扰线,有噪声产生的网络线为受扰线。系统中两条网络之间的容性耦合和感性耦合是引起串扰的两个重要原因。为了减小串扰,我们可以从以下2 个方面进行考虑[4]:

(1)布线条件允许的情况下,尽量拉大传输线间的距离,尽量减小相邻传输线间的平行长度。

(2)通过端接,使传输线远端或近端的终端阻抗与传输线匹配,可大大减小串扰的幅度。

2 状态监测系统无线节点的SI 仿真

2.1 节点构成

状态监测系统的原理框图如图1 所示,由CC2430 通信模块接收状态监测无线传感器网络节点传输来的状态参数数据,将接收到的数据送入处理器模块,处理器选用TI 公司的TMS320F2812,GPRS 模块主要由GPRSMC55 芯片构成,实现与Internet 网连接。其中微处理器模块外扩了SRAM,SRAM 和DSP 的接口信号属于高速信号,为保证数据的正确性必须对其中的信号进行完整性仿真分析,有效地减小反射和串扰对信号的影响。

图1 状态监测系统原理框图

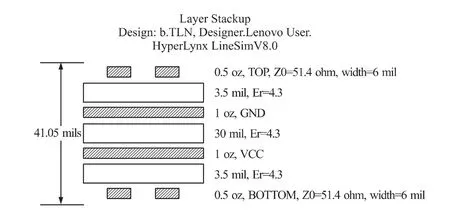

2.2 PCB 板层叠设计

在仿真分析前,需要对PCB 层叠进行设置。这是系统进行信号完整性仿真分析的基础[5]。Hyper-Lynx 的LineSim 和BoardSim 中都包含一个强大的层叠编辑器。通过它可以对PCB 进行层叠设计。该节点采用4 层电路板,相对介电常数εr为4.3 的FR4 材料,走线特性阻抗设定为51Ω,PCB 的厚度为1.05mm。具体层叠参数如图2 所示。

图2 PCB 板层叠设置

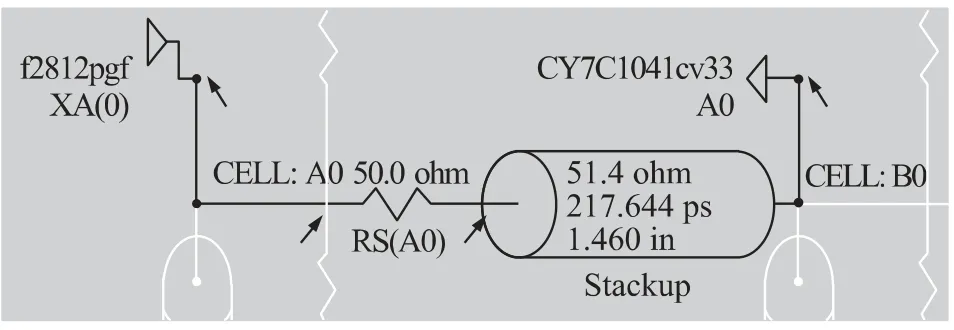

2.3 布线前反射仿真

根据前面的分析,减小和消除反射的方法是对发送端或接收端进行终端阻抗匹配,从而使源反射系数或者负载反射系数为零。以SRAM 地址线XA0 为例,对地址线进行串联端接仿真。图3 为串联端接原理图。由于在实际情况中不可能把端接电阻值放置距离驱动器端很近[2],所以在驱动端和串联端接电阻之间加入一段导线,以使仿真模型与实际情况相符。如图4 所示。

图3 串联端接原理图

图4 实际串联端接原理图

表1 反射仿真数据

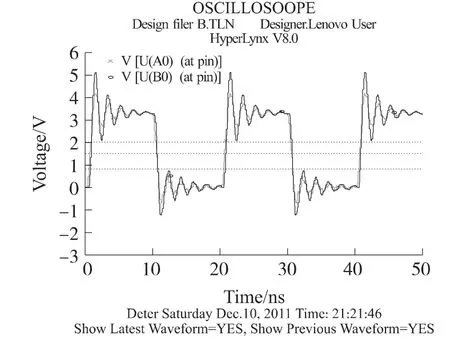

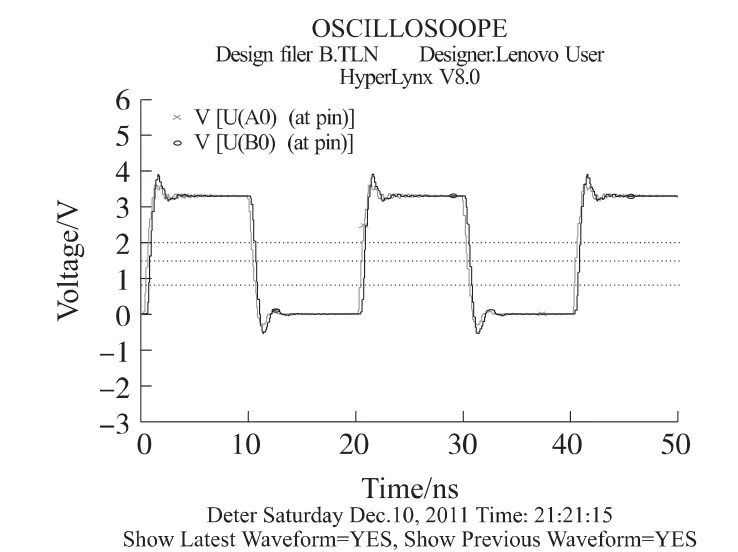

根据图5、图6、图7 得到仿真数据如表一所示。由仿真波形可以看出,实际串联端接后信号振铃现象明显减小。接收端和源端的过冲和下冲幅值在允许的范围之内,抑制信号反射的效果很好。

图5 未端接仿真波形图

图6 串联端接仿真波形图

图7 实际串联端接仿真波形

2.4 布线前串扰仿真

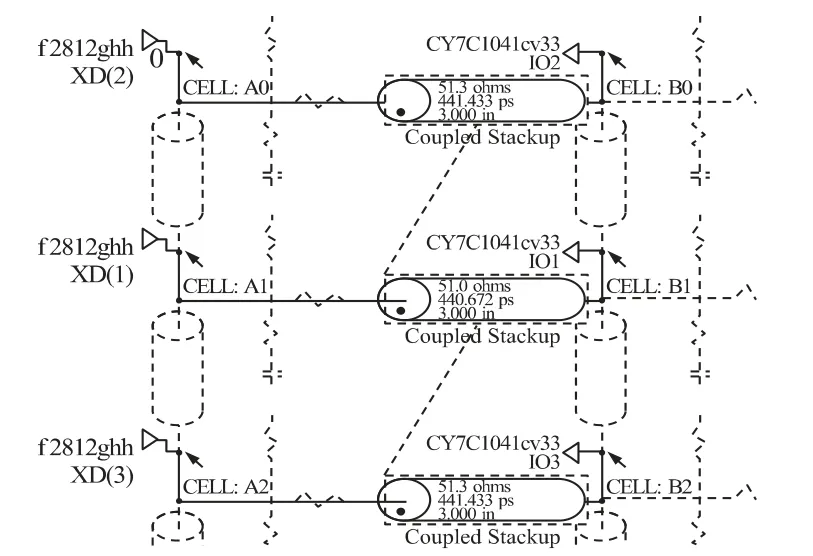

在布局布线时,由于DSP 与SRAM 之间的走线间距较近,走线密度较高,必然存在较大程度耦合。在此,以XD(2)为例,建立信号完整性原理图,设置3条走线同在第1 层,如图8 所示,XD(2)为受扰线,XD(1)和XD(3)为干扰线。仿真结果如图9所示。

图8 串扰仿真原理图

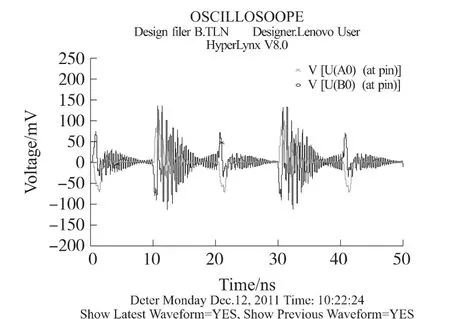

图9 串扰仿真结果

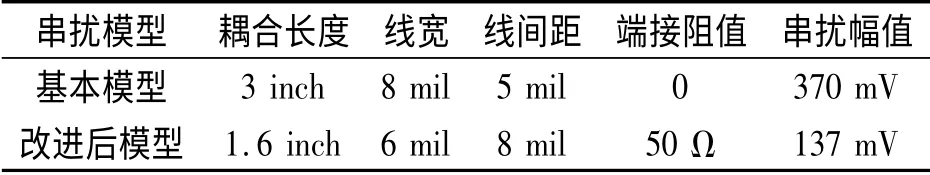

根据前面的分析,可以通过端接匹配电阻、减小耦合长度、拉大传输线间的间距、减小线宽来减小串扰的影响。图10 为进行改进后的串扰仿真图。根据图9、图10 可以得到仿真数据如表2 所示。

图10 改进后的串扰仿真结果

表2 串扰仿真数据

由表2 可知,改进后,串扰幅度最大为137 mV,满足了系统设计的要求。

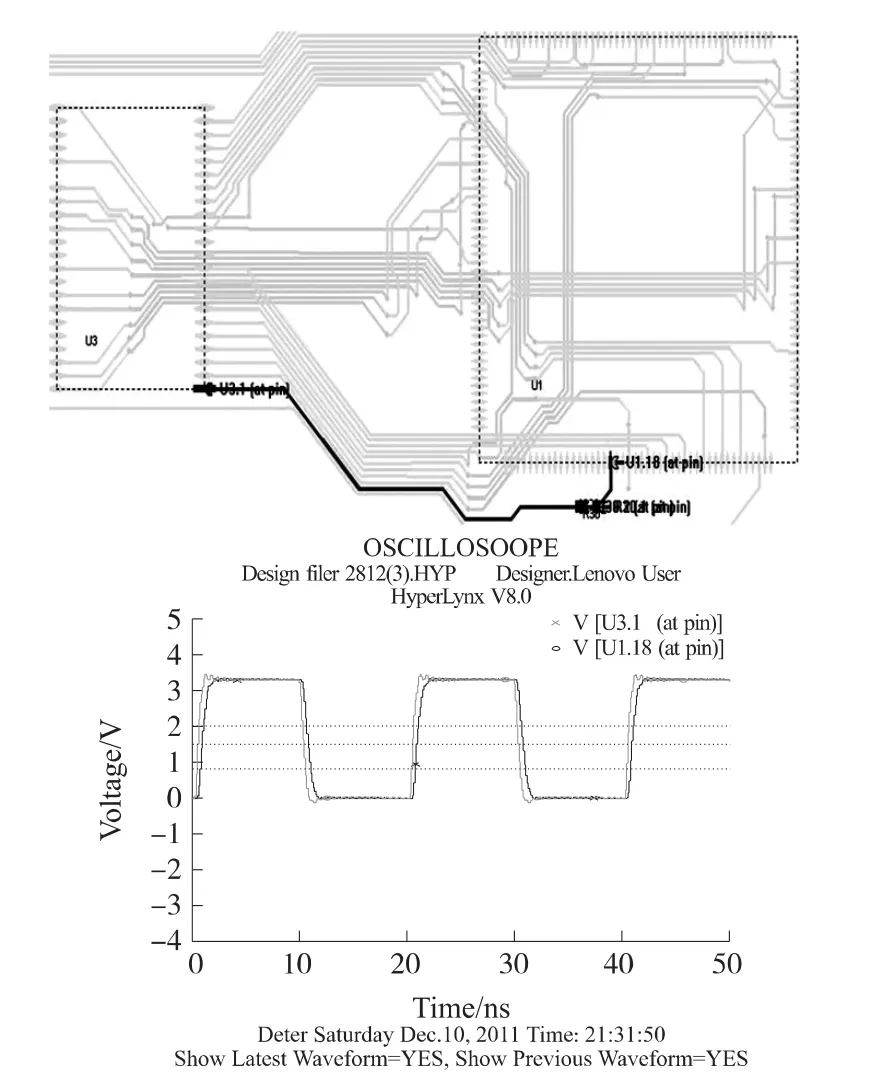

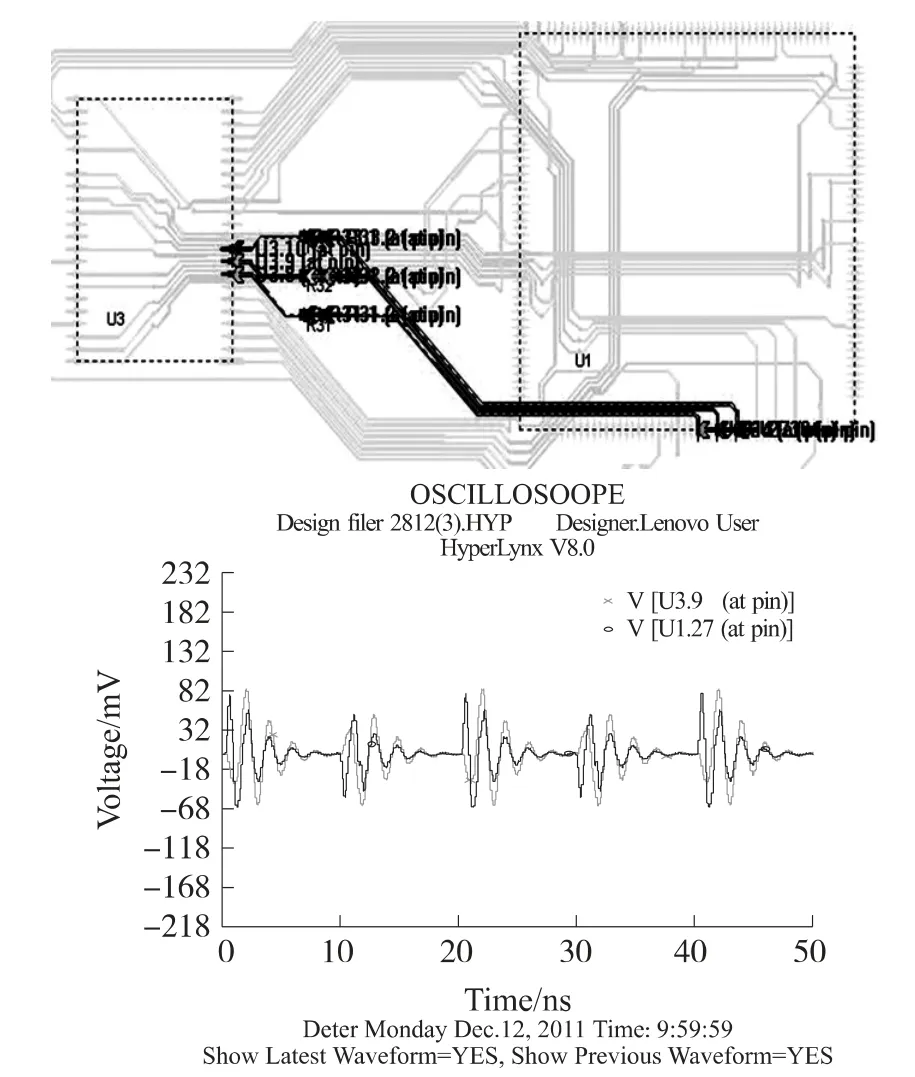

2.5 布线后仿真

PCB 板绘制完成后,元器件的布局布线基本确定。此时进行布线后仿真可以更加贴近实际情况[6],可以发现原有设计问题,以修正设计参数优化布局走线。在§3.3 和§3.4 已分别对相关信号进行了反射和串扰仿真,这里通过布线后仿真验证上述仿真结果。仿真结果如图11 和图12 所示。

图11 实际走线和端接反射仿真结果

图12 实际走线和串扰仿真结果

2.6 布线前和布线后仿真结果比较

图11 为反射仿真的实际走线和仿真结果。由图可知,驱动端输出信号的上冲电压为3.472 V,下冲电压为-129 mV。接受端输入信号的上冲电压为3.366 V,下冲电压为-24 mV。接收端和驱动端的信号波形上冲和下冲都小于200 mV,拥有良好的信号完整性,满足设计要求。图12 为串扰仿真的实际走线和仿真结果。由图可知,XD(2)处的波形抖动较小,串扰幅值最大值为85 mV,不会影响信号的完整性。前仿真与后仿真的结果比较如表3 所示。

表3 布线前后仿真数据比较

上述结果基本一致,满足系统信号完整性要求。

3 结束语

本文利用HyperLynx 软件和元器件IBIS 模型对变电站状态监测系统无线节点进行了信号完整性分析和研究。对其中关键信号线进行了详细的布线前和布线后仿真实验,通过一系列有效措施抑制了信号的反射和串扰影响。由于DSP 和SRAM 之间数据收发率较高,因此时序问题就显得十分重要。所以如何解决这一问题是下一步需要研究和改进的方面。

[1] 历科立,景占荣,严会会.基于HyperLynx 的FPGA 系统信号完整性仿真分析[J].现代电子技术,2011,34(8):146-146.

[2] 李成,程晓宇,毕笃彦,等.基于HyperLynx 的高速DSP 系统信号完整性仿真研究[J].电子器件,2009,(2):445-451.

[3] Eric Bogatin.李玉山,李丽萍,等译. 信号完整性分析[M]. 北京:电子工业出版社,2005.

[4] 曾爱凤,王海鹏.板级互连线的串扰规律研究与仿真[J].电子测量技术,2010,33(8):9-12.

[5] Howard Wjohnson & Martin Graham. High Speed Digital Design[M].Prentice Hall,1993:189-190.

[6] 李聪,张国贺,陈宝国,等.基于HyperLynx 的DSP 系统信号完整性仿真与改进[J].战术导弹技术,2011,(4):110-116.