一种抗相关功耗攻击DES算法及FPGA电路实现

2012-09-17单伟伟吕宇翔孙华芳

李 杰 单伟伟 吕宇翔 孙华芳

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

一种抗相关功耗攻击DES算法及FPGA电路实现

李 杰 单伟伟 吕宇翔 孙华芳

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

针对目前以差分功耗攻击为代表的旁路攻击技术对加密设备的安全性造成了严重威胁的状况,提出了一种基于“非对称”掩码的新型抗差分功耗攻击的方法,并在标准加密算法(DES)中实现.即通过在算法的不同时刻引入不同的随机掩码变换,使加密设备的功耗与密钥之间的相关性被扰乱,从而抵御相关功耗攻击.以此方案设计了电路并采用FPGA实现了电路.搭建了功耗攻击的FPGA实物平台,分别对未加防御的DES和抗相关功耗攻击DES算法电路进行相关功耗攻击实验.实验结果表明,以增大5倍攻击样本且花费了近5倍的破译时间为代价,仍无法攻破该方法保护的DES算法,可见“非对称”掩码方法对相关功耗攻击起到了防御效果.

差分功耗攻击;DES算法;掩码技术;抗功耗攻击;FPGA

信息的保密性是信息安全的一个重要方面,保密的目的是防止破译信息系统中的关键信息.近年来对信息系统最为引人瞩目的攻击形式是利用加密硬件执行某种操作时泄漏的旁路信息[1](如功耗、执行时间等)来推测真实密钥,如简单功耗分析(simple power analysis,SPA)和差分功耗分析(differential power analysis,DPA),由于其简便易行且不破坏加密系统,已成为信息安全的一大威胁.Kocher等[2]在1999年提出 DPA 技术,通过测量约1 000条芯加解密操作时的功耗曲线,就可以破译当时市场上大部分智能卡.基于相关系数的差分功耗攻击(correlation power analysis,CPA)[3]使攻击者更容易利用大样本统计方法获得密钥信息.

为抵御功耗攻击,多种抗功耗攻击的方法相继诞生,例如在算法流程中插入随机操作[4]、增加功耗噪声[5]和采用双轨电路设计的方法[6]等.除了以上几种方法外,内部数据处理流程中引入掩码[7-10]也是一种有效对抗功耗攻击的方法.在加密算法运算时,每一个中间值都与一个称为“掩码”的随机数进行变换,这使得功耗信息不仅与密钥操作有关,而且还与引入的随机数相关.随机数扰乱了功耗与密钥间的相关性,从而实现了抗功耗攻击.采用单一掩码的传统掩码技术仅能抵御基于简单分类的传统DPA攻击[10],难以有效地防御基于数学模型进行相关性计算的CPA攻击.

本文提出了一种用“非对称”掩码技术来抵御相关功耗攻击.该非对称掩码方案通过在DES算法的首轮和末轮内的不同时刻添加不同的掩码操作,从而有效地抵御相关功耗攻击.改进的抗攻击DES采用数字电路设计,并用FPGA实现,最后对其进行功耗攻击实验,以验证算法的抗攻击效果.

1 DES算法架构及相关功耗攻击原理

DES算法为对称密码体制,主要由置换和扩散构成,易于用硬件实现.由于其具有多次循环迭代的共性,在该算法的运算过程中功耗与所做的操作及操作数之间具有一定的联系,使其易受功耗攻击.DPA攻击通过将采集到的真实功耗信息与数学分析计算得到的假设功耗信息进行统计分析,从而获得两者的相关性,当且仅当猜测密钥与真实的密钥相同时,相关系数取得最大值.其中需要采用一定的功耗模型将无实际意义的数学分析映射为有物理意义的假设功耗值,通常功耗模型采用汉明距离模型,电路在某个特定时段用0→1转换和1→0转换的总数来表示电路的功率消耗.

CPA攻击的一般流程为:①选择DES执行过程的某个中间值,用来恢复密钥信息,这个中间值是一个函数f(d,k),其中,d为已知的明文或密文,k为密钥信息的一部分(称为子密钥);② 测量DES加密过程的实际功耗迹,若采集D次加密过程,每次加密采集P个功耗点,则获得一个D×P的功耗矩阵,记为矩阵T;③ 计算假设的中间值,假设子密钥k有K种可能,对于每一次加密计算出中间值,可获得一个D×K的矩阵V;④ 将中间值映射为假设功耗值,利用步骤①和③,并采用功耗模型(汉明距离或者汉明重量模型)计算得出一个D×K的假设功耗矩阵H;⑤计算假设功耗矩阵与实际功耗矩阵之间的相关性,得出一个P×K的矩阵Z,其每一行分别对应一种猜测的密钥,每一列对应在该时刻假设功耗与实际功耗之间的相关系数,计算式为

式中,hd,i为矩阵 H 的元素,i=1,2,…,K,d=1,2,…,D;td,j为矩阵 T 的元素,j=1,2,…,P.⑥ 利用矩阵Z按行绘制出曲线(密钥-相关性曲线),出现峰值的曲线即对应CPA攻击结果.

2 DES算法的抗CPA非对称掩码设计

2.1 传统掩码技术的DES分析

DES 算法的16 轮(i=1,2,…,16)加密操作相同,仅进入首轮操作前需进行的初始置换(initial permutation,IP)和第16轮输出端需进行的最终置换(finial permutation,FP)有所不同.每一轮内的操作包括E盒置换(e box permutation)、S盒置换(S-BOX)、P盒置换(P);轮间的加密子密钥为Ki;轮间数据被分为相同长度的Li和Ri两部分.

基本的基于掩码技术的DES算法抗DPA攻击方案[10]通过在DES算法进行初始置换时就与一个64 bit的随机数进行异或操作来引入掩码值,之后在加密的每一轮内添加相同的随机化掩码操作,从而使其整体功耗随机化,因此能防御经典DPA攻击.但是在进行更强大的基于相关系数的CPA攻击时,取IP置换后的值与首轮的输出值并利用汉明距离模型构造模拟功耗矩阵,可以推导出,二者的汉明距离与标准DES的汉明距离完全相同.因而采用汉明距离模型能有效屏蔽掩码的作用,使得该抗攻击方法无法抵御基于相关系数的CPA攻击.

2.2 非对称掩码DES方案设计

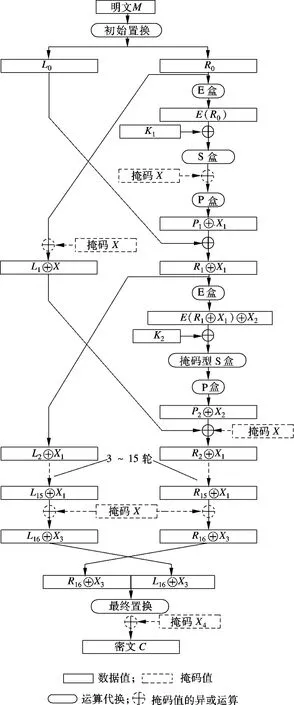

为克服上述方案中两轮之间使用同一个掩码带来的安全隐患,本文提出一种基于“非对称掩码”的抗攻击方案.其核心思想是对DES的首轮和末轮添加的掩码值及位置均异于其他轮,使得对其采用汉明距离模型时无法消去掩码的作用.本方案的具体流程如图1所示,其中,X为随机数,X1~X4均为由X计算得出的随机数,X1=P(X),X2=E(X1),X3=X1⊕X,X4=I([X3,X3]).其中,P()表示P盒置换;E()表示E盒置换;I()表示IP置换,[X3,X3]表示用2个X3首尾拼接成的变量,因而X,X1,X2,X3,X4为 32,32,48,32,64 bit.

图1 非对称掩码DES算法的流程图

非对称掩码DES算法在首个子密钥K1未对数据进行操作之前,算法流程保持和原始DES流程相同,在第1轮子密钥K1对明文进行异或后引入掩码X;随后的第2~15轮的加密过程,操作方式类似,仅异或的随机数值不同,旨在保持算法中间处理过程功能的正确性;最后在第16轮输出前异或上掩码X,经过IP逆置换(FP),并加上掩码X4还原真实的密文信息.

从该方法可以看出,仅在密钥信息引入后,才对寄存器迭加上掩码,此后随机数直接影响寄存器的翻转,从而改变算法产生的实际功耗.若对该算法同样采用CPA攻击方法,仍选取IP置换后的值与首轮的输出值为攻击点.以第1轮为例,该方案中IP置换后的值与首轮的输出值之间的汉明距离为

式中,R0为明文M进行初始置换后数据的第32~63 bit部分;R1为第1轮输出数据的第32~63 bit部分,可见本方案的汉明距离因为与随机数X1做异或运算而变成随机数.而对应于原始DES,汉明距离仍为

随机数的影响被消除.可以看出,由于引入了随机数X1,使得该方案的汉明距离与标准DES的汉明距离不同.即攻击者利用汉明距离模型已无法表征出实际的功耗消耗.因此对CPA攻击来说,即使猜测密钥正确,相关系数也无法取得最大值.

2.3 非对称掩码DES的电路设计

DES算法包括16轮的迭代运算,其中,除了首轮和末轮,各个中间轮操作流程完全相同.因此,16轮操作可以通过结合部分控制逻辑在不同时刻使用同一套硬件结构实现,即一个周期完成一轮的加密运算.故完成一次完整的加密运算需要16个周期.子密钥生成方法与标准DES算法相同,仅需移位运算和置换运算即可实现.此外,该算法除了掩码型S盒,剩余置换运算均与DES标准相同.下面对涉及掩码操作的电路单元作进行说明.

1)随机数产生电路 本文设计中所使用的随机数是由硬件描述的伪随机数发生器(RNG)产生的,实现方法为线性反馈移位寄存器.

2)轮间的Mask电路 由于在每一轮迭代中,每个64位的中间结果被分为左右2部分,而且左右2部分作为相互独立的32位数据进行处理.

① 第1轮.左半部分异或上随机掩码X.右半部分在S盒的输出端异或上随机掩码X,并经P盒置换后获得.由于在该轮S盒未经修改,P盒置换是线性运算,因此该轮右半部分的输出结果异或上掩码X1.

②第2~15轮迭代运算.左半部分均为上一轮右半部分的输出,即左半部分异或上随机掩码X1.右半部分经E盒扩展以及掩码后的S盒、P盒置换后,输出结果保持异或上掩码X1.这样使得算法流程保持高度的对称性,也保证算法的功能正确.

③第16轮.左半部分异或上随机掩码X;右半部分的运算与第15轮操作类似,唯一不同的仅在P盒输出端异或上掩码X.故使得左右2部分的输出端分别异或上掩码X4.

3)掩码型S盒电路设计 S-BOX替换是轮内运算的核心,且是非线性的,为了适应Mask算法需要进行修正.在本文设计的第2~16轮操作中,采用修正过的 SM-BOX[9],如

式中,P-1为P盒的逆置换运算.采用查找表实现S-BOX与SM-BOX的操作.

4)最终置换 由于初始置换IP与最终置换FP为互逆的线性运算,因此,在该方案中构造掩码X4进行操作,以在算法进行最终置换并保证算法安全性的前提下,去掉掩码还原出正确的密文信息.

加密电路的信号接口如图2所示,图中,含时钟端(clk)、复位端(reset-n)、加载掩码信号(ld)、加载明文信号(load-i)、加/解密信号(encrypt-i)、明文(data-i)、密钥(key-i)、密文(data-o)以及加密完成信号(ready-o).encrypt-i控制电路工作在加密状态或者解密状态;load-i出现高电平时表示加密开始;ld为高电平时表示加载掩码,电路具有抗相关功耗攻击能力;当ready-o出现高电平脉冲时则表明加密完成,密文由data-o输出.

图2 加密电路接口信号图

2.4 非对称掩码DES功能仿真

将上述模块用Verilog语言设计,每个周期实现一轮的加密操作.并将该设计在ModelSim的平台下进行测试,利用FIPS-81标准给出的测试矢量作为明文输入,得出的加解密结果正确.例如输入为h’68652074696d6520,密钥取为 h’0123456789abcdef,分别在模块的输入端加入激励,得到的波形如图3所示.从波形中可以看出,时钟周期为100 ns,一次加密过程需要16个周期完成.输出信号有效时,加密结果为h’6a271787ab8883f9,与测试向量给出的结果相同,并且在一次加密过程中,掩码值X,X1,X2,X3,X4均保持恒定,而在不同次的加密中随机数不同.同样地,在FPGA平台下,也进行了多组矢量的测试,结果正确.因此,利用本文设计的非对称掩码方案实现的DES算法在功能上可以完全实现标准的DES算法的加解密功能.

图3 非对称掩码DES仿真波形

3 抗功耗攻击实验及结果

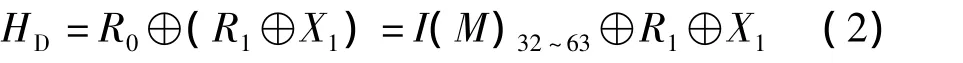

本文搭建的功耗攻击平台实物图如图4所示,该平台主要由示波器、PC机、差分探头、电源、子板和母板构成.示波器接在串联于母板与电源之间的电阻两端的差分探头上,实时地记录母板运行加密运算时产生的电流.将电流值换算成相应的功耗值后,通过网线将功耗数据传输至PC机.PC机除了接收和处理功耗数据外,还要向母板发送激励.其中,FPGA作为母板,分别烧录了原始DES算法和本文改进的DES算法的镜像文件.此外,利用集成了UART接口的一个微处理器作为子板,为母板和PC机提供了接口,方便PC与FPGA间激励矢量的传输.

图4 FPGA功耗攻击平台

选取攻击DES算法的第1轮,并以6位子密钥为一组进行破解.按照CPA攻击流程,利用式(1)计算出相关系数,从而通过寻找相关系数的峰值来猜测正确的密钥值.先对原始的DES算法进行CPA攻击,输入20 000组明文,固定一组密钥,示波器的采样频率为1 GHz.在一次加密过程中示波器采样8 500个功耗点,因此生成20 000×8 500的功耗矩阵T.以6位子密钥为一组,逐组攻击.以猜测首六位密钥为例,猜测的子密钥有26=64种可能,因此测量得到的功耗矩阵H为20 000×64.

将2个矩阵的功耗数据导入Matlab程序后,计算出相关系数并绘制出曲线.截取前4个周期的相关系数轨迹(见图5(a)).由图可见,当猜测密钥为43(即正确的子密钥101011)时,相关系数在第1 000个功耗点处(约第1轮加密结束时刻)出现明显峰值,即首6位子密钥攻击成功.运用同样的方法攻击剩余的42位密钥,即对剩余的7个S盒进行CPA攻击,发现当猜测子密钥与真实子密钥相同时,相关系数仍出现峰值,因此可从相关系数中猜测出真实的密钥值,故CPA攻击成功.

图5 CPA攻击实验结果

用同样的方法在FPGA功耗攻击环境下,对本文提出的非对称掩码DES算法进行功耗攻击.攻击样本增加到1×105个,相关系数轨迹如图5(b)所示.可以看出,当猜测密钥为43时,其绘制的相关系数湮没于其他功耗迹中.然后运用同样的方法攻击剩余的42位密钥,即对剩余的7个S盒进行CPA攻击,发现当猜测子密钥与真实子密钥相同时,正确密钥产生的相关系数轨迹仍无出现明显峰值,故无法从功耗迹中推测出正确的密钥.

对上述不同DES核的功耗攻击实验结果进行统计可以看出,由于引入了非对称掩码随机数,使得该方案的汉明距离被随机数改变,即攻击者利用汉明距离模型已无法表征出实际的功耗消耗.因此对CPA攻击来说,即使猜测密钥正确,相关系数也无法取得最大值,即使以增加5倍的攻击样本为代价,非对称掩码DES核的密钥仍无法由相关系数获得.而且相比处理2个2×104行的功耗矩阵运算,处理2个10×105行的矩阵运算花费的时间显著增加.实验结果表明,本文设计的非对称掩码DES核具有良好的抗CPA攻击效果.

4 结语

本文提出了一种基于非对称掩码的抗功耗攻击方法,并在DES算法上应用.经电路设计和FPGA实现,在硬件抗攻击平台上进行了实验.可以看出,对其进行CPA攻击时,以消耗至少5倍多的样本和计算时间为代价,仍然无法获取密钥.可见本文设计的非对称掩码DES方案可以有效抵御CPA攻击.

[1] Kelsey J,Schneier B,Wagner D,et al.Side channel cryptanalysis of product ciphers[J].Journal of Computer Security,2000,8(2/3):141-158.

[2] Kocher Paul,Jaffe Joshua,Jun Benjamin.Differential power analysis[C]//19th Annual International Cryptology Conference.California,USA,1999:388-397.

[3] Mangard Stefan,Oswald Elisabeth,Popp Thomas.Poweranalysisattacks[M]. Berlin, Germany:Springer Science,2007:178-183.

[4] Zafar Y,Park J,Har D,et al.Random clocking induced DPA attack immunity in FPGA[C]//IEEE InternationalConferenceonIndustrialTechnology.Gwangju Korea,2010:1068-1070.

[5] Kamoun N,Bossuet L,Ghazel A.Correlated power noise generator as a low cost dpa countermeasures to secure hardware AES cipher[C]//3rd InternationalConference on Signals Circuits and Systems.Tunis,Tunisia,2009:1-6.

[6] Guiley S,Sauvage L,Hoogvorst P,et al.Security evaluation ofWDDL and SecLib countermeasures against power attacks[J].IEEE Transactions on Computers,2008,57(11):1482-1497.

[7] Akkar M L,Goubin L.A generic protection against high-order differential power analysis[C]//10th InternationalWorkshoponFastSoftwareEncryption.Lund,Sweden,2003:192-205.

[8] Trichina E,Korkishko L.Secure and efficient AES software implementation for smart cards[C]//5th International Workshop on Information Security Applications.Jeju,Korea,2004:425-439.

[9] Yoshikawa M,Kojima Y.Efficient random number for the masking method against DPA attacks[C]//21st International Conference on Systems Engineering.Las Vegas,NV,USA,2011:321-324.

[10] Akkar M L,Giraud C.An implementation of DES and AES,secure against some attacks[C]//Third International Workshop on Cryptographic Hardware and Embedded Systems(CHES).Paris,France,2001:309-318.

A correlation power analysis resistant DES algorithm and its circuit implementation on FPGA

Li Jie Shan Weiwei Lü Yuxiang Sun Huafang

(National ASIC System Engineering Research Center,Southeast University,Nanjing 210096,China)

With the threat of differential power analysis(DPA,a type of side channel attack)to encryption devices,a new DPA countermeasure method is proposed and implemented on data encryption standard(DES)algorithm,using“asymmetric”mask technique which introduces asymmetrical random transformation to eliminate the relevance between power consumption and the key in order to resist DPA attack.Its hardware implementation was designed and realized on FPGA(field-programmable gate array).Then,a real power analysis attack FPGA platform is built to test the proposed DES as well as the unprotected DES respectively.The experiment results show that even when the power samples and analyzing time are nearly 5 times larger than the unprotected DES,our improved DES still cannot be attacked to gain the right key by Correlation Power Analysis.Therefore,the“asymmetric”mask technique is effective in resisting correlation power analysis.

differential power analysis;data encryption standard algorithm;mask technology;power analysis attack resistance;FPGA(field-programmable gate array)

TN47

A

1001-0505(2012)06-1063-06

10.3969/j.issn.1001 -0505.2012.06.008

2012-06-06.

李杰(1969—),男,博士,研究员;单伟伟(联系人),女,博士,副教授,wwshan@seu.edu.cn.

国家自然科学基金资助项目(61006029)、江苏省基础研究计划资助项目(BK2010165,BK2010167).

李杰,单伟伟,吕宇翔,等.一种抗相关功耗攻击DES算法及FPGA电路实现[J].东南大学学报:自然科学版,2012,42(6):1063-1068.[doi:10.3969/j.issn.1001 -0505.2012.06.008]