一种数字控制可变输出DC-DC转换器的设计

2012-09-17王绍权黄秋华陈秀玲孙伟锋时龙兴

王 青 王绍权 黄秋华 陈秀玲 徐 申 孙伟锋 时龙兴

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

一种数字控制可变输出DC-DC转换器的设计

王 青 王绍权 黄秋华 陈秀玲 徐 申 孙伟锋 时龙兴

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

针对SoC中的动态电压调节技术,设计了一款可变输出的数字控制Buck型DC-DC变换器.首先,采用基于系统模型的轨迹预测方法,根据当前开关周期电感电流和输出电压的采样值,并基于电感、电容的储能特性,预测出下一开关周期的电感电流和输出电压值;然后,将此预测值代替实际采样值,补偿环路时延,提高瞬态响应.此外,采用多采样技术减弱随机噪声的影响.本设计采用SMIC 65 nm工艺实现.测试结果表明,当仿真预测值与实际采样值之间的最大偏差小于15 mV时,输出电压的稳态误差可控制在5 mV内.负载和参考电压变化时,输出电压的瞬态响应时间分别为122.3和476.1 μs,电源调整率为14.37%.

DC-DC转换器;数字控制;预测算法;多采样;可变输出

在电子产品领域中,便携式产品发展迅速,随着其处理能力的提高,新功能不断涌现,随之造成的缺点是系统面积增大、功耗增加.提高系统集成度、降低系统功耗成为设计中重点关注的问题.电源芯片作为便携式产品的主要组成部分,同样面临这方面的挑战[1].

在电源管理芯片的效率几乎被开发至极限的情况下,提高效率的设计重点已经从电源转换环节过渡到负载环节.目前市场上出售的供移动设备使用的SoC均具备了动态电压调制(DVS)的降耗技术,作为配套的电源转换器也被要求能够在多个输出电压值之间快速切换.将电源芯片与一些常规功能器件(如充电器、比较器等)集成在同一颗芯片内,已成为便携式电源芯片发展的一个方向,一些深入定制的客户化电源芯片可以与主机系统实现片上集成.随着工艺尺寸的缩小,数字电源在集成度方面的优势显著,在纳米尺度下设计障碍更小、工艺移植性更好,因而成为电源发展的新方向[1-2].

本文针对带有DVS功能的SoC系统中的电源转换器,设计了一款可变输出的数字控制Buck型DC-DC变换器,为了抑制数字调制过程中固有时滞对瞬态响应的影响,提出了基于拓扑电路结构的预测方法.同时,为了避免常规采样控制策略不能有效获得随机扰动信息的局限,采用多采样技术针对扰动进行相应的调整,加快调制速度.

1 可变输出数控转换器的工作原理

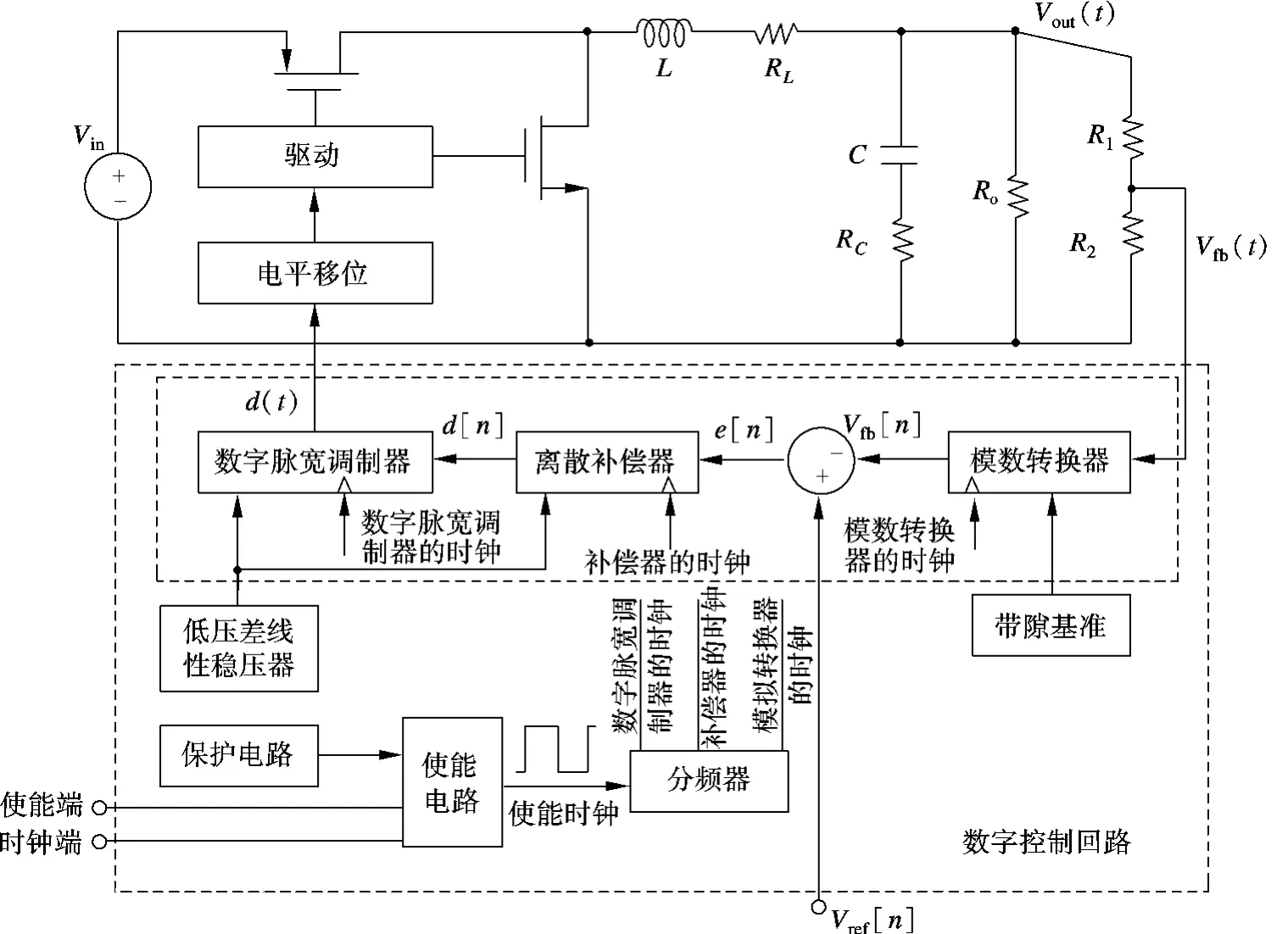

图1为本设计中数字控制Buck型DC-DC转换器的结构框图.采用全集成设计方案,控制器的主体由模数转换器(ADC)、离散补偿器和数字脉宽调制器(DPWM)3个部分组成[3-4].输出电压Vout(t)经电阻分压后的值Vfb(t)被ADC采样,并转换成数字离散信号Vfb[n].将该离散信号与预设的参考信号Vref[n]进行比较,得到的误差信号e[n]作为补偿器的输入.补偿器输出占空比控制命令d[n]以控制DPWM 电路产生所需要的一系列占空比值d(t).本设计中模拟部分和数字部分分别使用了不同的电压域,因此采用内嵌低压差线性稳压器,将模拟电压域转换为数字电压域,并用电平移位电路作为模数电路信号交界面的接口电路.

电源转换器的输出电压为0.6~1.5 V,调节步长为25 mV,因此ADC需要具有较大的线性量化范围及较高的转换精度.本文设计了功耗较低的逐次逼近型6 bit ADC.为避免数字电源中由于ADC和DPWM量化不匹配造成的极限环振荡[5-6],设计中DPWM 的分辨率大于ADC的分辨率,并选择了 9 bit振荡环结构[7].

图1 数字控制Buck型DC-DC转换器的结构框图

2 快速响应的数据控制策略

数字电源系统属于纯滞后系统,反馈环路中采样量化、数据处理等步骤会造成不可忽略的时间延迟,尤其是在高开关频率的系统中,该时延对系统瞬态性能的影响更加明显.具有输出电压实时可调功能的电源要求根据处理器发出的控制命令在最小的延时时间内调节输出电压至新的值.环路时延是数字控制系统中的固有缺陷,制约着开关变换器的瞬态响应.因此,环路时延的研究对于数字控制技术在高性能 DC-DC变换器的应用有重要影响[8-10].

改善DC-DC转换器瞬态响应的最简单的方法是改变功率级电路的参数(如开关频率或输出滤波器的参数).但是这种方法不仅会带来器件成本的增加,还会导致效率的降低[11].因此,控制器瞬态响应速度的优劣是设计的关键所在.在数字控制开关电源中,可以借助数字电路强大的计算能力,利用非线性控制方法,对响应时间进行优化,从而实现接近最优的瞬态响应[12-13].

2.1 预测算法

根据电源系统当前的状态及系统需要达到的状态,利用电感、电容储能元件的特性,可以提前计算出后面几个周期所需控制量的值,达到补偿环路时延的目的.以图1所示的同步整流Buck型DC-DC转换器拓扑结构为例,电路工作在连续电流模式下,假设各元件均为理想元件,则电感电流的关系为

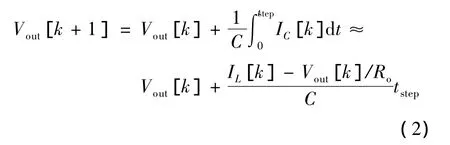

式中,L为输出滤波器中的电感;IL为流过电感的电流;VL为电感两端的电压;Ts为开关周期;D为本周期内的占空比.

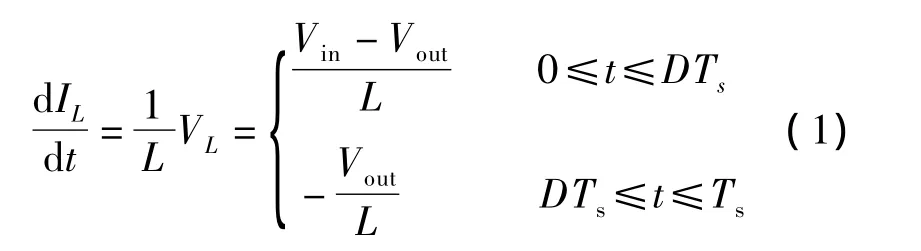

由式(1)可知,如果已知一个周期开始时刻的IL,Vout以及该周期的开关管占空比D,通过设定合适的插值点个数N,即可对系统运行变化做出准确的拟合,预测出下一周期开始时刻的对应值.

输出电压的变化主要是受输出端电容的充放电直接影响的.设每周期开始时刻采样的电感电流和输出电压值分别为IL[k]和Vout[k],则下一个插值点的输出电压Vout[k+1]可表示为

式中,C为输出滤波器中的电容;IC为流过电容的电流;tstep=Ts/N.此时,电感电流IL[k+1]可由式(1)计算得到,即

按上述步骤,重复计算N+1次后即可预测得到下一个开关周期的电感电流和负载电压,完成预测工作.在控制策略模块中,利用预测值代替实际采样值,从而克服环路时延.为了避免预测误差累积,每个开关周期起始时均采用新采样值对预测值进行修正,以降低系统的发散速率.

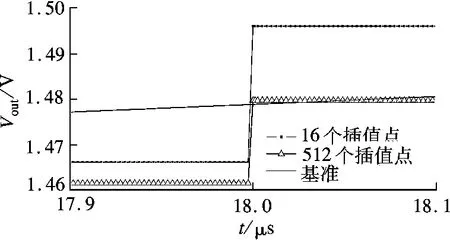

应用Matlab软件对本设计进行验证,设置2种不同的插值点个数(512和16)进行仿真,输出电压的局部放大波形如图2所示.图中,基准线表示实际输出电压的波形曲线.由图可知,2种插值点算法得到的预测值与实际电压的偏差小于15 mV,插值点个数越多,预测结果越接近实际情况.本设计中设定了16个插值点,实验结果表明,系统性能良好,且计算量仅为设定512个插值点时的1/32.需要注意的是,本设计是利用电感和电容的储能特性进行预测的,对功率级参数的准确度比较敏感.加入预测算法会增加系统的动态功耗,功耗值与插值点个数成正比.

图2 输出电压与多种预测方法的比较

2.2 多采样技术

常见的数字电源控制中,在每个开关周期内执行一次采样操作[2-3,6].然而,扰动随机出现后,若本次采样不能获得扰动信息,则要到下一个周期采样时才能被检测到.设扰动从出现至被检测到的最大延时为Ts,此时实际系统状态变量已经发生了改变.所采样的信号中如果存在噪声尖峰,则会降低量化器的有效分辨位数.因此,为了减弱环路时延对瞬态响应的影响,在设计时除了严格控制信号时序之外,还可以利用多采样技术[14],在一个开关周期中等时间间隔采样K次,将扰动的最大延时缩短为Ts/K.用多次采样的平均值代替瞬时值,消除噪声毛刺的影响.多采样技术已广泛应用于在逆变器等领域中[15].

本设计中,对4次ADC处理值取平均值,并将其送入PID补偿器,PWM在下个开关周期得到实现.控制回路从最后一次ADC采样到PWM信号输出延迟了0.75DTs,此时延作为纯相位滞后进行补偿.

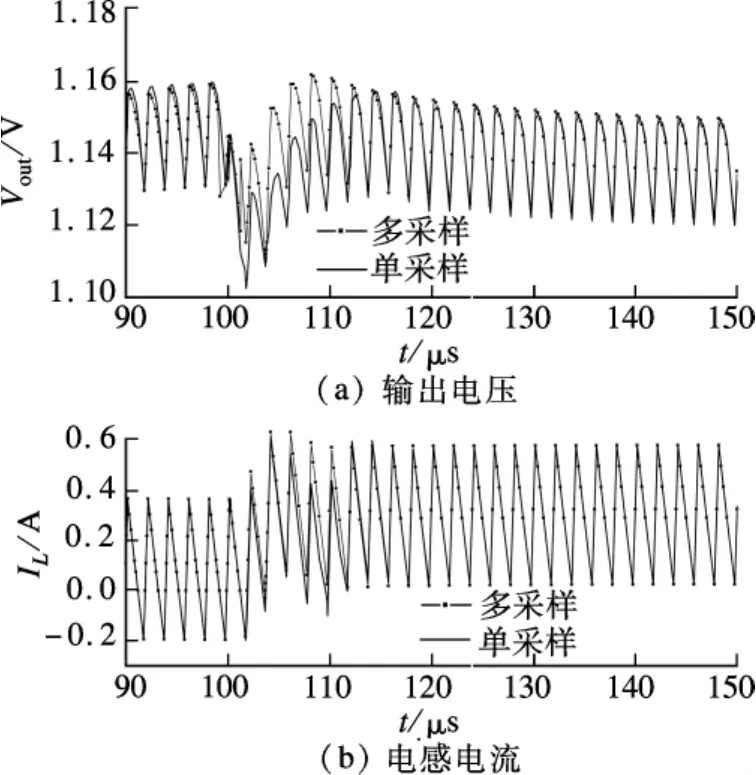

利用Matlab软件仿真得到负载发生变化时输出电压响应变化的局部放大波形图(见图3).由图可知,当负载电流由0.1 A突变至0.3 A时,单采样系统的输出电压经过约10 μs重新达到平衡值,而多采样系统经过约7 μs即可恢复平衡,并且其过充电压较单采样系统减小约10 mV.

图3 2种采样处理系统输出的比较

3 实验结果与讨论

本文设计了一种具有可调输出的数字控制DC-DC转换器.采用SMIC 65 nm CMOS工艺进行验证,符合SoC的主流工艺,便于实现片上集成.设计指标如下:输入电压为2.2~2.7 V,输出电压为0.75~2.15 V,每次最小调整步长约为22 mV,最大负载电流为100 mA,开关频率为1.5 MHz,输出滤波器中的电感值为22 μH,电容值为2.2 μF.芯片核心电路面积约为0.063 56 mm2(见图4).由于实际芯片含有多层冗余金属,电路显微照片模糊,因此采用版图示意.

图4 芯片布局图(版图)

设定Vin=2.5 V,Vout=1 V,Iout=50 mA,系统软启动时输出电压和电感电流的响应曲线见图5.由图可知,输出电压稳定时间约为1.02 ms,浪涌电流最大值为92.7 mA,输出电压的稳定值约为1.004 2 V,纹波约为24 mV,存在5 mV左右的稳态偏差.

图5 系统软启动时Vout和IL的波形形

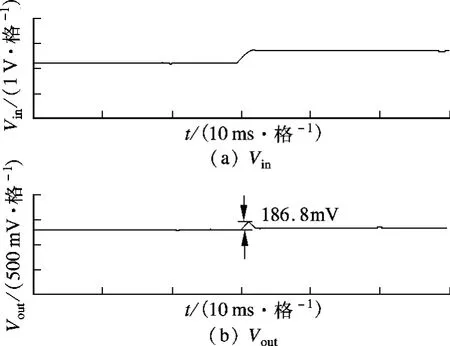

图6 输入电压变化时的输出响应波形图

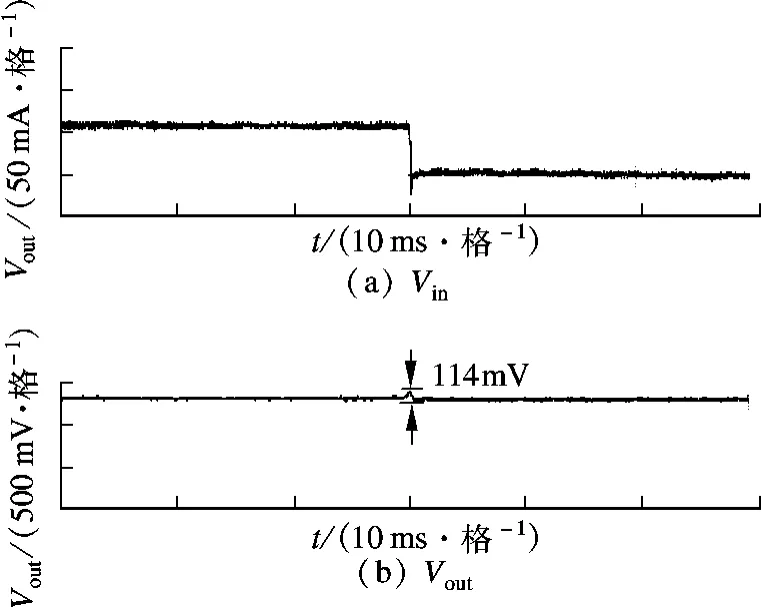

图7 负载电流变化时的输出响应波形图

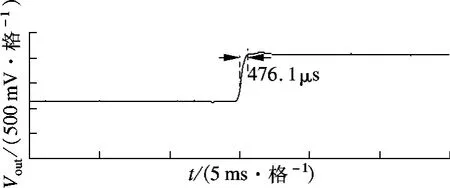

图8 基准电压变化时的输出响应波形图

图6~图8分别为输入电压、负载电流和参考基准电压发生变化时的输出电压响应波形.由图可知,当输入电压从2.2 V变为2.7 V时,输出电压最大过冲为186.8 mV,恢复时间为1.103 ms,电源调整率约为14.37%.当负载电流由55 mA变为0 mA时,输出电压存在约114 mV的过冲,恢复时间为122.3 μs.当参考基准电压由2.12 V变为1.15 V时,对应的输出电压稳态值分别为2.124 0和1.151 1 V,调整时间为476.1 μs.

4 结语

本文针对SoC中DVS技术的需求,设计了一种数字控制可变输出的Buck型DC-DC转换器,并且为了便于与SoC系统片上集成,采用了深亚微米工艺.为了提高瞬态响应速度,削弱数字电路固有的时延影响,采用了一种基于拓扑电路结构的预测补偿方法,通过对输出电压和电感电流的轨迹进行预判,提前给出下一步的控制变量,达到补偿环路时延的目的.测试结果表明,所设计的数字控制开关电源在输入电压、负载电流变化时均具有良好的抗扰能力,在输出电压调整参考值变化时也能够很好地跟随调整.然而,该算法的微调能力欠佳,输出电压具有稳态误差,因此下一步的研究重点是提高补偿算法的微调能力.

[1]钟建鹏.便携式产品面临的 PMIC设计挑战[EB/OL].(2011-06-01)[2012-01-15].http://www.eetchina.com/ART-8800 643569-628868-TA-5c9ddb4e.HTM.

[2] Manh V V.An integrated high efficiency DC-DC converter in 65nm CMOS[D].Linköping,Östergötland,Sweden:DepartmentofElectricalEngineering of Linköpings University,2010.

[3] ProdiA.Digital control of switching converters design and VLSI/DSP implementation[D].Boulder,Colorado,USA:Department of Engineering,Electronics and Electrical of University of Colorado at Boulder,2003.

[4]Prodic A,Maksimovic D,Erickson R W.Design and implementation of a digital PWM controller for a highfrequency switching DC-DC power converter[C]//Proceedings of the27th Annual Conference of2001IEEE IndustrialElectronicsSociety. Denver, Colorado,USA,2001:893-898.

[5] Lorch J R.Operating systems techniques for reducing processor energy consumption[D].Berkeley,California,USA:Department of Engineering,Electronics and Electrical of University of California at Berkeley,2001.

[6] Al-Hoor W,Abu-Qahouq J,Huang L,et al.Design considerations and dynamic technique for digitally controlled variable frequency DC-DC converter[C]//Proceedings of the38th Annual Power Electronics Specialists Conference.Orlando,Florida,USA,2007:846-850.

[7] Gao Y X,Zhang S F,Xu Y P,et al.Analysis and comparison of three implementation methodologies for high-resolution DPWM[C]//Proceedings of the3rd International Conference on Power Electronics Systems and Applications.Hong Kong,China,2009:1-7.

[8] Bibian S,Jin H.Time delay compensation of digital control for switch mode DC power supplies using prediction techniques[J].IEEE Transactions on Power Electronics,2000,15(5):835-842.

[9] Feng G,Meyer E,Liu Y F.A new digital control algorithm to achieve optimal dynamic performance in DCDC converters[J].IEEE Transactions on Power Electronics,2007,22(4):1489-1498.

[10] Corradini L,Costabeber A,Mattavelli P,et al.Parameter-independent time-optimal digital control for point-of-load converters[J].IEEE Transactions on Power Electronics,2009,24(10):2235-2248.

[11] Meyer E,Zhang Z L,Liu Y F.An optimal control method for Buck converters using a practical capacitor charge balance technique[J].IEEE Transactions on Power Electronics,2008,23(4):1802-1812.

[12]Corradini L,Costabeber A,Mattavelli P,et al.Time optimal,parameters-insensitive digital controller for VRM applications with adaptive voltage positioning[C]//Proceedings of the11th IEEE Workshop on Control and Modeling for Power Electronics.Zurich,Switzerland,2008:1-8.

[13] Yousefzadeh V,Babazadeh A,Ramachandran B,et al.Proximate time-optimal digital control for DC-DC converters[C]//Proceedings of the38th Annual Power Electronics Specialists Conference.Orlando,Florida,USA,2007:124-130.

[14] Corradini L,Mattavelli P,Tedeschi E,et al.Highbandwidth multisampled digitally controlled DC-DC converters using ripple compensation[J].IEEE Transactions on Industrial Electronics,2008,55(4):1501-1508.

[15] Waler G R.Digitally-implemented nature any sampled PWM suitable for multilevel converter control[J].IEEE Transactions on Power Electronics,2003,18(6):1322-1329.

Design of digital controlled DC-DC converter with variable output voltage

Wang QingWang Shaoquan Huang Qiuhua Chen XiulingXu Shen Sun WeifengShi Longxing

(National ASIC System Engineering Research Center,Southeast University,Nanjing 210096,China)

Aiming for the dynamic voltage scaling technology in SoC(system on chip),a digital controlled DC-DC Buck converter with variable output voltage is designed.First,a trajectory prediction method based on system model is used.Based on the sampling values of the inductor current and the output voltage at the current switching cycle,the inductor current and the output voltage at the next switching cycle are predicted according to the characteristics of energy storage devices such as inductor and capacitor.Then,these predictive values are used to substitute the actual sample values,which can compensate the loop time delays and improve the transient responses.Besides,the multiple-sample technology is adopted to minimize the effect of random noise.The circuit is designed on the SMIC 65 nm process.The experimental results show that when the maximum deviation between the prediction values and the actual ones is less than 15 mV,the steady-state error of the output voltage can be controlled within 5 mV.When the load current and the reference voltage change,the transient response time of the output voltage are 122.3 and 476.1 μs,respectively.The line regulation is 14.37%.

DC-DC converter;digital control;prediction algorithm;multi-sampling;variable output

TN4

A

1001-0505(2012)06-1058-05

10.3969/j.issn.1001-0505.2012.06.007

2012-04-10.

王青(1981—),女,博士生;时龙兴(联系人),男,博士,教授,博士生导师,lxshi@seu.edu.cn.

江苏省自然科学基金资助项目(BK2010167)、江苏省“青蓝工程”资助项目.

王青,王绍权,黄秋华,等.一种数字控制可变输出DC-DC转换器的设计[J].东南大学学报:自然科学版,2012,42(6):1058-1062.[doi:10.3969/j.issn.1001 -0505.2012.06.007]