一种低相位噪声LC压控振荡器的设计与实现

2012-09-17常昌远王绍权余东升

常昌远 王绍权 陈 瑶 余东升

(东南大学集成电路学院,南京 210096)

一种低相位噪声LC压控振荡器的设计与实现

常昌远 王绍权 陈 瑶 余东升

(东南大学集成电路学院,南京 210096)

基于TSMC 0.35 μm CMOS工艺,设计并实现了一种用于锁相环(PLL)频率合成器中的低相位噪声LC压控振荡器.这种压控振荡器采用互补交叉耦合差分结构,利用开关电容阵列技术增大频率调谐范围,并结合大滤波电容、二次谐波谐振滤波网络、开关电容阵列和偏置滤波网络来降低相位噪声.采用TSMC 0.35 μm CMOS工艺完成前仿真、版图设计与后仿真,芯片面积为1 285.3 μm ×1 162.7 μm.流片测试结果显示,LC 压控振荡器的频率调谐范围为 1.558 ~2.065 GHz,调谐范围高达28%,中心频率处的相位噪声为-133.3 dBc/Hz@1 MHz,综合性能指数为-183.3 dBc/Hz.由此表明,所设计的压控振荡器具有比较优异的综合性能.

LC压控振荡器;相位噪声;开关电容阵列;CMOS

无线通信系统的迅猛发展促进了低成本、高集成度无线收发机的研究与开发.同时,现代集成电路制造工艺的不断进步,使得无线收发机系统中大部分单元电路能够集成到单片收发机芯片上.作为压控振荡器(voltage controlled oscillator,VCO)重要的性能指标,相位噪声会对收发机接受信号产生严重干扰[1].利用CMOS工艺将LC压控振荡器集成到频率合成器中,可降低生产成本,但CMOS器件中较高的1/f噪声导致相位噪声明显增加[2].近年来,通过采取合理的降噪措施,利用CMOS实现的LC压控振荡器的相位噪声性能已经能够满足大多数应用场合.Fang等[3]综合运用大滤波电容、开关电容和偏置滤波技术设计了一款应用于WSN中的压控振荡器.Jongsik等[4]采用大电容滤波和谐振滤波网络技术设计了一款线性度良好、具有宽调谐范围的LC压控振荡器.Wang等[5]利用谐波滤波电阻来降低相位噪声.Mohamed等[6]采取电流复用技术使有效相位噪声达到-133.3 dBc/Hz@1 MHz.

为了获得更好的综合性能,本文采用TSMC 0.35 μm CMOS工艺设计了一款中心频率为1.81 GHz的LC压控振荡器.基于降低相位噪声的设计原理和方法,给出了具体的电路设计、版图设计与后仿真.流片测试结果表明,所设计的压控振荡器整体性能优良.

1 降低相位噪声的设计考虑

实际上,VCO中的有源器件与无源器件都会产生噪声.噪声对振荡器的影响表现为输出信号幅度和频率的随机波动,且幅度扰动会被限幅机制所抑制,频率的随机波动在频率域表现为边带噪声谱.

图1 VCO核心电路图

基于噪声滤波技术的互补交叉耦合差分振荡器核心电路图见图1.由图可知,电感L1和电容C1插在共模点S1和Mtail产生的尾电流源之间,谐振于频率2ω0处,为共模点S1提供高阻抗,抑制了谐振回路有载品质因数的降低.共模点S1的阻抗由L1的品质因数决定.同样,在共模点S2和地之间插入由L2和C2构成的谐振网络,提高共模点S2的阻抗,抑制了MOS管MN1和MN2对谐振回路品质因数的降低.

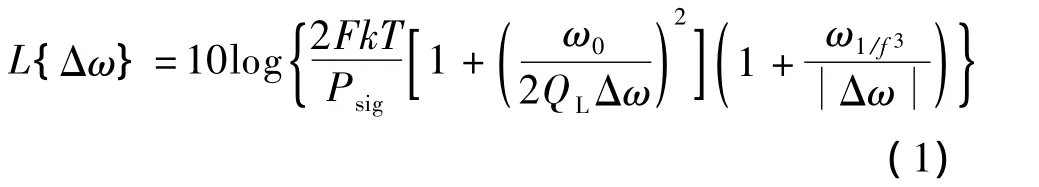

根据Leeson[7]的分析,VCO的相位噪声可以表示为

式中,F为经验参数;k为波尔兹曼常数;T为绝对温度;Psig为谐振电路的功耗;ω0和 ω1/f3分别为1/f2和1/f3相位噪声区域的拐角频率;Δω为频偏;QL为谐振腔的有载品质因数,主要由谐振电感的品质因数决定.在电感值选定后,应该选择圈数少、内径大的电感.设计中采用二次谐波谐振滤波电路以有效增加QL.

根据Hajimiri等[1]的分析,振荡器输出波形越对称,ω1/f3和相位噪声越小.本设计中采用交叉耦合差分结构,可以得到对称的波形,从而使得ω1/f3和相位噪声均较小.

尾电流管的闪烁噪声和高频噪声可以上变频变为相位噪声.尾电流管的闪烁噪声谱密度为

式中为尾电流平方均值;Δf为频率变化值;Kf为工艺相关常量;W和L分别为MOS管的栅宽和栅长;COX为单位面积栅氧电容;gm为MOS管的跨导.

可见,增大尾电流管的尺寸可以降低闪烁噪声.与NMOS器件相比,PMOS器件具有较小的闪烁噪声,故设计中选用PMOS晶体管为VCO提供偏置电流.

1.1 大滤波电容

根据Rael等[8]的分析,尾电流源中闪烁噪声和偶次谐波附近的噪声将会通过单平衡混频过程进入振荡器相位噪声中.图1中,与振荡器尾电流管Mtail并联的大电容Ctail可以过滤或者抑制偶次谐波附近的噪声.实际上,该大电容与尾电流管Mtail构成了一个低通滤波器.选择合适的容值,使滤波器的截止频率低于二次谐波频率2ω0,便可抑制偶次谐波附近的噪声,避免其影响振荡器相位噪声.

此外,根据 Hajimiri等[9]的分析,大电容Ctail可以降低MP1和MP2中漏电流的占空比以及MOS管沟道的热噪声,减少敏感时刻的噪声源,从而降低振荡器的相位噪声.

1.2 二次谐波谐振滤波网络

尾电流源在VCO中的作用为:①为振荡器提供偏置电流;② 在差分对管的共模点处提供高阻抗[10].VCO振荡过程中,在振荡波形的波峰与波谷处差分对管进入线性区,此时其电阻较小,从而降低了谐振腔的有载品质因数QL.由于共模点S1和S2处的振荡频率为2ω0,故可以在这2个共模点处分别插入一个窄带电路,并使此电路谐振于2ω0.窄带波网络为谐振腔提供了较高的阻抗,从而阻止了QL的降低.

1.3 开关电容阵列

根据Emad等[10]的分析,可变电容可以将AM噪声调制为相位噪声.相位噪声的转化程度受可变电容灵敏度kvar影响,kvar越大,则AM-FM 调制越明显.对于一个调谐范围较宽的LC VCO,如果仅采用大范围可变电容实现频率调谐,则可变电容灵敏度kvar较大.

Nbit开关电容阵列可以将整个可调频率范围分为2N个子区域.子区域的选择通过闭合与断开开关电容来实现,子区域内频率的调谐则通过控制可变电容来实现.由此便可使任何一个子区域里可变电容的灵敏度kvar都较小,从而有效降低可变电容AM-FM调制效应造成的相位噪声.

1.4 偏置滤波网络

振荡器尾电流源的偏置一般由带隙基准电流源提供.为了阻止带隙基准和偏置电流镜的噪声进入尾电流源影响振荡器的相位噪声,可以在偏置电路中加入低通滤波器[3].低通滤波器的作用是过滤高频噪声,由简单的RC网络构成.图1中,RLP和CLP构成了一个低通滤波器,其3 dB带宽为11 kHz.

2 电路设计

图2为LC VCO的整体结构图,采用互补交叉耦合差分结构.MOS 管 MP1,MP2,MN1,MN2组成了差分负阻管.与仅使用PMOS或者NMOS负阻管的差分结构相比,互补交叉耦合差分结构振荡器的输出振荡波形更加对称,1/f3区域的相位噪声更小[11].振荡器采用电流偏置的方法.Mtail产生的尾电流源为振荡器提供偏置电流,使振荡器工作在电流受限区[12].

图2 LC VCO的整体结构图

为了增加振荡器的频率输出范围,振荡器采用3 bit开关电容完成频率粗调,采用MOS变容管完成频率细调.图2中,S1~S7构成了3 bit开关电容阵列;2个电感LP串联构成了谐振电感;积累型MOS管可变电容构成了谐振腔可变电容Cvar;Cfix为谐振腔固定电容;Rb为谐振腔偏置电阻.

MOS管Mcur和Mtail组成电流镜,放大带隙基准所提供的偏置电流Ibias.电阻RLP和电容CLP构成偏置滤波网络,抑制偏置电路的噪声.与尾电流管Mtail并联的大电容Ctail抑制了尾电流管二次谐波噪声及更高次谐波噪声,改善了振荡器的相位噪声.L1与C1,L2与C2分别在振荡器2个共模点处组成二次谐波滤波网络,极大地降低了相位噪声.振荡器差分输出端的两级反相器构成了输出缓冲器.

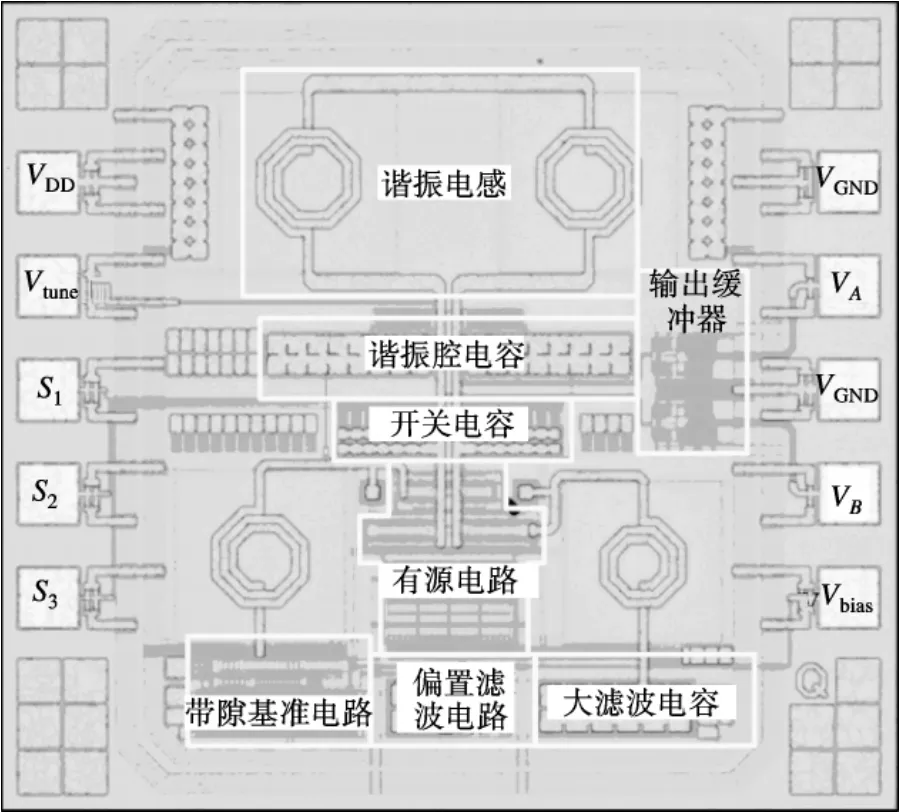

3 版图设计及后仿真

采用TSMC 0.35 μm CMOS工艺绘制振荡器的版图.版图采用完全对称的形式,降低了寄生参数,保证了器件的良好匹配性,有助于提高LC VCO的性能.版图中,2个谐振电感应保持足够远的距离,以防止过大的互感出现.有源电路应远离电感,以防止受到电感大电流的影响.连接谐振电感、谐振电容、开关电容和有源负阻的金属线应采用方块电阻小、与衬底寄生电容小的最顶层Metal-4[13],且引线应尽量短,以减小电感和电容的寄生串联电阻,改善相位噪声.振荡器控制信号线需远离其他信号线,以防止信号耦合.VCO的版图布局见图3,面积大小为 1 285.3 μm ×1 162.7 μm.

使用Cadence Spectre RF仿真工具对LC VCO进行后仿真.VCO的工作电压为3.3 V.

图3LC VCO版图

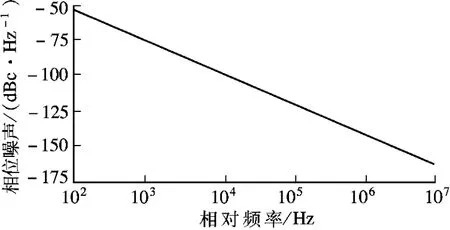

后仿真相位噪声曲线如图4所示.由图可知,中心频率1.81 GHz处VCO的相位噪声为-113.5 dBc/Hz@1 MHz.

图4 后仿真的相位噪声曲线

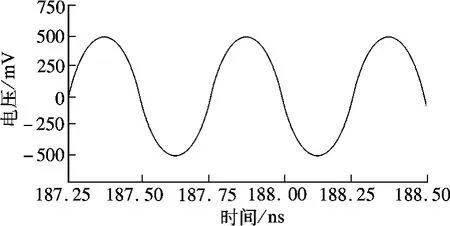

图5为VCO差分输出经过大隔直电容后接理想巴伦的振荡信号.由图可知,差分摆幅Vm=520 mV.根据功率计算公式

可得VCO的差分输出功率为4.3 dBm.

图5 差分瞬态输出

4 测试结果

图6为所用芯片照片.测试时采用键合测试方法.测试仪器为Agilent E5052A信号源分析仪.测试数据包括频率调谐、相位噪声和输出功耗.

图7为VCO的测试频率调谐曲线.图中,VCB为控制电压.由图可知,VCO的频率调谐范围为1.558 ~2.065 GHz,频率调谐范围高达 28%.VCO的整个频率范围被分成8段,控制电压范围为1.0~2.0 V,每段均具有良好的线性度.

图6 VCO芯片照片

图7 VCO测试频率调谐曲线

图8为VCO的测试相位噪声曲线.由图可知,中心频率1.81 GHz处的相位噪声为-111.4 dBc/Hz@100 kHz和 -133.3 dBc/Hz@1 MHz.电源电压为3.3 V,VCO的核心电路消耗电流约为10 mA.

图8 VCO测试相位噪声曲线

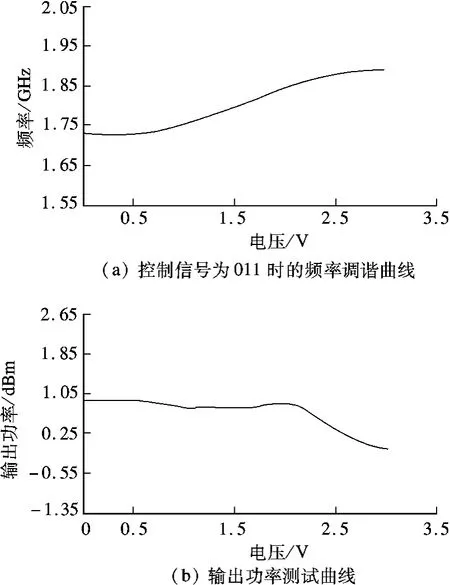

图9(a)为开关电容控制信号为011时的频率调谐曲线.由图可知,当控制振荡器电压Vctrl=1.6 V时,输出频率约为1.81 GHz.图9(b)为输出功率测试曲线.由图可知,当Vctrl=1.6 V时,输出频率约为1.81 GHz,振荡器输出功率约为0.75 dBm.

图9 频率调谐曲线和输出功率测试曲线

VCO的综合性能指数定义为

式中,L{Δf}为频偏 Δf处的相位噪声;fosc为VCO的中心频率;PmW为VCO的核心功耗.F的绝对值越大,VCO的整体性能越优良.本文所设计的VCO的综合性能指数为-183.3 dBc/Hz.

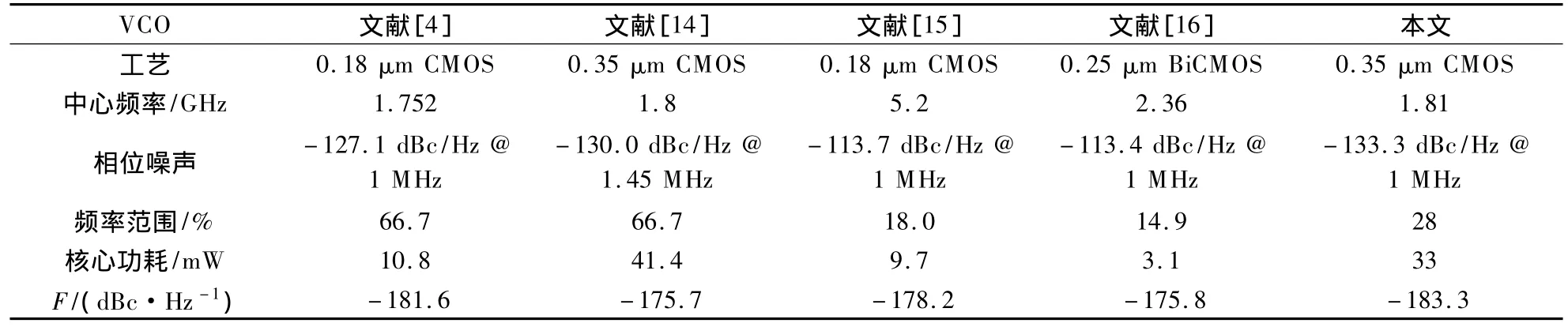

本文设计的VCO与其他VCO的性能比较见表1.由表可知,本文设计的VCO具有合理的频率调谐范围和功耗,相位噪声性能好,整体性能优良.

表1 VCO的性能比较

5 结语

本文基于TSMC 0.35 μm CMOS工艺设计并实现了一种用于PLL频率合成器中的低相位噪声LC VCO.该VCO采用互补交叉耦合差分结构,使用开关电容阵列技术增大频率调谐范围,采用大滤波电容、二次谐波谐振滤波网络、开关电容阵列和偏置滤波来降低相位噪声.测试结果表明,LC VCO的综合指标优良,中心频率处输出功率为0.75 dBm,综合性能指数为 -183.3 dBc/Hz,因而有望在无线收发机系统中得到广泛应用.

[1] Hajimiri Ali,Lee Thomas H.Low noise oscillators[M].Norwell,Massachusetts,USA:Kluwer Academic Publishers,1999:4-7.

[2]Li Z B,Kenneth K O.A low phase noise and low power multiband CMOS voltage controlled oscillator[J].IEEE Journal of Solid State Circuits,2005,40(6):1296-1302.

[3] Fang Xiangning,Zeng Jun,Li Bin,et al.A fully integrated differential double frequency wide tuning range CMOS LC VCO for 2.4 GHz IEEE802.15.4/ZigBee[C]//Proceedings of2010IEEE International Symposium on Signals Systems and Electronics.Chengdu,China,2010:1-4.

[4] Jongsik Kim,Jaewook Shin,Seungsoo Kim,et al.A wide-band CMOS LC VCO with linearized coarse tuning characteristics[J].IEEE Transactions on Circuits and SystemsⅡ:Express Briefs,2008,55(5):399-403.

[5] Wang Le,Parag Upadhyaya,Sun Pingping,et al.A 5.3 GHz low-phase-noise LC VCO with harmonic filtering resistor[C]//Proceedings of2006IEEE International Symposium on Circuits and Systems. Kos, Greece,2006:3237-3240.

[6]Mohamed S,Ortmanns M,Manoli Y.Design of current reuse CMOS LC VCO[C]//Proceedings of2008IEEEInternational Conference on Electronics,Circuits and Systems.St.Julian's,Malta,USA,2008:714-717.

[7] Leeson D B.A simple model of feedback oscillator noises spectrum[J].Proceedings of the IEEE,1966,54(2):329-330.

[8]Rael J J,Abidi A A.Physical processes of phase noise in differential LC oscillators[C]//Proceedings of2000IEEE Custom Integrated Circuits Conference.Orlando,FL,USA,2000:569-572.

[9] Hajimiri Ali,Lee Thomas H.Design issues in CMOS differential LC oscillators[J].IEEE Journal of Solid State Circuits,1999,34(5):717-724.

[10]Hegazi E,Sjoland H,Abidi A A.A filtering technique to lower LC oscillator phase noise[J].IEEE Journal of Solid State Circuits,2001,36(12):1921-1930.

[11] Hajimiri Ali,Lee Thomas H.A general theory of phase noise in electrical oscillators[J].IEEE Journal of Solid State Circuits,1998,33(2):179-194.

[12] Ham Donhee,Hajimiri Ali.Concepts and methods in optimization of integrated LC VCOs[J].IEEE Journal of Solid State Circuits,2001,36(6):896-909.

[13] Hegazi E,Rael J J,Abidi A A.The designer's guide to high purity oscillators[M].Dordrecht,the Netherlands:Kluwer Academic Publishers,2005:85-89.

[14]Shin J W,Kim J S,Kim S S.A wideband fractional-Nfrequency synthesizer with linearized coarse-tuned VCO for UHF/VHF mobile broadcasting tuners[C]//Proceedings of2007IEEE Asian Solid State Digital Conference.Jeju,Korea,2007:440-443.

[15] Young Jin Moon,Yong Seong Roh,Chan Young Jeong,et al.A 4.39 -5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO gain variation[J].IEEE Microwave and Wireless Components Letters,2009,19(8):524-526.

[16]Zihir S,Tasdemir F,Dinc T,et al.A new resonant circuit for 2.45 GHz LC VCO with linear frequency tuning[C]//Proceedings of2011IEEE Microwave Integrated Circuits Conference.Manchester, United Kingdom,2011:390-393.

Design and implementation of LC voltage controlled oscillator with low phase noise

Chang Changyuan Wang Shaoquan Chen Yao Yu Dongsheng

(School of Integrated Circuit,Southeast University,Nanjing 210096,China)

Based on TSMC 0.35 μm CMOS process,a fully integrated LC voltage controlled oscillator(VCO)used in phase lock loop(PLL)frequency synthesizer with low phase noise is designed and implemented.The LC VCO has a complementation cross-couple differential structure and adopts switched-capacitor technique to increase frequency tune range.Large filtering capacitance,second harmonic filtering network,switched-capacitor array and bias filter network are used to reduce phase noise.Simulation,layout design and post-simulation are completed by TSMC 0.35 μm CMOS process.The chip size is 1 285.3 μm × 1 162.7 μm.Chip testing results show that the frequency of the LC VCO can be tuned from 1.558 to 2.065 GHz.The tune range is 28%.In the center oscillation frequency,the phase noise of the LC VCO can achieve -133.3 dBc/Hz at 1 MHz,and the FOM(figure of merit)is -183.3 dBc/Hz.Thus,the overall performance of the designed VCO is good.

LC voltage controlled oscillator;phase noise;switch capacitance array;CMOS(complementary metal oxide semiconductor )

TN432

A

1001-0505(2012)06-1052-06

10.3969/j.issn.1001 -0505.2012.06.006

2012-05-10.

常昌远(1961—),男,博士,副教授,ccyycc@seu.edu.cn.

国家核高基资助项目(2009ZX01031).

常昌远,王绍权,陈瑶,等.一种低相位噪声LC压控振荡器的设计与实现[J].东南大学学报:自然科学版,2012,42(6):1052-1057.[doi:10.3969/j.issn.1001 -0505.2012.06.006]