SRAM型FPGA单粒子效应逐位翻转故障注入方法

2012-08-07宋凝芳秦姣梅江云天

宋凝芳 秦姣梅 潘 雄 江云天

(北京航空航天大学仪器科学与光电工程学院,北京100191)(第二炮兵装备研究院,北京100085)

SRAM(Static Random Access Memory)型FPGA(Field Programmable Gate Array)具有信息密度大、性能高、可重复编程的特性,在空间领域得到了广泛应用[1].然而SRAM型FPGA对空间中的单粒子十分敏感,易发生单粒子翻转.单粒子翻转会导致FPGA中存储单元的内容改变,导致计算结构错误、程序执行序列错误等,甚至导致系统的崩溃[2].因此,在应用于空间环境中之前,必须对FPGA进行容错设计,并对设计的可靠性进行有效测试和评估.

目前,在地面上模拟空间中的单粒子翻转主要采用辐射模拟和故障注入的方法.辐射模拟即采用重离子或高能质子等模拟源来辐照器件,测试其辐射敏感参数,为器件选型和预估实际辐射环境中的单粒子翻转率提供依据.然而,此方法成本很高,注入位置难以控制,而且危险性高.

与此相比,模拟单粒子翻转的第2种方式,即故障注入方法则弥补了上述缺点,成为地面模拟单粒子翻转的重要手段.尤其是利用SRAM型FPGA重配置特性进行的故障注入方法得到了极大的关注.文献[3]提出采用部分动态重配置,随机注入的方法对FPGA进行故障注入.文献[4-5]中提到开发了故障注入平台SLAAC1,对Virtex系列芯片采用TMR(Triple Modular Redundancy)技术后的单粒子翻转可靠性进行评测.此平台只适用于Virtex系列芯片,对VⅡ及以上系列不支持.国内方面,文献[2]实现了基于重配置技术的故障注入,但试验时需由用户提供翻转位的地址.而实际上用户无法知道设计中对应电路资源的配置位位置,在测试时很难决定需要翻转的配置位,从而为电路的可靠性评测造成了很大的困难.

本文提出的逐位翻转故障注入方法,无需用户了解数字电路设计的实现细节及提供故障注入位置,就可得到设计的可靠性参数,为设计的可靠性评估和改进提供依据.适用的故障类型包括单粒子翻转及单粒子瞬态脉冲引起的所有单位配置位故障.

1 逐位翻转故障注入方法

故障注入方法是一种评测容错机制是否有效的试验方法,通过有意识地向系统中引入故障来加速容错机制的评测.FPGA发生单粒子翻转后,其故障表现为其中存储单元的内容改变,而这些存储单元的内容是由比特文件中的配置位决定的.SRAM型FPGA动态重配置的特性使得可在程序运行中人为翻转配置位,从而引入与单粒子翻转同等效力的故障,模拟FPGA空间应用发生单粒子翻转时的状况.通过分析故障注入后电路的输出功能,评测逻辑设计的抗单粒子翻转能力.

为了能对任何一个用FPGA实现的电路在其设计完成后评测它的抗单粒子翻转可靠度,并主动找出其配置存储单元中的敏感位,提出了一种逐位翻转的故障注入方法.

逐位翻转,顾名思义,即在程序运行过程中对配置位进行逐位翻转,然后逐次动态重配置到FPGA中,检测翻转位对设计输出的影响.翻转后引起输出结果错误的配置位即为敏感位.此方法可以检测出配置存储单元中的所有敏感位,并通过生成一个msk.dat掩码文件,定位出敏感位在配置文件中的具体地址.

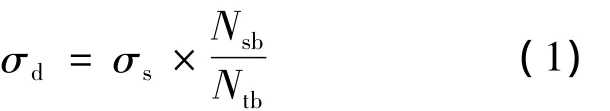

得到敏感位个数后,可计算得到电路设计配置存储单元的动态翻转截面[5]为

式中,σs为器件配置存储单元的静态翻转截面;σd为电路设计配置存储单元的动态翻转截面,σd的单位与σs相同,为 cm2/器件;Nsb为敏感位位数;Ntb为配置位总位数.与静态翻转截面反映器件的抗单粒子翻转能力不同,动态翻转截面反映的是FPGA实现的用户设计的抗单粒子翻转能力,与使用的器件和用户设计均有关系.

将敏感位位数乘以每位的翻转率μ,就可得系统的失效率λ,表达式为

得到λ后,由于系统可靠度服从泊松分布,其可靠度表达式为

式中,t为系统运行时间;R为系统可靠度.根据式(3)可绘出系统的可靠度变化曲线.

2 逐位翻转故障注入实现

2.1 故障注入系统结构

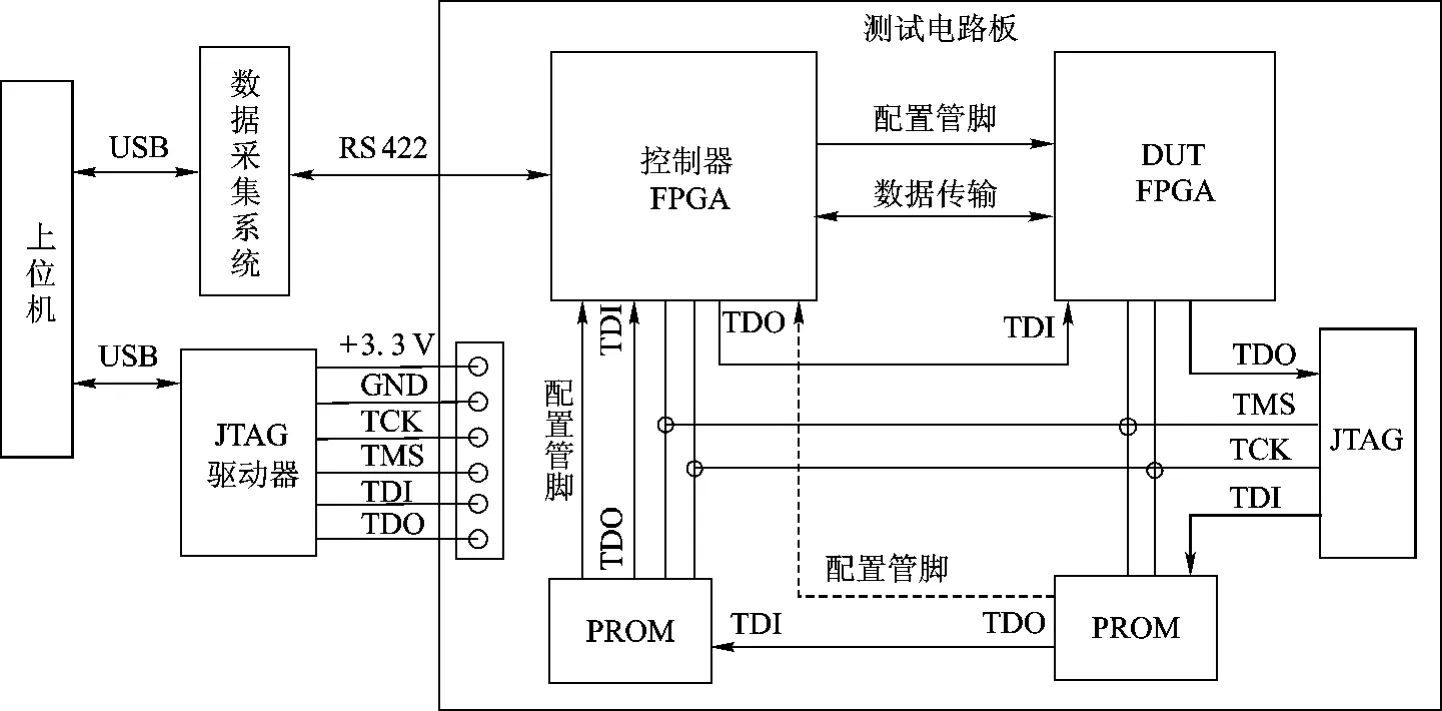

根据上述逐位翻转方法,故障注入系统的实现需有一个控制芯片来控制配置位的翻转和被测芯片的重配置,并将检测到的敏感位及敏感位位置(由msk.dat体现)上传到上位机.

设计的故障注入系统结构框图如图1所示.包含测试电路板、数据采集系统和上位机3部分.

测试电路板包含控制器FPGA、被测FPGA(DUT,Device Under Test)及各自的 PROM(Programmable Read-Only Memory).控制器负责的主要功能为:①DUT的初始配置;②DUT配置数据的翻转和动态重配置;③DUT输出结果和预知正确结果的比较,及比较结果的上传.

数据采集系统起到协议转换和平衡数据传输速率的作用,负责上位机命令的下达和测试电路板数据的上传.

2.2 故障注入试验流程

整个试验的流程如图2所示.分为以下几步:

1)上位机上电,控制器将DUT PROM中的配置数据发送给DUT,完成DUT的初始配置;

2)上位机发送逐位翻转命令,控制器对DUT配置数据进行逐位翻转;

3)控制器将翻转位所在数据帧动态重配置到DUT中;

图1 故障注入系统结构框图

图2 试验流程图

4)比较重配置后DUT输出结果和预知的正确结果.引起输出结果错误的位为敏感位,错误数加1,并将相应位的msk掩码值记为1;

5)将msk值和错误总数上传.上传的数据在上位机中生成一个msk.dat掩码文件.根据此文件可知敏感位的总位数及具体位置.

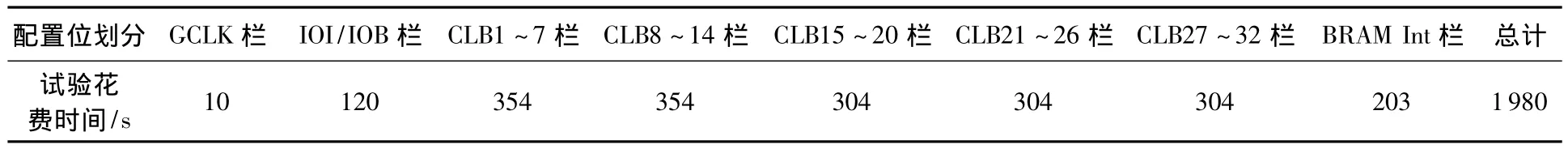

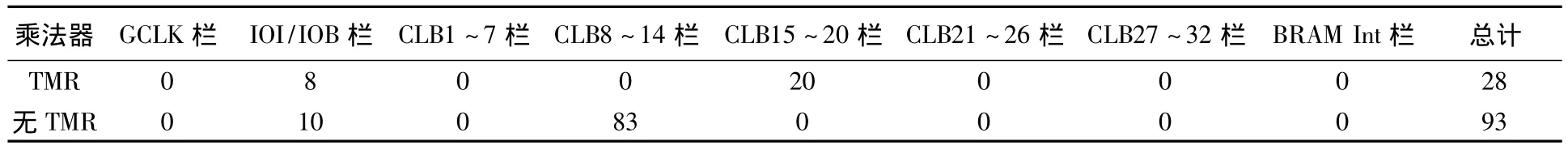

考虑到控制器的资源使用以及敏感位位置分析的方便,将FPGA的配置位按栏类型做了如表1划分,分别进行逐位翻转.通过这种方式可直观看出每类配置位的敏感位个数.

另外,方法在设计时利用SRAM型FPGA可以局部动态重配置的优点,每次只重配置翻转位所在的1帧数据,节约了大量的时间.试验所用XC2V1000系列芯片除BRAM(Block Random Access Memory)外共有配置位2 876 416位.即一次试验共需重配置2 876 416次.在配置时钟选择2 MHz时,如果重配置全部采用全局重配置,试验共需187 h,是不现实的.而本方法只需30 min左右即可将所有配置位遍历一遍,节约了大量的时间,也为重复试验实现了可能.试验花费时间如表1所示.

表1 逐位翻转试验时间花费

3 故障注入试验及结果分析

3.1 测试对象

对经过TMR设计的乘法器和不经过TMR设计的乘法器分别进行逐位翻转试验,比较测试结果.

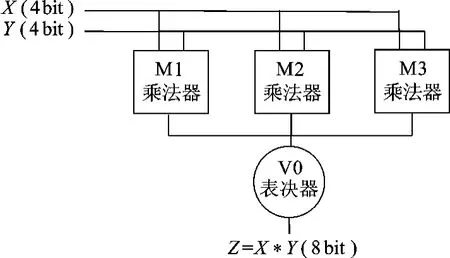

TMR采用输入和乘法模块均三模冗余,单表决器输出的设计方法(如图3所示).同时,为了避免TMR单点失效问题,各模块进行了布局操作.将M1模块放置于CLB(Control Logic Block)1~7栏,M2放置于CLB8~14栏,M3放置于CLB21~26栏,V0放置于CLB15~20栏.将所有的输入输出放置在芯片左侧和右侧的管脚.未经过TMR设计的乘法器其乘法器模块放置于CLB8~14栏.乘法器输入为4位×4位,输出为8位.两种设计的资源使用情况如表2所示.

图3 TMR乘法器设计结构图

表2 两种设计资源使用情况

3.2 测试结果及分析

3.2.1 测试结果

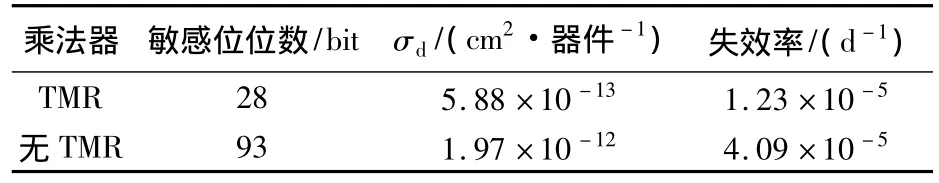

对上述设计进行试验,结果如表3所示.

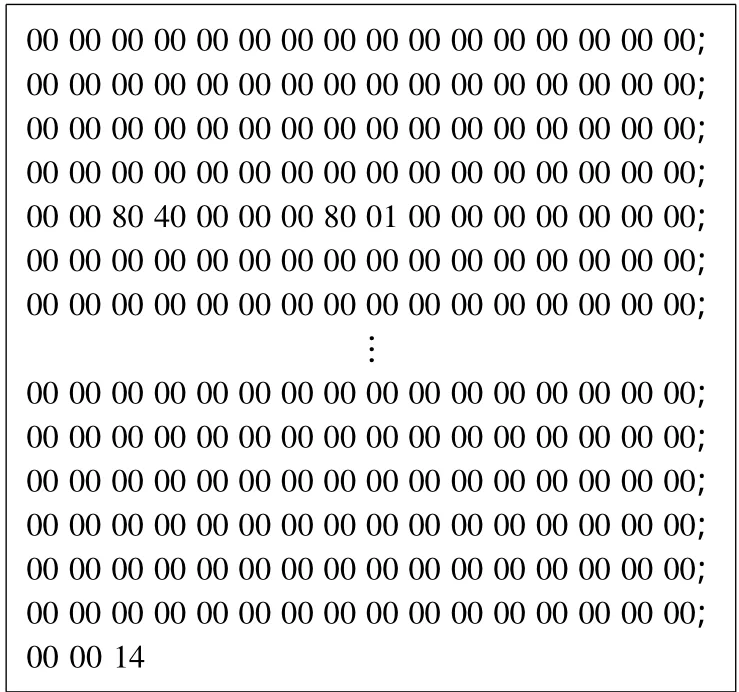

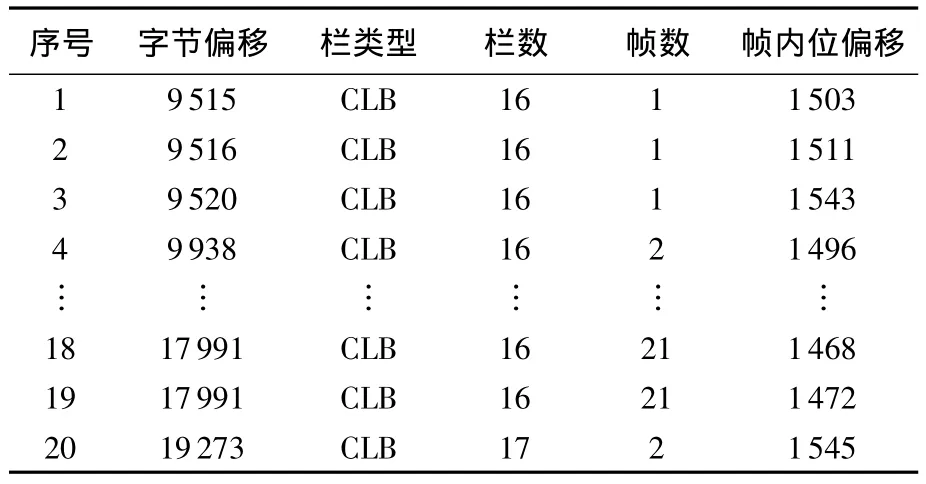

TMR乘法器CLB15~20栏逐位翻转试验生成的msk.dat文件截取部分如图4所示.文件中为1的位即表示配置数据中相应位为敏感位,最后3个字节代表敏感位的总位数.对msk文件进行简单分析即可得敏感位的具体位置,见表4.

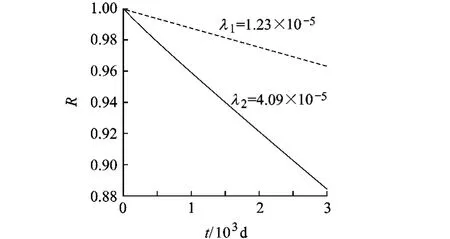

根据实验结果,由式(1)、式(2)可得两种电路设计的可靠性参数如表5所示.这里的σs采用粒子能量为63.3 MeV时XC2V1000的静态翻转截面7.86 ×10-8cm2/器件[6].翻转率采用 Xilinx公司发布的 VirtexⅡ系列芯片配置位翻转率4.4 ×10-7/(bit·d)[7].由式(3),得到两种设计的可靠度变化曲线如图5所示.

表3 逐位翻转试验结果bit

图4 TMR乘法器CLB15~20栏msk.dat文件

表4 TMR乘法器CLB15~20栏敏感位位置

表5 设计的可靠性参数

3.2.2 试验结果验证

为了验证所得敏感位位置的正确性,对TMR乘法器试验得到的敏感位进行逐位测试.对应查找到的敏感位,在配置文件中翻转相应位,然后逐次用JTAG下载器下载到程序中运行,结果均造成程序的输出结果错误.从而表明试验得到的敏感位位置是正确的.

图5 两种设计的可靠度变化曲线

3.2.3 试验讨论

根据试验结果可以得到如下分析:

1)本试验电路设计为组合逻辑电路,没有用到时钟和BRAM,因此,敏感位完全位于CLB栏和IOI/IOB栏.

2)TMR设计的CLB栏敏感位只存在于表决器模块中,因此,要想进一步提高设计的可靠度,应该提高表决器模块的可靠度或采用多表决器的方法.这与理论分析是相符合的.

3)此方法在对时序电路进行故障注入试验时,需提前判断好故障传输至输出端可能所需的最长周期,以在故障判断时做相应周期延时.

4)翻转的配置存储位中包含一部分的用户存储单元,即决定触发器功能的比特位.但触发器占资源很少,只有0.42%左右[5],可以忽略.

5)此方法只能进行单位翻转,要想遍历所有的两位翻转或多位翻转是不现实的.但实际中,单粒子效应引起的95%以上是单位翻转[8],且采用刷新功能可以有效防止翻转积累,因此并不影响本试验对可靠度的评测.

4 结论

提出的逐位翻转故障注入方法可以检测出用户电路设计配置存储资源的敏感位,得到其动态翻转截面和失效率,绘出可靠度变化曲线,从而对电路设计在空间应用中的可靠度进行评测.试验花费时间较少,一次完整的试验只需33 min.试验不仅可以得到敏感位的位数,还可以对敏感位的位置进行定位,对设计改进有很好的参考意义.但方法主要针对单位配置位翻转故障,对多位翻转、累加翻转故障及单粒子功能中断故障的故障注入方法还有待进一步研究.

References)

[1]费尔南达·利马·卡斯腾斯密得,路易吉·卡罗,里卡多·赖斯.基于SRAM的FPGA容错技术[M].杨孟飞,龚健,文亮,等译.北京:中国宇航出版社,2009:1-8 Fernanda L K,Luigi C,Ricardo R.Fault-tolerance techniques for SRAM-based FPGAs[M].Translated by Yang Mengfei,Gong Jian,Wen Liang,et al.Beijing:China Astronautic Publishing House,2009:1 -8(in Chinese)

[2]齐鑫,冯文全.基于动态重配置的SEU故障检测与修复系统的设计[C]//方滨兴.中国通信学会第六届学术年会论文集.广州:中国通信学会,2009:82-87 Qi Xin,Feng Wenquan.The design of a SEU fault detection and recovery system based on dynamic reconfiguration[C]//Fang Binxing.The Sixth Conference Proceedings of China Communications Association.Guangzhou:China Institute of Communications,2009:82 - 87(in Chinese)

[3]Leveugle R,Antoni L,Feher B.Dependability analysis:a new application for run-time reconfiguration[C]//Amaral J N.Proceedings of the International Parallel and Distributed Processing Symposium(IPDPS).Los Alamitos:IEEE Computer Society Press,2003:345-351

[4]Johnson E,Caffrey M P,Graham P S,et al.Accelerator validation of an FPGA SEU simulator[J].IEEE Transactions on Nuclear Science,2003,50(6):2147 -2157

[5]Morgan K S,McMurtrey D L,Pratt B H,et al.A comparison of TMR with alternative fault-tolerant design techniques for FPGAs[J].IEEE Transactions on Nuclear Science,2007,54(6):2065-2072

[6]Quinn H M,Graham P S,Morgan K S,et al.An introduction to radiation-induced failure modes and related mitigation methods for Xilinx SRAM FPGAs[C]//Plaks T P.Proceedings of the International Conference on Engeering of Reconfigurable Systems Algorithms(ERSA).Las Vegas:CSREA Press,2008:139 -145

[7]Yui C,Swift C,Carmichael C.Singel event upset susceptibility testing of the Xilinx VirtexⅡ FPGA[C]//Katz R B.Military and Aerospace Applications of Programmable Devices and Technologies Conference(MAPLD).Washington D C:Kossiakoff Conference Center,2002:212 -217

[8]Quinn H M,Graham P S,Wirthlin M J,et al.A test methodology for determining space readiness of Xilinx SRAM-Based FPGA devices and designs[J].IEEE Transactions on Instrumentation and Measurement,2009,58(10):3380 -3395