基于无载频脉冲雷达信号的高速数字采样方法与实现

2012-07-24沈绍祥叶盛波方广有

沈绍祥*①② 叶盛波① 方广有①

基于无载频脉冲雷达信号的高速数字采样方法与实现

沈绍祥叶盛波方广有

(中国科学院电子学研究所电磁辐射与探测技术重点实验室 北京 100190)(中国科学院研究生院 北京 100049)

该文针对无载频脉冲雷达信号周期重复性的特点,提出了一种全新的高速数字采样方法和原理。该方法利用FPGA的差分比较器端口构成高速1 bit量化器,采用FPGA内部多相位时钟,对1 bit数据流进行并行交替数字采样,并缓冲编码,从而获得上吉赫兹的等效数字采样率。通过将多个比较电平下的1 bit采样数据进行累积,从而完成高速数字采样过程。在Xilinx的XC2V3000的FPGA中实现了该方法,获得了采样率达1.6 GHz的8 bit等效高速模数转换器功能。该设计方法不仅能够提高等效采样方式的效率,而且与高速实时采样相比,具有低功耗、低成本的优势,在实际中获得了良好的应用。

现场可编程门阵列;数字采样;1 bit量化器;比较电平

1 引言

无载频脉冲雷达信号是一种时域超宽带信号,具有准周期性,超宽带的特点。工程应用中,传统上对此类信号的采集均采用等效采样(等效顺序采样)方式。该方法降低对模数转换器的转换速率要求。但实际应用中,这种采样方式大多是一个回波采样一次(或为累积使用,多采集几个样本累积起来),获得一个样本,回波利用率较低。若一道回波需采集样本数越多,所需系统工作的时间就越长,不利于野外探测作业。

与等效采样相比,实时采样可提高工作效率和回波利用率。但对于无载频脉冲雷达信号而言,若采用实时采样,则ADC的采样率非常高。如脉冲雷达天线的中心频率为300 MHz时,需要ADC的采样率至少是600 MHz。而这样的商业化ADC,价格高、功耗大、购买渠道有限,同时系统设计难度大。

本文结合等效顺序采样和实时采样的特点及无载频脉冲雷达信号的准周期性,参考Flash ADC结构与TDC结构,给出了一种全新的利用FPGA高速差分端口的数字采样方法。该比较器P端输入雷达信号,N端接入参考比较电压,通过比较器后形成1 bit数据流,然后使用多相位时钟对1bit数据流进行数字采样,从而形成高速采样率的1 bit采样点。每一个比较电平采集一组时窗大小的记录,通过改变比较电平大小,从而获得多组不同比较电平下、相同时窗大小的1 bit采样点。将这些相应时刻1 bit采样点累积起来,就能够获得等效数位的高速ADC,相应实现了数字采样过程。在Xilinx公司的XC2V3000 FPGA上实现该设计方法,获得了1.6 GHz,等效8 bit ADC。已成功应用于某型号的双通道脉冲雷达中,在野外验证试验中获得了良好的测量效果。

2 数字采样原理

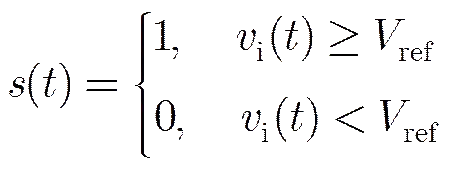

1 bit高速数字采样方法原理框图如图1所示。

图1 1bit数字采样原理框图

(2)

其中=1/。

可以看到,上面的过程就完成了对模拟信号的1 bit实时数字采样,其采样率为。当要求很高时,如1 GHz以上,实现难度较大,且对后续的处理电路要求极高。

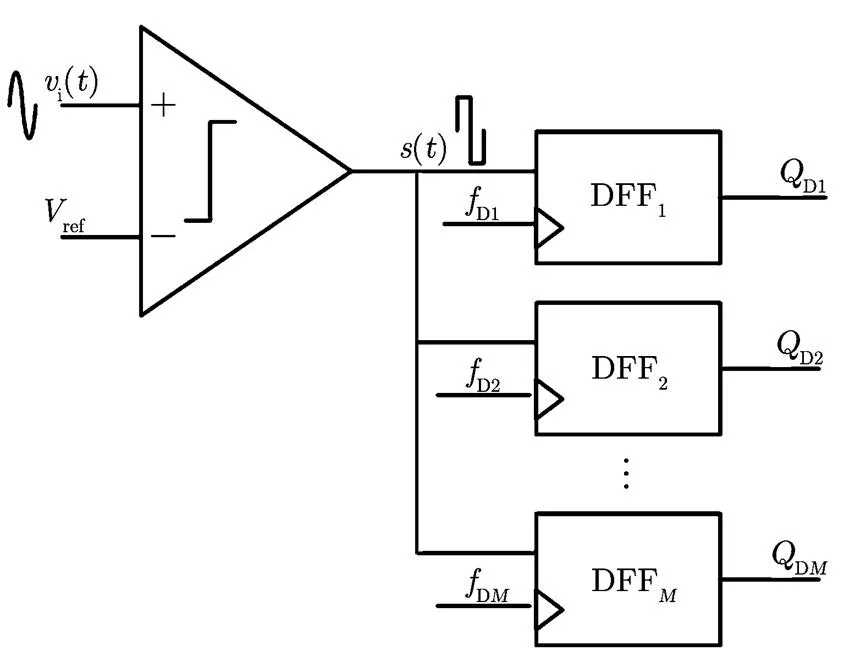

为提高采样率同时降低设计难度,采用并行交替数字采样方法,如图2所示。比较器输出到每个采样器的时延相同,路采样器的工作频率~均为,相位差为/,其中=1/,则系统采样率为。

图2 多路并行交替采样原理框图

(4)

3 数字采样设计实现

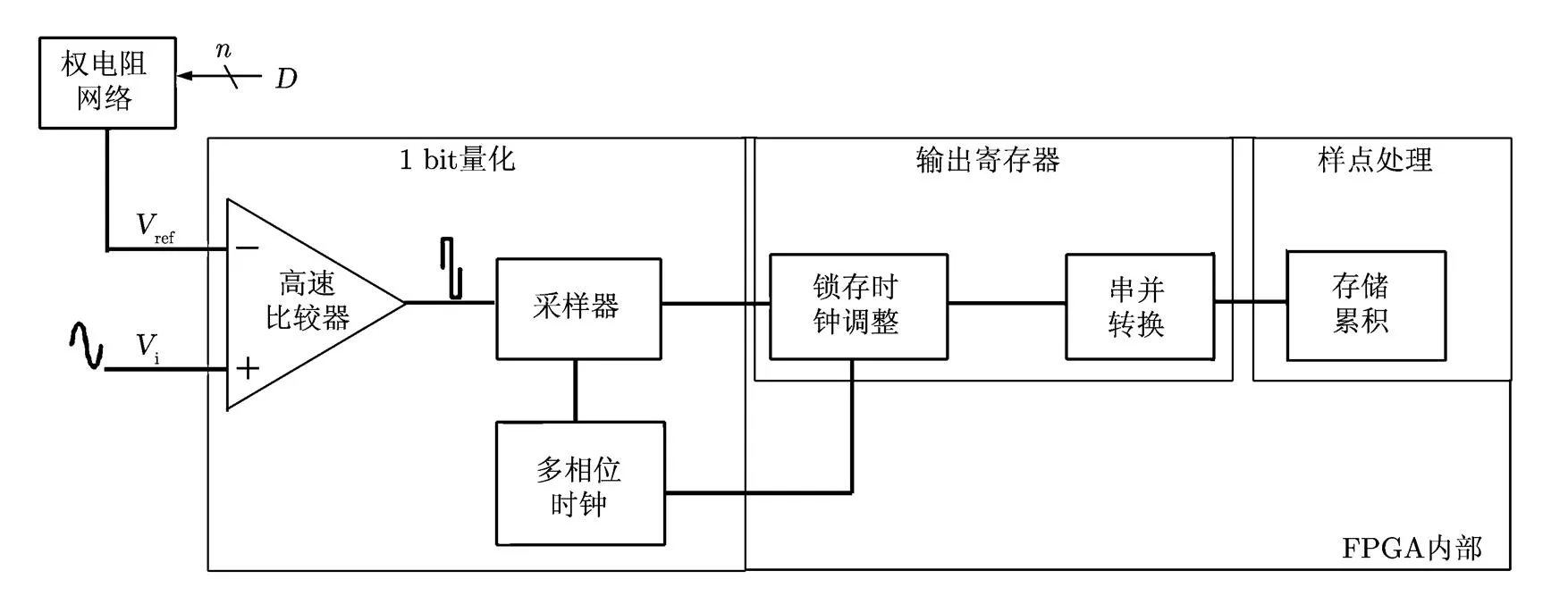

Flash ADC是一种全并行结构的ADC,其转换速率快,适合于高速ADC设计,但Flash ADC量化位数不高。这种全并行结构ADC提供了数字采样结构的设计思路,结合并行交替采样技术和上述数字采样原理给出了本文的数字采样设计框图,见图3。

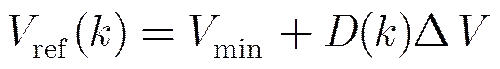

数字采样结构框图是由权电阻网络、1 bit量化、输出寄存器、样点处理几个部分组成。权电阻网络是实现不同比较电平使用,通过改变权电阻网络输入的数字量,就能够获得不同比较电平输出,其功能等效于DAC; 1 bit量化由高速比较器、采样器和多相位时钟组成,输入信号与比较电平在高速比较器上进行比较输出1 bit的数据流,再由采样器通过多相位时钟进行数字交替并行采样得到高采样率下1 bit量化数据;输出寄存器则是由锁存时钟调整、串并转换部分构成,将1 bit量化数据通过锁存时钟调整模块统一到一个相位时钟下进行锁存、串并转换模则是将1 bit数据流进行降频,并通过低频主逻辑时钟锁存存储;样点处理部分是将输出寄存器降频输出的1 bit数据流做存储,并将不同下的1 bit数据流进行累积,获得所需的等效量化位数为的编码数据。

图3 数字采样结构框图

3.1 权电阻网络

3.2 1 bit量化与输出寄存器

1 bit量化是数字采样的核心部分,其高速比较器起到了模拟信号到数字信号的1 bit转换过程。由数字采样原理分析知道,通过时间交替并行采样能够获得高速1 bit采样。该系统中并行交替采样时钟是关键。一般在交替并行采样系统中,其采样时钟基本上是通过时钟产生芯片和时钟分配芯片来获得多个不同相位的时钟,这种方法会造成通道之间的失配(幅度、时钟相位等)。

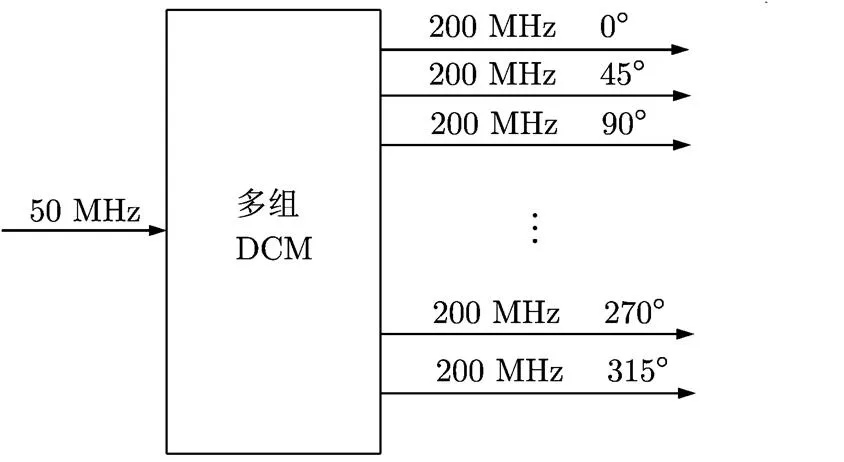

本文的数字采样过程除权电阻网络外的功能模块均通过一片FPGA来实现,多相位时钟则由内部的时钟管理器(DCM)来产生,结合FPGA内部的时钟布线资源,可以充分保证各时钟之间的相位一致性。而高速比较器是借助FPGA本身的差分端口来构成,采样器是利用FPGA内部的D触发器来实现。Xilinx公司的VirtexII XC2V3000,其内部有12个时钟管理器,内部时钟最高能工作到300 MHz,差分端口支持622 Mb/s数据率,兼容多种形式的接口电平。设计1.6 GHz采样率1 bit数字采样器,采用200 MHz, 8个相位时钟进行采样。取外部晶振时钟频率50 MHz,利用多组DCM构成多相位采样时钟,每个时钟之间相位相差45°,见图4。这8个相位时钟分别输入到8个采样器上进行交替并行采样。

通过1 bit量化之后的采样点,均是通过不同相位时钟并行交替采样得到。该不同相位时钟采集的1 bit数据流需要经过多级流水线逐步调整到某一个相位时钟下进行锁存,再由串并转换将数据流降频供后端进行存储。设计中200 MHz时钟周期为5 ns,每个采样时钟之间相差0.625 ns。锁存时钟调整模块按照流水线结构采用提前锁存方法设计,两级触发器之间至少保证有四分之三时钟周期数据稳定时间,消除可能存在的亚稳态情况。以0°和45°两个相位时钟情况来看,见图5(a),在第1级触发器上,0°和45°相位时钟各自采样并输出和。而第2级触发器上,由0°相位统一来锁存和并输出和。对而言,在45°相位时钟第2个时钟上升沿到来之前,被0°相位时钟提前1/8时钟周期进行锁存,此时数据有7/8时钟周期进行建立和保持。图5(b)是0°和45°相位时钟调整锁存时钟的时序关系,D=1/8,其中为时钟周期。其他相位间锁存时钟调整关系与此类似,最终统一到0°相位时钟锁存。

将所有相位的采样点统一到0°相位锁存后,其时钟频率仍然为200 MHz,需要进行降频后再存储到FPGA内部BlockRAM中。串并转换采用速度与面积之间的互换原则,用于实现该过程。取主逻辑时钟50 MHz,则200 MHz降频4级才能达到50 MHz频率,数据宽度从200 MHz, 8个1 bit样点经流水结构变宽为50 MHz, 32个1 bit样点输出。降频后可以减少系统功耗、降低逻辑时序要求,方便后级处理。

图4 多相位时钟形成框图

3.3 样点处理

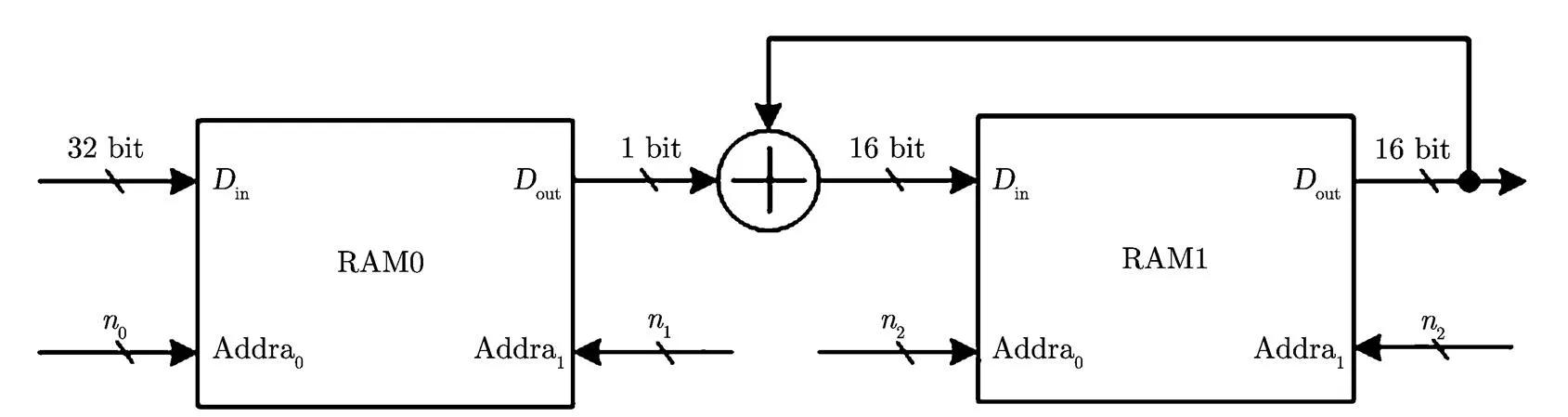

数字采样中的一个重要过程是将不同比较电平下的1 bit数据累积起来,以获得所需等效量化位数的编码值。样点处理是由存储1 bit样点的RAM0,加法器和保存累积和的RAM1组成,见图6。设回波信号周期为,比较电平某时刻的值为,在一个内,先将采集的1 bit量化数据存储于RAM0中,采集结束后,启动累积和操作,从RAM1中按地址取出之前个比较电平的样点累积和,与RAM0中取出的对应时刻1 bit样点值进行累积,将新累积和重新回写到RAM1相应地址中保存。当全部比较电平输出完成,则获得了所需等效量化位数的编码值。

3.4 实现约束

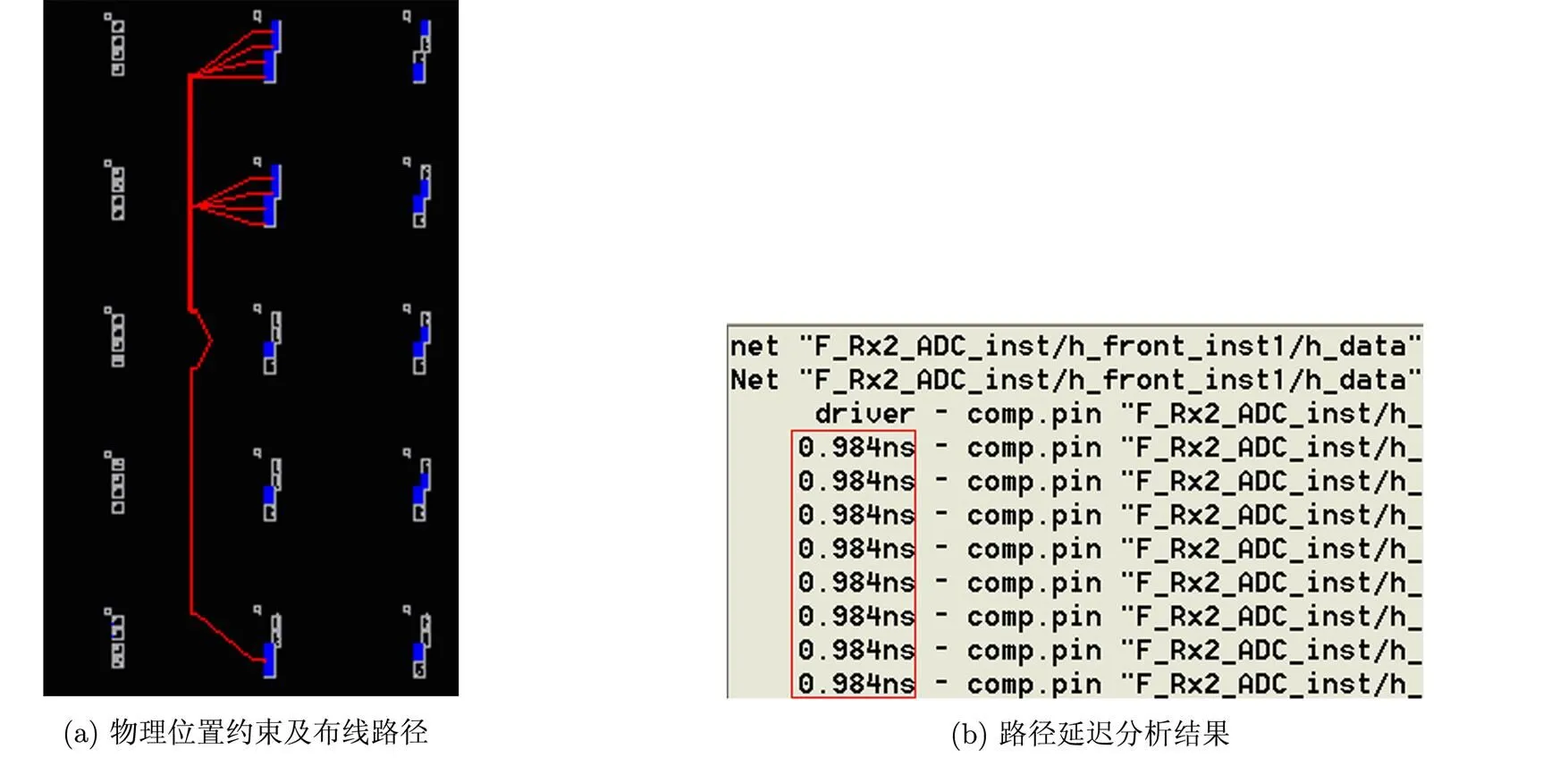

在FPGA实现数字采样过程中,需要进行一些关键的约束。从高速比较器输出到8个采样触发器之间的路径延迟要一致,这样才能保证信号到达8个采样触发器的时刻相同,通过手动放置8个采样触发器的物理位置并写入约束文件,来确保该约束。此过程很难一次确定合适位置,需经过多次尝试来最终确定,其原则是看布线延迟是否一致。图7(a)是采样触发器物理放置情况,8个触发器放置在4个silce中,线条所标识的是布线路径;图7(b)是差分端口到8个采样器的路径延迟大小,用线框标出,其值为0.984 ns。

4 试验测试

本文的高速数字采样技术试验硬件是通过一片Xilinx公司FPGA XC2V3000及辅助外围电路来构成,测试系统由试验硬件,信号源,直流电源组成。试验硬件的数字采样率为1.6 GHz,测试时,设置信号源输出分别为100 MHz和300 MHz正弦信号,输出幅度0.5 Vpp,经50W同轴电缆与试验硬件连接。通过数字采样获得归一化后的一道波形见图8。

在自行研制的某型号双通道探地雷达中,第1通道天线60 MHz中心频率,设计数字采样率400 MHz;第2通道天线500 MHz中心频率,系统采用外同步方法并结合可变延迟法设计采样率达到3.2 GHz。该雷达在甘肃天山老虎沟旱地冰川进行了野外验证试验。系统设置第1通道采样时窗20.48ms,第2通道采样时窗640 ns;取冰层的介电常数为3.2,其探测结果见图9(a)和图9(b)所示。第1通道探测结果表明122 m处存在显著的分层结构;第2通道探测结果表明在50.8 m处有分层结构。

图5 两级流水线及锁存时序关系

图6 样点处理框图

图7 采样器位置约束及延迟分析

图 8 正弦100 MHz, 300 MHz信号采样结果

(a) 第1通道探测结果

(b) 第2通道探测结果

图9 两通道野外验证试验探测结果

5 结论

该文给出了无载频脉冲信号的数字采样方法和原理,并且在Xilinx公司的XC2V3000的FPGA上实现了该采样方法,其等效采样率能达到1.6 GHz。而结合可变延迟法则可以进一步提高等效采样率,使其达到3.2 GHz。该方法设计简单,硬件结构紧凑。最后通过实验进行了测试,并将该采样方法运用到实际某型号探地雷达中,进行了实际的野外试验验证,其探测效果良好,为工程化应用提供了良好的基础。

[1] Assessment of Ultra-WideBand (UWB) Technology[C]. OSD/DARPA, Ultra-WideBand Radar Review Panel, R-6280, Office of the Secretary of Defence. Defense Advanced Research Projects Agency, 1990.

[2] 严明, 田茂, 甘露, 等. 冲击型探地雷达回波信号的等效采样方法研究[J]. 武汉大学学报, 2007, 32(4): 373-375.

Yan Ming, Tian Mao, Gan Lu,.. Equivalent sampling method for echo signal of impulse ground penetrating radar[J]., 2007, 32(4): 373-375.

[3] 张康, 周斌, 方广有. 无载频脉冲探地雷达主控系统小型化设计[J]. 微计算机信息, 2007, 23(35): 211-213.

Zhang Kang, Zhou Bin, and Fang Guang-you. Miniaturized design of impulse ground penetrating radar host control system[J]., 2007, 23(35): 211-213.

[4] Walt Kester. ADC Architectures III: Sigma-Delta ADC Basics. Analog Devices Inc., 2008: 1-10.

[5] Wu Jingyuan, Hansen Sten, and Shi Zonghan. ADC and TDC implemented using FPGA[C]. 2007 IEEE Nuclear Science Symposium Conference Record, Honolulu, Hawai, Nov. 2007: 281-286.

[6] Borislav Gueorguiev Tomov and Jøgen Arendt Jensen. Compact FPGA-based beamformer using oversampled 1-bit A/D converters[J]., 2005, 52(5): 870-880.

[7] 叶盛波, 周斌, 方广有. 新型探地雷达内同步接收机设计[J].仪器仪表学报, 2010, 31(10): 2364-2367.

Ye Sheng-bo, Zhou Bin, and Fang Guang-you. Research of a internal synchronous ground penetrating radar receiver[J]., 2010, 31(10): 2364- 2367.

[8] Khoini-Poorfard R, Lim L B, and Johns D A. Time- interleaved oversampling A/D converters: theory and practice[J], 1997, 44(8): 634-645.

[9] 黄争. 基于时间交替采样结构的高速ADC系统[D]. [硕士论文], 电子科技大学, 2007: 4-7.

Huang Zheng. High speed ADC system based on time- interleaved sampling[D]. [Master dissertation], University of Electronic Science and Technology of China, 2007: 4-7.

[10] Xilinx Inc. Virtex II FPGA Family: Complete Data Sheet. DS031, 2007: 2-7.

[11] Xilinx Inc. 1:7 Deserialization in Spartan-3E/3A FPGAs at Speed Up to 666 Mbps. Xapp485, 2008: 2-10.

[12] 叶盛波, 周斌, 方广有. 新型超宽带探地雷达数字采样接收机设计[J]. 电波科学学报, 2011, 26(4): 783-787.

Ye Sheng-bo, Zhou Bin, and Fang Guang-you. Design of a new Wideband digital sampling receiver for ground peneterating radar[J]., 2011, 26(4): 783-787.

[13] Mätzler C and Wegmüller U. Dielectric properties of fresh- water ice at microwave frequencies[J]., 1988, 21(11): 1660.

[14] Matsuoka T, Fujita S, and Mae S. Effect of temperature on dielectric properties of ice in the range 5~39 GHz[J]., 1996, 80(10): 5884-5890.

Method and Implementation of High-speed Digital Sampling Technology Based on Impulse Radar Signal

Shen Shao-xiangYe Sheng-boFang Guang-you

(Key Laboratory of Electromagnetic Radiation and Detection Technology, the Institute of Electronics, Chinese Academy of Sciences, Beijing 100190, China)(Graduate University of the Chinese Academy of Sciences, Beijing 100049, China)

A High-speed digital sampling technology suitable for periodical impulse radar signal is proposed in this paper. One bit high-speed quantize is constructed by differential comparator in FPGA. Time-interleaved digital sampling and buffer encoding are used to one bit stream based on the internal multi-phase clock of FPGA, to achieve sampling rate higher than 1 GHz. High speed digital sampling is realized by the accumulation of one bit sampling data with different comparison levels. An 8 bit, 1.6 GHz ADC based on the proposed method is realized on XC2V3000 Xilinx’s FPGA, which is successfully applied in GPR. The proposed method has the advantages of low cost and power consumption as compared with real sampling, and exhibits higher efficiency as compared with equivalent sampling.

FPGA; Digital sampling; One bit quantize; Compare level

TN958.4

A

2095-283X(2012)02-0136-07

10.3724/SP.J.1300.2012.20022

2012-04-11收到,2012-05-18改回;2012-06-05网络优先出版

国家自然科学基金(40976114)和国家863项目(2008AA121702)资助课题

沈绍祥 sxshen@mail.ie.ac.cn

沈绍祥(1977-),男,安徽人,2005年于中国矿业大学(北京)获硕士学位,现为中国科学院电子学研究所助研,在读博士生,专业方向为电磁场与微波技术,主要从事超宽带探地雷达系统设计及应用研究。

E-mail: sxshen@mail.ie.ac.cn

叶盛波(1983-),男,湖北人,2006年于武汉理工大学获学士学位,2011年于中国科学院电子学研究所获博士学位,助研,主要研究方向为超宽带探地雷达系统设计及雷达信号处理。

E-mail: shengboye@163.com

方广有(1963-),男,河南人,中国科学院电子学研究所研究员,博士生导师,主要研究领域为超宽带电磁学及工程应用,损耗介质中隐蔽目标的电磁探测,微波成像新技术与新方法,电磁场的数值计算方法等。

E-mail: gyfang@mail.ie.ac.cn