高速大容量存储系统的应用设计

2012-06-22胡世明康怀祺滕云龙

胡世明 康怀祺 滕云龙

(电子科技大学 成都 610054)

1 引言

随着中国航空电子技术和雷达成像技术的快速发展,合成孔径雷达的分辨率和采样率大幅提升,由此产生的高速大容量数据需要实时快速的保存以方便后续分析处理。同时由于航空平台的限制,对存储设备的可靠性和抗振动特性以及体积,重量也有严格的要求,因此存储电路通常采用非易失的电路芯片构成,而传统的机械硬盘,DOC,E2PROM等存储技术由于各自的缺点已经不适用对高速大容量数据的存储[1,2]。近年来,快速发展的闪速存储器(FLASH MEMORY)以其抗振动、读写速度快、存储密度大、可擦除、非易失、低成本、环境适应能力强以及命令、地址、数据线复用和接口便利等特点,得到了广泛的应用,成为大容量数据存储系统首选器件。

然而伴随着数据存储系统容量要求越来越大,存储速度要求越来越高,同时由于NAND FLASH的控制逻辑比较复杂,对时序要求十分严格,而且更重要的是闪存芯片中允许存在一定的无效块,需要对其进行无效块管理。所以针对上述要求及问题,数据存储系统需要一个控制器。如今,大规模集成电路和高性能FPGA的飞速发展,可以采用FPGA作为高速大容量存储系统的核心控制器,在FPGA上实现存储系统要求的所有控制功能。基于上述原因,设计了以FPGA Virtex-4系列芯片为核心控制芯片,以三星公司K9HCG08U1M闪存芯片为存储介质的高速大容量存储系统。

2 大容量存储系统介绍及硬件结构

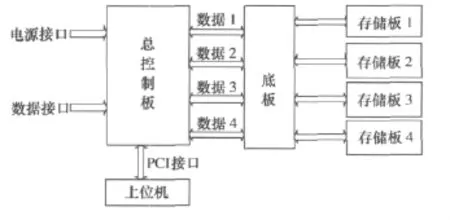

本存储系统包含四块存储板卡,一块控制板卡,在结构上均采用了基于CompactPCI总线的6U标准板型。每块存储板卡上共载有96片 Nand型FLASH,Nand FLASH存储芯片采用三星公司的K9HCG08U1M型芯片,从而可以实现单板768GB的存储容量。四块存储板卡可以实现3TB的总存储容量。这其中,单块存储板卡的96片闪存芯片分为4组,由两块FPGA Virtex-4芯片控制,每个组中,采用3级流水线操作,每级流水线由8片闪存芯片并行构成基本的存储模块。控制板卡核心为一片Virtex-4系列的FPGA芯片,负责对四块存储板卡进行数据分路,同时负责存储系统与主机的通信。图1为该存储系统结构图。

图1 系统结构图

3 系统存储关键技术

由于NAND型FLASH芯片本身存在写入带宽低,写入速度慢,而且存在无效块的缺点,因此必须设计合理有效的控制逻辑来克服这些缺点。针对写入带宽低和写入速度慢的缺点,可以通过采用并行总线操作和流水线操作的方法来增加带宽;针对无效块的问题,可以通过建立无效块管理表,将无效快地址加入到无效块管理表中,从而在写入或读出数据,以及对NAND FLASH进行擦除操作时,避免对无效快的操作。

3.1 并行总线操作[3]

并行总线操作的本质是通过拓宽数据总线的带宽来实现数据宏观上的并行操作。并行操作可以按照需要将多片闪存芯片的数据线结合起来共同使用,以此来提高系统读写带宽,从而提高读写效率。在并行系统中,可以将多片闪存芯片看作一个模块,把这个模块作为整个存储系统中的基本数据存储单元,所有操作都是面向这些基本模块来进行的。

本存储板卡中,8片K9HCG08U1M型闪存芯片构成一个64位带宽的存储子模块,如图2所示,它们共用相同的控制信号,包括片选信号,读写信号,芯片内部地址等,采用一驱八的形式由FPGA提供。由于R/B信号采用集电极开路输出,可以采用线与。所以将八片闪存芯片的R/B信号连在一起并通过一个电阻上拉至电源。这样,数据量将是使用单独一块芯片时的8倍,理论上速度也是非并行时的8倍。

图2 FPGA与NAND FLASH接口示意图

3.2 流水线操作

以K9HCG08U1M型闪存芯片为例,在进行写编程操作时,假设写入时钟为30MHz,以编程一页写操作为例,命令、地址以及数据加载所需时间大约为133μs,而闪存芯片自动编程所需时间典型值为800μs,而在进行擦除操作时,当擦除一个块时,芯片自动编程所需时间典型值更是达到了1500μs,远大于命令和地址加载时间。由此得知,自动编程耗费了大量的时间,影响了闪存芯片操作速度。因此,借鉴现今高性能计算机中的流水线操作原理,可在时间片上实现微观并行。流水线运行起来后,在任意时间片上总有若干小操作在同时进行,即在时间上实现复用。因此从总体上看,操作速度将会提高。图3为闪存芯片流水操作示意图[4]。

图3 流水线操作示意图

3.3 无效块管理

NAND型FLASH存储器在出厂时就存在一些初始无效块,并且在使用过程中也会出现存储单元的损坏。因此有必要在对闪存芯片进行写、读以及擦除操作前,对闪存芯片进行读无效块操作,记录闪存芯片的无效块地址,从而避免对无效块的操作,保证数据能够被正确的存储和读取。为了避免对无效块的操作,在FLASH的使用过程中,出现了各种无效块处理方法。目前主要有:a.建立无效块屏蔽函数来避免对无效块的操作。b.基于FAT文件系统处理无效块。上述方法都有各自的优缺点[5]。

本方法中,直接在FPGA内部开辟了专门的存储单元用于存储闪存芯片的无效块地址,工作时在进行其他操作之前,先进行读无效块操作,将闪存芯片的无效块地址存入FPGA内的存储单元中,每次在进行写入、读取以及擦除操作时,避免对闪存芯片无效块的操作,达到对无效块管理的目的。需要指出的是,存储无效块地址信息的存储单元是在FPGA内开辟的,每次掉电之后存储信息都会丢失,所以每次系统上电之后,在对芯片进行其他操作之前都会先进行检查无效块操作,因此本无效块管理方法是一种动态管理。

总之,本无效块管理方法实质是将芯片出厂时的无效块进行屏蔽,从而避免对这些无效块的操作,达到无效块管理的目的。

4 软件设计与验证

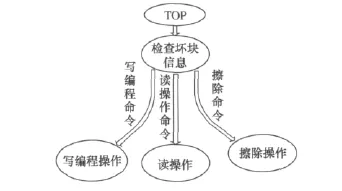

本设计方法中,主要包括4个功能模块和一个顶层模块,4个功能模块包括:写编程操作模块,读操作模块,擦除操作模块以及读无效块模块,这些模块都用Verilog程序语言进行编写。顶层模块先调用读无效块模块,将无效块信息存入FPGA内专门的存储单元,然后根据输入的指令来决定具体执行那项操作。

图4 程序执行框图

4.1 检查无效块操作

三星公司规定K9HCG08U1M芯片无效块信息标记在每个块的最后一页的空闲区的第一个字节,读出全为FFh时为有效块,为非FFh时为无效块[6]。在本方法中,由于8片芯片并行操作,所以读出为64位的十六进制信息,当其中有任意一位十六进制数为非F时,则认为为无效块,将无效块地址信息存入FPGA内专门开辟的存储单元中。由于是8片芯片的并行操作,当其中有一片的块信息为无效块信息时,则认为其余的7片芯片的相同地址的块也为无效块,这必然会造成对存储空间的浪费。经计算,单板浪费的存储空间大约为18GB,四块存储板总共浪费72GB的存储空间,对本存储系统要求的2.5T的存储空间来说这样的存储空间浪费是可以接受的。

图5 检测无效块局部观测图

图6 检测无效块时序命令图

图5 为对存储板进行无效块检测的观测图,图6为无效块检测时序放大图。从图中可看出,块标志信息在RE信号的上升沿从FLASH芯片中读出,为FFFFFFFFFFFFFFFFh,表明检测的8片 FLASH芯片的块为有效块。如读出的块标志信息为非FFFFFFFFFFFFFFFFh,则该块的地址信息将存入FPGA内的无效块地址存储单元中。以此顺序检测,从而完成无效块检测操作。

4.2 擦除操作

由于FLASH芯片的擦除自动编程操作所需的时间较长,则在进行擦除操作的时候同样采用流水线技术,如在第一组FLASH芯片的第一级8片芯片自动编程时,可对第二级以及第三级芯片甚至第二组的三级FLASH芯片进行加载擦除命令操作,从而可以节省时间,达到快速擦除的目的。

需要注意的是,在进行擦除操作时,也会将NAND FLASH芯片出厂时的无效块标记信息同时擦除,所以在擦除操作进行之前,也要先进行读无效块操作,将无效块地址记录,从而在擦除操作的时候避免了对无效块的擦除操作,只对有效块进行擦除操作。

4.3 写编程操作

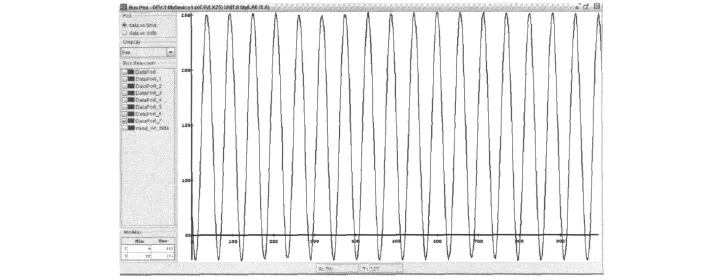

在进行写编程操作时,当加载完命令和地址后,FLASH芯片进入自动编程,自动编程时间典型值为800μs,最大值为3ms,即芯片自动编程时间不确定,有的芯片编程时间可能小于800μs,有的芯片编程时间就是典型值,而其他芯片的编程时间可能需要3ms。而且在本存储系统中,由于采用8片芯片并行结构以及流水线操作,所以写操作自动编程时间为8片芯片中的最大值,同时在写编程的流水线操作时,每级的芯片自动编程时间也不一样。所以在进行流水线操作时,流水级数应尽量大。如果流水级数太少,就有可能出现命令加载完后所有的流水级都进入自动编程时间,而这时外部还在源源不断的向存储系统发送待存储的数据,就会造成存储数据的丢失。图7所示为写入存储板的正弦信号的Bus Plot观测结果。

图7 待写入的正弦信号

4.4 读操作

在进行读操作时,为了使读出的数据与存储的数据保持一致,即保持数据的连续性,应该按照写入数据的次序依次读出数据,达到保持数据连续性的目的。

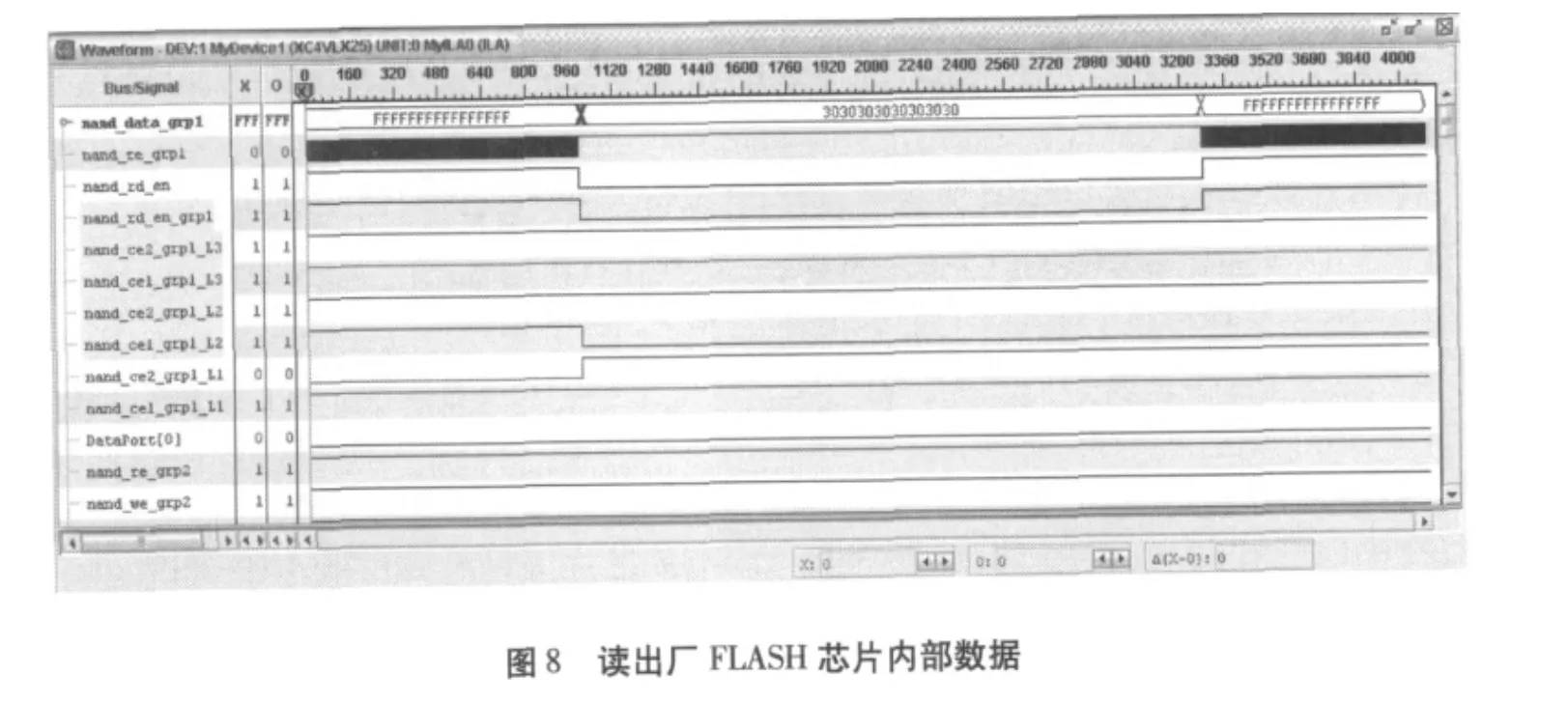

图8所示为利用ChipScope软件对FLASH芯片出厂时的数据进行读操作观察时的部分观测结果,由于芯片在出厂时,其内的数据全被置为1,所以从读出的芯片数据也得以验证。并且在读数的过程中,数据正确率达到了100%,这也充分说明无效块检测操作已经将出厂无效块全部检测到并对这些无效块进行了屏蔽。

图9所示为对存储板写入正弦信号的数据进行读操作的Bus Plot观测结果。由于存储板上的存储芯片为8片FLASH芯片并行结构,所以数据位为64bit。对每8bit加载总线,得出8路信号,由图得知,读出的信号与写入的信号完全一致,说明数据能够被正确的写入,正确的存储,也能够被正确的读出。

5 结束语

本文所介绍的高速大容量存储系统,存储速度高,存储速率理论可达320MB/s。存储容量大,除去无效块影响,总容量可达到2.5TB。在测试过程中各项性能指标都达到了合成孔径雷达成像试验所需的要求。此外,该存储系统只需对系统硬件电路稍做改动,就可支持更大容量的闪存芯片以扩充存储容量。同时,该存储系统具有一定通用性,可以应用于其他需要高速大容量数据存储的场合,具有很高的工程应用价值。

[1]朱知博.基于NAND FLASH的高速大容量存储系统设计 [J].现代电子技术,2011,34(8):170-173.

[2]高怡祯.基于闪存的星载大容量存储器的研制[D].中国科学院研究生院,2004.

[3]雷磊.NAND型FLASH海量存储系统的设计与实现[D].北京:北京理工大学,2008.

[4]刘瑞.基于FLASH的高速图像采集存储系统[D].中国科学技术大学,2009.

[5]张胜勇,高世杰,吴志勇等.基于 FPGA的NAND FLASH坏块处理方法[J].计算机工程,2010,36(6):239-241.

[6]Samsung.K9XXGG08UXM flash memory datasheet rev.13[EB/OL],http://www.sumsung.com,2011.