SpaceWire CODEC的容错设计和实现

2012-04-17程照强刘淑芬

程照强,刘淑芬

(北京控制工程研究所,北京 100190)

SpaceWire[1]是由ESA推出的专门面向航天应用的高速总线,它以IEEE 1355-1995和LVDS标准(ANSI/TIA/EIA-644)为基础,同时在错误处理方面有更好的支持.其基本特点是串行、高速(200Mbit/s)、全双工.SpaceWire CODEC(encoderdecoder)是SpaceWire协议控制器的主要组成部分,主要完成对数据的编码发送和解码接收.SpaceWire CODEC的组成中包含寄存器以及存储器单元,这些单元存储着系统的状态、控制信息、数据等,在空间环境中高能粒子的影响下容易发生单粒子翻转(SEU,single event upset)、单粒子功能中断(SEFI,single event functional interrupt)等,尤其在基于FPGA的实现方式中,这些存储单元更容易受到SEU、SEFI的影响.为了保证产品在轨正常工作,必须对SpaceWire CODEC进行容错设计以减缓SEU、SEFI等单粒子效应的影响.

1 SpaceWire CODEC及容错性能分析

1.1 SpaceWire CODEC 结构

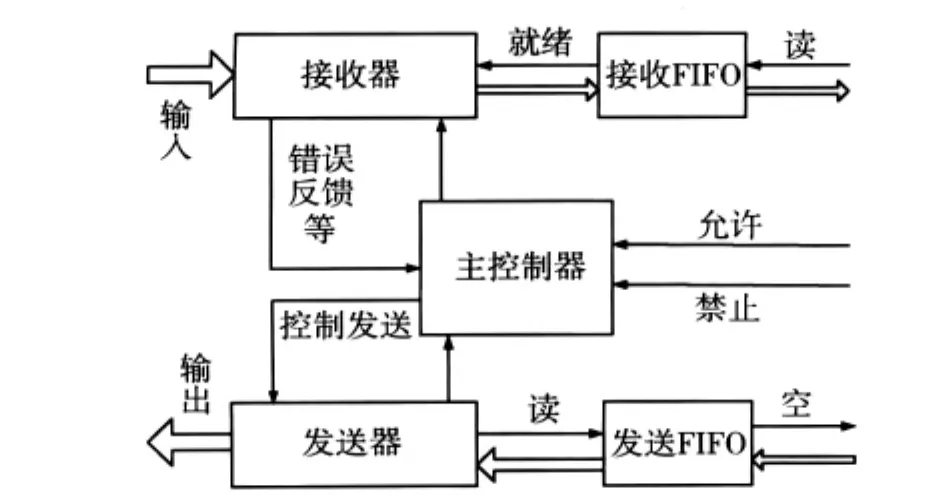

SpaceWire CODEC包括协议中的信号层(不包含其中LVDS接口部分)、字符层、交换层和数据包层.SpaceWire CODEC由发送先进先出数据缓存器(FIFO,first in first out memory)、接收 FIFO、发送器、接收器以及主控制器5部分组成.发送及接收FIFO主要用来实现主机和SpaceWire CODEC的数据交换;发送器则是按照主控制器的要求,对相应的字符进行编码并发送;接收器则主要实现对数据进行解码和错误检测;主控制器主要用来控制数据传输,包括链路控制、错误恢复、控制发送器发送数据以及接收器接收数据等功能.SpaceWire CODEC结构简图如图1所示.

图1 SpaceWire CODEC结构简图Fig.1 Block diagram of SpaceWire CODEC

1.2 SpaceWire容错性能分析

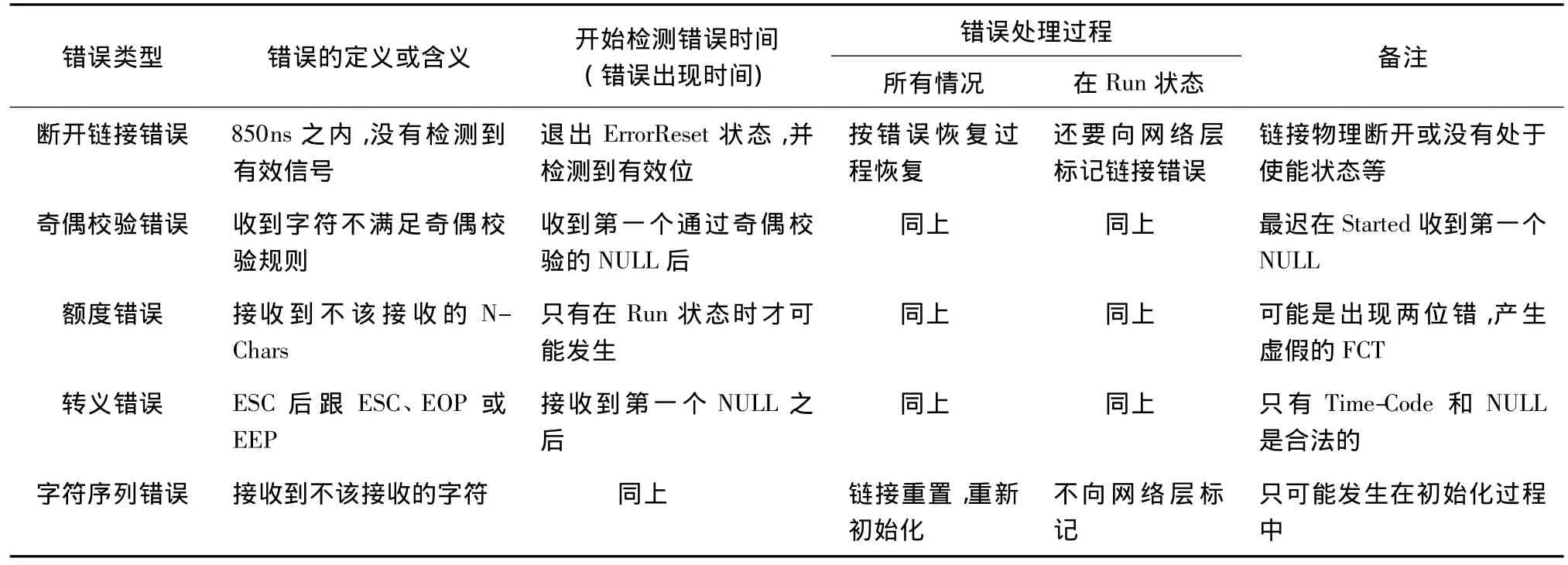

SpaceWire自身提供了一些容错措施,包括:在信号层中采用DS(Data-Strobe)编码,该编码可以很好地消除时钟偏移,减小或者补偿数据偏移;在字符层增加奇偶校验位(每10位数据至少有1位奇偶校验位),通过信息冗余来提高数据传输的可靠性;在数据包层,通过正常数据包结束符(EOP,normal end of packet)和错误数据包结束符(EEP,error end of packet)来区分正确的数据包以及错误的数据包;在交换层能够检测到的错误以及这些错误的处理方法如表1所述,交换层是实现SpaceWire错误检测和恢复的主要协议层;在网络层中,采用自适应群组路由(GAR,group adaptive routing),其目的之一是实现冗余路由、冗余链接,当到达目标节点的某条链接出现故障时,可以通过网络中的其他链接到达目标节点,从而提高网络的容错能力.

表1 中,ErrorReset、Started、Run 是SpaceWire主状态机的三个状态,Time-Code、FCT(flow control token)、ESC(Escape)、EEP、EOP、NULL 则 是SpaceWire中规定的字符,N-Chars(Normal-Characters)指EEP、EOP和数据字符.表1中的错误恢复过程是基于端到端的SpaceWire链接来实现的.具体的恢复过程以A、B两个端点之间的链接为例:当A端主控制器的状态寄存器跳转到一个非法的状态(如发生SEU,A端检测到错误的情况类似)时,A端主控制器将控制A端发送器停止发送任何数据,链接B端的接收器在850ns内接收不到任何有效的数据,将产生一个断开链接错误,并将此错误通知给B端的主控制器,B端主控制器在接收到断开链接错误后,控制B端发送器停止发送任何数据,这将在A端造成一个链接断开错误,至此,A、B两端之间的链接完全断开,并重新开始建立链接,如果建立链接条件不成立,那么A、B两端将一直尝试建立链接,直到A、B两端非使能(停止建立链接)或建立链接的条件成立;如果建立链接条件成立,链接重新建立,恢复数据传输,A、B之间的链接完成一个错误恢复过程.B端检测到错误的情况和A端类似.此外,当A、B之间的链接出现故障时,可以通过路由、冗余的链接找到从A到B进行数据传输的其他链接.

SpaceWire没有规定SpaceWire CODEC内部的容错能力,其发送/接收FIFO本身不具有任何错误检测、恢复的能力;发送器对数据进行发送时,增加奇偶校验位,提高数据传输的可靠性;接收器具有较强的检错能力,可以检测到表1中的各种错误,将错误信息传递给主控制器.主控制器通过控制链接来实现错误恢复.

SpaceWire的容错能力体现在基于端到端的链接,SpaceWire CODEC具有一定的错误检测能力,但这不足以保证在恶劣的空间环境中实现可靠的数据传输,具体表现在以下几个方面:

①SpaceWire CODEC仅在发送数据时增加奇偶校验位,在发送/接收FIFO中,没有任何保证数据可靠性的措施.FIFO作为SpaceWire CODEC和主机之间的缓冲区,用来存储待发送/接收到的数据、命令、控制信息,是容易受SEU、SEFI影响的部分,不采取容错措施有可能导致发送/接收到的数据、命令发生错误并造成严重的后果;

②SpaceWire CODEC的容错策略侧重在检测到错误后,采用基于端到端的错误恢复机制实现错误恢复,而不是SpaceWire CODEC自身来纠正检测到的错误,在空间环境中SpaceWire CODEC的实现载体如果受到空间辐射的影响,将影响系统的可靠性;

③SpaceWire基于端到端的错误恢复机制,并非能纠正检测到的所有错误;当SpaceWire CODEC中的一些寄存器,如寄存器中的[Linkable]位(链接建立使能位)发生了翻转,只能通过对寄存器中的[Linkable]位进行重新设置,否则链接将无法建立;

④SpaceWire CODEC这种基于链接的错误检测、恢复方法需要占用网络的时间资源和带宽资源.以错误恢复时间为20μs、传输速率为100Mbit/s计算,那么在链接恢复的过程至少有2000bit的数据无法处理,这不仅会造成链接阻塞,影响数据的正常传输,对系统的实时性也将产生影响.

根据以上分析,为适应恶劣的空间环境,有必要对SpaceWire CODEC中的FIFO、状态机、寄存器等容易受SEU、SEFI影响的部分进行容错设计.

表1 交换层出错类型以及处理方法Tab.1 Error types and their handling ways in exchange level

2 SpaceWire CODEC的容错设计

2.1 FIFO的容错设计

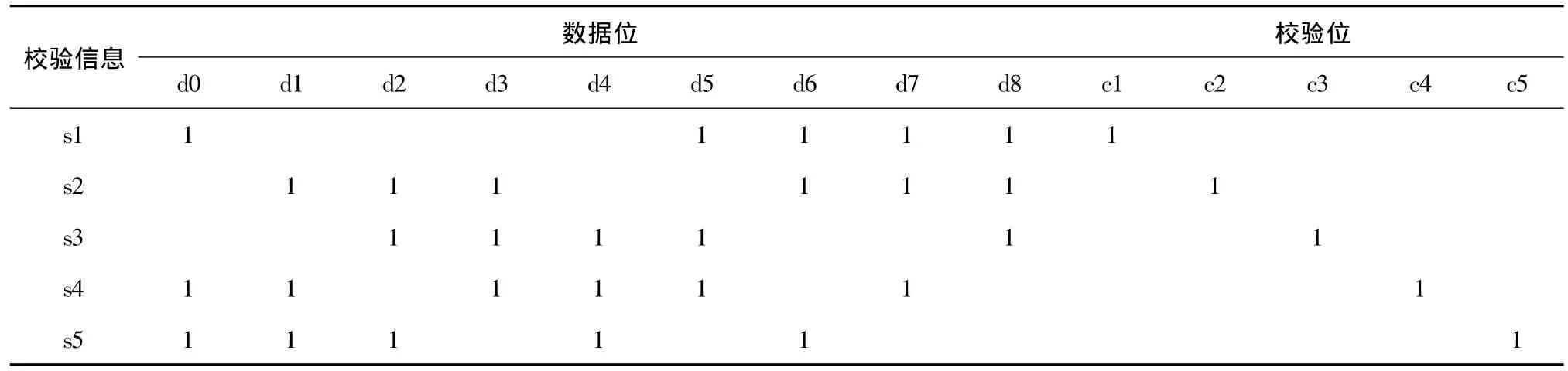

FIFO作为CODEC和主机之间的缓冲单元,需要存储的数据包括8位数据和1位控制信息标志位.检错纠错(EDAC,error detect and correct)是FIFO的有效容错设计方法.

本文通过实现Hsiao[2-3]编码,使FIFO具有纠一检二的能力.与扩展Hamming编码相比,Hsiao编码具有以下优点:①编解码速度快,校验矩阵中每行“1”的个数相等,这说明用于产生每位校验位的电路延时几乎相等,不仅速度快,而且便于优化;②电路面积小,校验矩阵中的“1”表示硬件电路中参与XOR运算的相关数据位,Hsiao编码中所用到的XOR比扩展Hamming编码的要少,这不仅能减小面积,同时能降低功耗;③Hsiao编码4位错误的检测概率高于扩展Hamming编码.

Hsiao编码最重要的是校验矩阵即H矩阵的构造,H矩阵应满足:

①每列中有奇数个“1”,无相同列;

②每行中“1”的个数尽可能相等;

③“1”的总个数尽可能少.

上述条件保证了编码的最小距离是4,可实现纠一检二,但是校验矩阵却不唯一.以本文中的FIFO为例,(14,9)分组码的H矩阵有C(10,9)=10种选择,不同的矩阵对电路的性能影响是不同的,目前尚无有效的选择算法,本文选择了表2所示的校验矩阵.

当出现两位数据错误时,具体的处理方法如下:将错误信号返回给更高层,同时将数据中的原有数据直接输出.这样的考虑是基于:①检测到两位错误,这两位错误并非一定出现在有效数据位,也有可能在校验位出错,甚至出错的两位都在校验位;②传输层、应用层如果也采取相应的措施,完全有可能纠正此错误;③可以由应用层根据数据的不同应用来决定如何处理.

表2 Hsiao码校验矩阵Tab.2 Check matrix of Hsiao coding

采用Hsiao编码使FIFO具有纠一检二的能力,实现EDAC后FIFO的结构如图2所示.

2.2 主控制器状态机容错设计

SpaceWire主控制器状态机(FSM,finite state machine)是SpaceWire CODEC电路中的重要组成部分,主要用来完成链接建立、链路维护、链路控制以及错误处理等,其容错能力、可靠性直接影响到总线的正常工作.

SpaceWire主控制器状态机包括ErrorReset、ErrorWait、Ready、Started、Connecting、Run 6 个状态,除了在链接建立过程中要经过ErrorReset、ErrorWait、Ready、Started、Connecting这 5 个状态之外,一旦链接建立,其状态机的状态将一直保持Run状态,直到链接终止或者出现错误.

图2 带有检错纠错功能的FIFO结构图Fig.2 Block diagram of FIFO with EDAC

对正常运行的SpaceWire网络来说,几乎所有接口的主状态机都运行在Run状态.为保证数据的可靠传输,状态机处在Run状态时要采取更加有效的容错设计方法,同时增强在其他状态时的检错能力,借助SpaceWire自身的错误恢复能力实现错误恢复.本文对主控制器状态机采用下列方案进行容错设计:

①状态机采用 One-Hot编码[4],可有效地提高电路的速度和可靠性;

②One-Hot编码正常状态只有一个触发器的状态为1,其余态皆为0,根据这个特点,对当前状态机寄存器增加奇偶判断,来有效地检测合法状态到非法状态之间的转化;

③增加一个前态寄存器,在主状态机的转换关系中,任何状态到达ErrorReset都是合法的;除了Error-Reset状态之外,其他任何状态只能由一个状态转换而来;在到达当前状态时,首先判断前一个状态是否对应,以此来防止合法状态之间的非法转化(如ErrorWait跳转到Started就是一个非法的转化);

④设置rflag标志,在到达Run状态时,对当前的状态寄存器采取刷新的策略,保证状态机在Run状态时,有更高的可靠性.同时对rflag标志位进行刷新,防止错误的积累而导致rflag判断出错.

本文对主状态机采用 One-Hot编码、带有EDAC功能的二进制编码[5]以及本文所采用的方法进行对比(仅对主控制器进行综合),如表3所示.

由表3可知,状态机采用EDAC编码,增加了额外的解码电路、编码电路,因而需要较多的逻辑资源,对频率会产生影响;One-Hot编码需要较多的触发器资源,逻辑资源则相对较少;本文采用的方法资源开销较小,并可以达到较高的频率.

表3 主控制器状态机3种不同设计方法对比Tab.3 Comparison of three different design methods for master controller FSM

2.3 寄存器的容错设计

寄存器作为SpaceWire CODEC的重要组成单元,其中暂存着协议执行过程中的重要数据,它的可靠性至关重要.由于设计中的寄存器分布比较分散,不适合采用冗余编码方案,因此本文对SpaceWire CODEC中所有寄存器采用空时三模冗余(ST-TMR,space-time triple modular redundancy)[6]设计.

图3 空时三模冗余结构示意图Fig.3 Block diagram of ST-TMR

采用ST-TMR不仅可以防止单一寄存器发生SEU而导致数据失效,同时由于ST-TMR采用了硬件冗余和时间冗余相结合的技术,寄存器前一级的组合逻辑上的单粒子瞬时干扰(SET,single event transient)也可以被滤除.ST-TMR能够有效减轻组合逻辑的SET和时序逻辑的SEU.如图3所示,STTMR容错方法通过在组合逻辑的下一级时序逻辑上使用带延迟的多级时钟,可以在不同时刻采样组合逻辑的输出,利用该时间差,滤除组合逻辑有可能发生的SET.

实现ST-TMR首先是要生成带有时延的时钟.在FPGA中可以通过插入buffer来实现,本文采用xc4vlx200型FPGA中的BUFIO缓冲单元来实现,延时约为 380ps.实现两级延时为 760ps.当采用100MHz的时钟频率时,这一延时为时钟周期的7.6%,对时序的影响较小,当采用的时钟频率更高时,影响将加大.

3 验证与测试

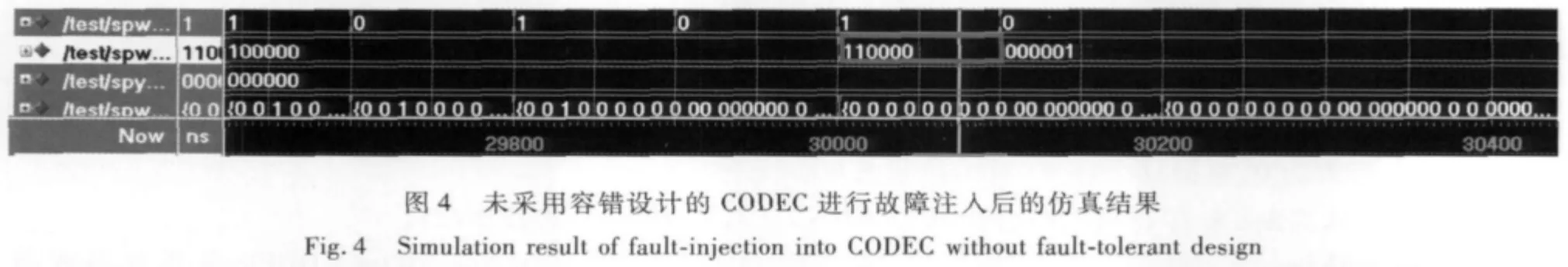

在Modelsim6.2g下,通过对寄存器、信号进行强制赋值来实现对SpaceWire CODEC中寄存器的故障注入;在TestBench中,通过一个故障注入的进程来实现对某些信号的强制赋值,在30001ns时,强制将状态寄存器的状态更改为一个非法的状态“110000”,持续时间为100ns.分别对容错设计前后的CODEC注入故障,可以看到在图4中,由于注入故障,导致状态寄存器直接回到 ErrorReset(“000001”)状态,链接断开;在图5中注入同样的故障,在故障结束后,状态寄存器仍然在 Run(“100000”)状态,链接并没有受到故障的影响,仍然进行正常的数据传输.在对数据进行EDAC编码后、写入FIFO之前以及在从FIFO中读出数据进行EDAC解码之前,随机的注入一位、两位故障来实现对FIFO的故障注入.故障注入的结果表明,容错设计能有效地屏蔽注入的故障.

采用容错设计的SpaceWire CODEC在Vitrex-4系列开发板上实现,其物理测试链接示意图如图6所示.通过和SpaceWire标准接口建立链接,能够正确地发送、接收各种字符以及断开链接后恢复链接.验证结果表明采用容错设计后的SpaceWire CODEC功能正确.

图6 SpaceWire物理测试链接示意图Fig.6 Interconnection of SpaceWire test

4 结论

容错设计是提高产品可靠性的有效途径,产品设计过程中需要在各个环节采取容错措施.本文分析了SpaceWire协议的容错性能,并对 SpaceWire CODEC的容错设计方法及验证情况进行了介绍.通过对SpaceWire CODEC中的FIFO、状态机和寄存器进行相应的容错设计,从整体上提高了SpaceWire CODEC的容错能力.仿真结果表明容错设计有效,测试结果表明容错设计的SpaceWire CODEC功能正确.

[1 ] Steve P.Space engineering spacewire-links,nodes,routers and networks[S].ESA-ESTEC ,2008

[2] Hsiao M Y.A class of optimal minimum odd-weight-column SEC-DED codes[J].IBM Journal of R & D,1970,14:395-401

[3] Ghosh S,Basu S,Touba N A.Reducing power consumption in memory ECC checkers[C].IEEE International Test Conference,Charlotte,Oct 26-28,2004

[4] Kumar N.Automated FSM error correction for single event upsets[C].Military and Aerospace Programmable Logic Devices International Conference,Washington D.C,2004

[5] Shailesh N.A comparison of fault-tolerant state machine architecture for space-borne electronics[J].IEEE Transactions on Reliability,1996,45(1):109-113

[6] Chen W,Gong R.Two new space-time triple modular redundancy techniques for improving fault tolerance of computer systems[C].The 6thIEEE International Conference on Computer and Information Technology,Washington D C,Sep.2006