一种DVB-S2中低复杂度的LDPC编译码研究

2012-02-23尹爽爽王中训

尹爽爽,王中训

(烟台大学光电信息科学技术学院,山东烟台 264005)

0 引言

国际数字视频广播(digital video broadcasting,DVB)组织从2002年初启动 DVB-S(digital video broadcasting standard)的升级工作,2004年正式公布了 EN302 207 号文本(草案),即 DVB-S2(second gen-eration satellite digital video broadcasting standard)标准,正式采纳低密度奇偶校验码(low density parity check codes,LDPC)码和 BCH(bose chaudhuri hocquenghem)码的级联码作为其前向纠错码方案。DVB-S2标准可以被认为是当前DVB-S标准的继承者,该标准的纠错码使用BCH码作外码,LDPC码作内码的级联码以替代DVB-S标准使用的里德所罗门码和卷积码级联的编码方法[1]。LDPC码是由Gallager于1962年提出的一类具有稀疏奇偶校验矩阵的线性分组码[2],由于当时硬件条件的限制并未得到很好的发展,1995年MacKay和Neal重新发现并证明了迭代译码的LDPC码具有渐进香农限的性能[3],LDPC码以逼近Shannon极限的误码率性能和可完全并行实现迭代译码的特点,成为纠错码研究的热点。为了提供灵活性,DVB-S2标准中的LDPC码有64 800 bit和16 200 bit两种码长的码,并对长码和短码分别规定了11种和10种码率。如此大的码字长度使通信性能距香农限约0.7 dB,在系统效率方面比DVB-S高出30%。

LDPC译码是一个迭代过程,每次迭代中庞大的数据处理量、存储量和互联要求对译码器实现是一个巨大的挑战,因此为实现这些码的出色性能,要求对硬件实现问题进行调查研究。本文着重从硬件实现的角度考虑,首先采用了低存储量和低复杂度的码字构造方法对DVB-S2中LDPC码进行了编码,进而用类似的方法推导出了校验矩阵,然后采用降低复杂度的最小和译码算法在Matlab环境下对不同码率的LDPC码的性能进行了仿真对比,重点研究了译码算法中采用的不同的量化比特数和迭代次数对译码性能的影响,利用应用知识极大地简化了面向低实现复杂度的高层次设计。

1 DVB-S2中LDPC

1.1 DVB-S2中LDPC的编码

DVB-S2标准下的信道编码包括两种级联码,外部的BCH码把长度为k1比特的二进制信息编码为长度为k比特的码字,k比特的码字然后被编码成n比特长度的LDPC码,n等于64 800 bit或16 200 bit,分别称为普通帧(码长为64 800 bit)和短帧(码长为16 200 bit)。表1和表2分别给出了普通帧和短帧的不同码率(短帧中的码率需要校正)下的参数[4]。

表1 DVB-S2中普通帧的参数Tab.1 Parameters of normal frames in DVB-S2

表2 DVB-S2中短帧的参数Tab.2 Parameters of short frames in DVB-S2

DVB-S2标准下,LDPC码编码规则的主要思想是根据标准中的地址表由信息位推导出校验位,然后信息位在前,校验位在后组合为码字,有如下步骤。

1 )校验位初始化为零。

2 )计算奇偶校验位。

(1)式中:pj为检验节点;im为变量节点。

由第m个信息位im导出第j个校验位pj,j=(x+q(m mod360))mod(nldpc-kldpc),nldpc和kldpc分别表示码字长度和信息位长度;x表示第x个周期为360的循环,对应 DVB-S2标准附录 B 和 C[1]相应地址表的第x行的值;q的计算公式为

由于LDPC码具有循环结构,因此极大程度地降低了编译码复杂度[5],另外还可以看出每个子矩阵只需存储第一行地址,其他行可以由第一行导出,降低了存储量,因而降低了硬件实现复杂度。

3)计算最终的奇偶校验位。

1.2 校验矩阵的构造

DVB-S2中使用的LDPC码被称为扩展非规则重复累积(eIRA)码[6],其校验矩阵有如下形式

H= [H1H2](4)(4)式中:H1大小为m×k;HT1矩阵中1的位置与标准附录B和C相应的地址表对应[7],可由编码规则的第二步的方法生成;H2是双对角线矩阵,大小为m×m,其形式为

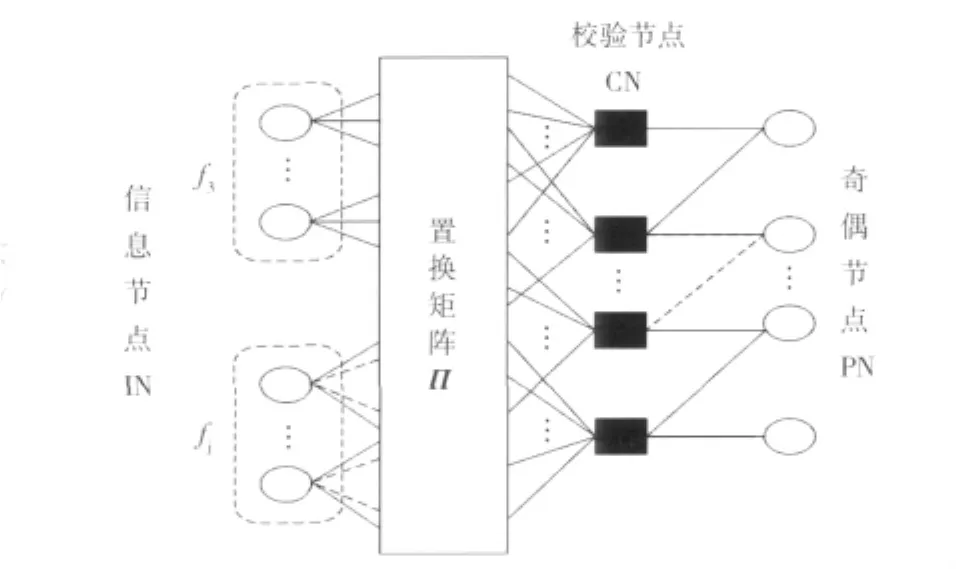

校验矩阵对应的Tanner图如图1所示。

图1 DVB-S2中LDPC码的 Tanner图Fig.1 Tanner Graph of DVB-S2 LDPC

2 降低复杂度的DVB-S2 LDPC码

由于浮点运算慢,在硬件中占用资源多,难以进行硬件实现,因此常使用定点来代替浮点表示。针对浮点域的译码算法难以进行硬件实现,有人提出用图形处理器(graphic processing units,GPU)进行并行译码,这种方法可以取得较高的精度,但缺点是GPU只适合简单的计算,不能使用对数域上的译码算法。本文研究的是译码器的量化,硬件实现以有限精度进行数据的处理而不是无限精度。最有效的实现是在硬件复杂度、译码性能和数据处理速度三方面的一个折衷。

2.1 量化

量化的主要目标是找到一个定点表示模型,即在性能衰减的可接受范围内用尽可能小的所有位宽度。在硬件实现中,降低数据通路的位宽,控制复杂度和存储器的大小,就能够降低功耗和提高数据处理的速度。译码器输入数据的量化和对译码迭代中间变量的量化对控制复杂度有直接的影响,它们直接决定数据通路的位宽和存储器的大小。量化所用的位宽越小,译码器在速度和低功耗等方面的性能越好。量化还对译码性能有直接的影响,因此,在实现的复杂度方面需要考虑的一个关键问题是量化的优化。

2.2 降低复杂度的译码算法

基于置信传播(belief propagation,BP)的迭代译码算法常被用来对LDPC进行译码。实际中通常采用对数域的LLR-BP译码算法,其中校验节点更新公式[8]为

由于上述算法中的非线性函数在硬件中实现复杂,因此提出了最小和算法,该算法虽然性能略有损失,但只需要异或运算和取最小值的比较运算,降低了硬件使用资源[9]。该算法的校验节点的更新简化为

归一化最小和算法是在上式的基础上乘以系数α(小于1),会对某些码长和码率的性能起到改善作用,但乘以α与否和α取多大值要在具体条件下进行仿真实验比较得出结论。

在硬件实现阶段之前,需要对最大迭代次数进行研究以决定将要实施的译码器在迭代过程中所需要的足够的迭代次数。显然,随着迭代次数的增加,误码率性能会越来越好,但同时会延长每帧的处理时间或延时,也会增大译码器的复杂度,因而带来功耗的增加。同时应当指出,如果迭代次数增加一倍,延时不一定增加一倍,因为不是所有的帧译码都需要达到最大迭代次数。

3 仿真和结果分析

在Matlab环境下,对用Matlab产生的随机数进行编码后采用降低复杂度的最小和译码算法进行译码,分别仿真了不同码率在AWGN信道中对普通帧和短帧的误帧率性能的影响,最大迭代次数设置了100次,仿真结果见图2和图3,图2中FER为误帧率。从仿真结果中可以看出LDPC码在低信噪比时也能表现出很好的性能。

为了在真实的硬件环境下仿真,用定点形式表示取代了浮点形式对DVB-S2中的LDPC码的性能进行了研究。本文深入地探讨了一切可能的折衷以达到某种硬件复杂度要求。通过改变译码算法中的量化比特数和最大迭代次数来判断定点实现对性能的影响。

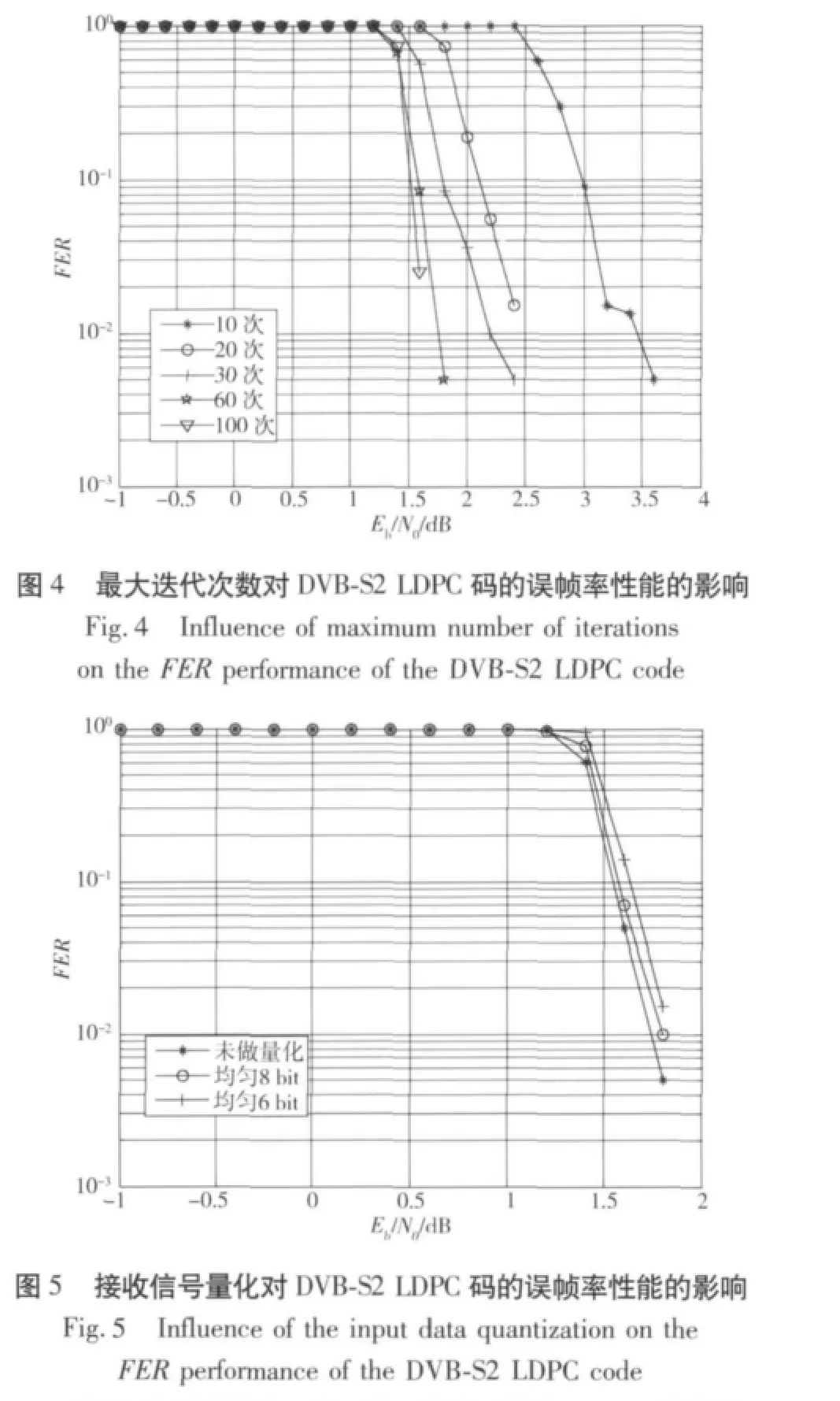

本文选取了短帧,码率为3/5的DVB-S2 LDPC码,分析了迭代次数对性能的影响。仿真结果见图4。

从仿真结果中可以看出,最大迭代次数从10次变到100次时性能有明显的改善。当从30次变到60次,误帧率为2×10-2时,性能改善了0.5 dB;当从60变到100次时,性能改善了约0.1 dB,这意味着继续增大迭代次数,性能不会有多大的改进了。从硬件实现的角度考虑,降低最大迭代次数就会使数据吞吐量和译码延时降低。

本文选取了短帧,码率为3/5的DVB-S2 LDPC码,最大迭代次数设置为60次,分别对接收信号和译码中间变量进行了量化并在Matlab下作了仿真;对接收信号量化时,选取[-4 4]的量化,量化方式为均匀量化,量化比特数分别选取了8 bit和6 bit;对译码中间变量量化时,选取[-200 200]的量化,量化方式分别选取均匀量化和非均匀(A律)量化,量化比特数选取均匀16 bit,10 bit和非均匀8 bit。仿真结果分别见图5和图6。

从仿真结果图5中可以看出,均匀8 bit量化与连续译码性能相差约0.05 dB,均匀6 bit量化相差约0.1 dB,由于增大量化比特数会增大硬件实现复杂度,所以对接收信号量化一般采用低阶6 bit均匀量化就可以取得接近连续译码的性能。从仿真结果图6中可以看出,均匀10 bit量化性能损失非常厉害,均匀16 bit量化性能与连续译码性能相差约0.05 dB,非均匀8 bit量化非常接近均匀16 bit量化的性能,但是由于非均匀(A律)量化中间计算量大,中间计算导致的精度损失过大,且硬件实现复杂度太高,所以一般不采用非均匀量化,为方便硬件实现译码中间变量的量化一般采用高阶15 bit或16 bit均匀量化就可以取得接近连续译码的性能。

图6 译码中间变量量化对DVB-S2 LDPC码的误帧率性能的影响Fig.6 Influence of the inner data quantization on the FER performance of the DVB-S2 LDPC code

假设浮点数的加减运算需要2个时钟周期,实际中可能需要更多,而定点只需一个时钟周期即可完成。从程序上分析可知,完成一次迭代节省的时钟数是

(8)式中:a表示校验矩阵中水平方向1的平均个数;b表示校验矩阵中垂直方向1的平均个数。仿真实验中也可以看到定点译码比浮点快。另外分析一下在存储空间上的优化,存储的优化主要集中在对接收数据和处理过程中数据的存储上,从算法中可知判决时的数据来源有两个,分别是接收到的数据和接收到校验节点发送的数据(中间过程的数据存储可以复用此存储区域),以均匀16 bit量化为例,假设浮点存储需要32位,则节约的存储空间为n×2×(32-16)bit=32n bit。从这里也可以看出,在性能损失允许的范围内,量化所用比特位数越少,节约的存储空间越大。

4 结论

本文从硬件实现的角度考虑,完成了针对DVBS2 LDPC码的降低复杂度的编码和译码算法实现。通过Matlab仿真,分别对普通帧和短帧的DVB-S2 LDPC码的不同码率进行了性能比较,同时还研究了不同迭代次数对性能的影响,仿真结果表明,设置最大迭代次数30次到60次之间可以在复杂度和译码性能方面取得一个很好的折衷。重点研究了量化对译码性能的影响,经仿真分析,对接收信号使用[-4 4]的低阶均匀6 bit量化,对译码中间变量使用[-200 200]的高阶16 bit均匀量化可以取得接近连续译码的性能,具有很好的实用价值。

[1]European Telecommunications Standards Institute.ETSI EN 302 307 V1.1.1(2004-06),Digital Video Broadcasting(DVB),Second generation framing structure,channel coding and modulation systems for broadcasting,Interactive Services,News Gathering and Other Broadband Satellite Applications[S].[s.l.]:[s.n.],2004.

[2]GALLAGER R G.Low density parity check codes[J].IRE Trans,On Information Theory,1962,8(01):21-28.

[3]NEAL D JC MacKay.Near shannon limit performances of low density parity check codes[J].Elect Letters,1996,32(8):1645-1646.

[4]SHAKER Sherif Welsen.DVB-S2 LDPC finite-precision decoder[C]//IEEE.IEEE ICACT 2011.Sungnam:IEEE Press,2011:1383-1386.

[5]邓炯.几种LDPC码的性能比较[J].通讯技术,2009,49(5):34-39.

DENG Jiong.Performance Comparison for Several Kinds of LDPC Codes[J].Telecommunication Engineering,2009,49(5):34-39.

[6]YANGM,RYAN W E,LIY.Design of efficiently encodable moderate-length high-rate irregular LDPC codes[J].IEEE Transactions on Communications,2004,52(4):564-571.

[7]肖扬.Turbo与LDPC编解码及其应用[M].北京:人民邮电出版社,2010:120-125.

XIAO Yang.Coding and Decoding of Turbo and LDPC and its Application[M].BeiJing:The People's Posts and Telecommunications Press.2010:120-125.

[8]FOSSORIER M,MIHALJEVIC M,LMAI H.Reduced complexity iterative decoding of low density parity codes based on belief propagation[J].IEEE Transactions on Communications,1989,47(5):673-680.

[9]BANIHASHEMIA H,ZHAO J,ZARKESHVARI F.On implementation of min-sum algorithm and its modifications for decoding LDPC codes[J].IEEE Transactions on Communications,2005,53(4):549-554.

(编辑:王敏琦)